SLVS504B - MARCH 2004 - REVISED SEPTEMBER 2015

# **TPS65012** Power and Battery Management IC for Li-Ion Powered Systems

Technical

Documents

Sample &

Buy

#### Features 1

- Linear Charger Management for Single Li-Ion or Li-Polvmer Cells

- Dual Input Ports for Charging From USB or From Wall Plug, Handles 100-mA and 500-mA USB Requirements

- Charge Current Programmable via External Resistor

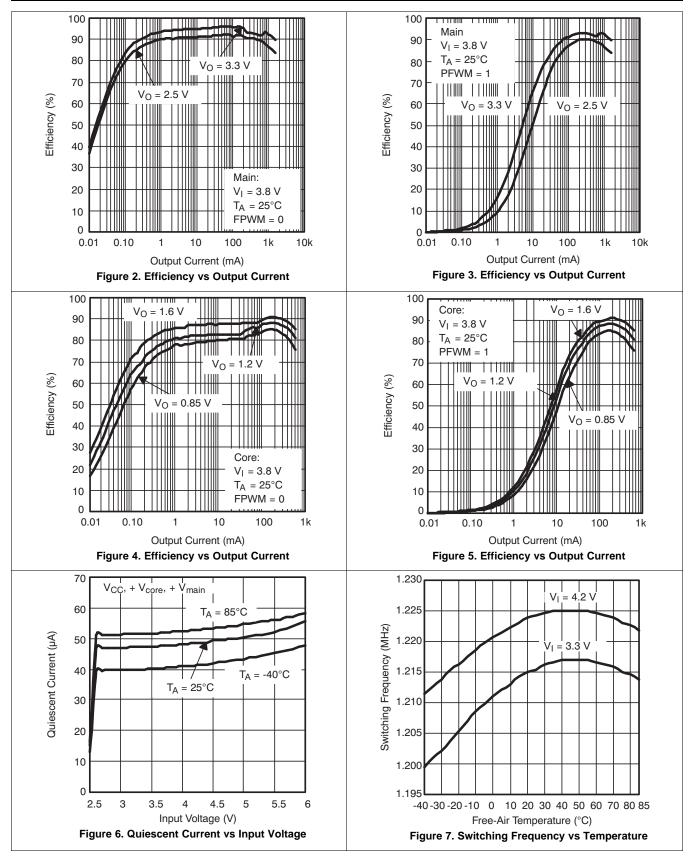

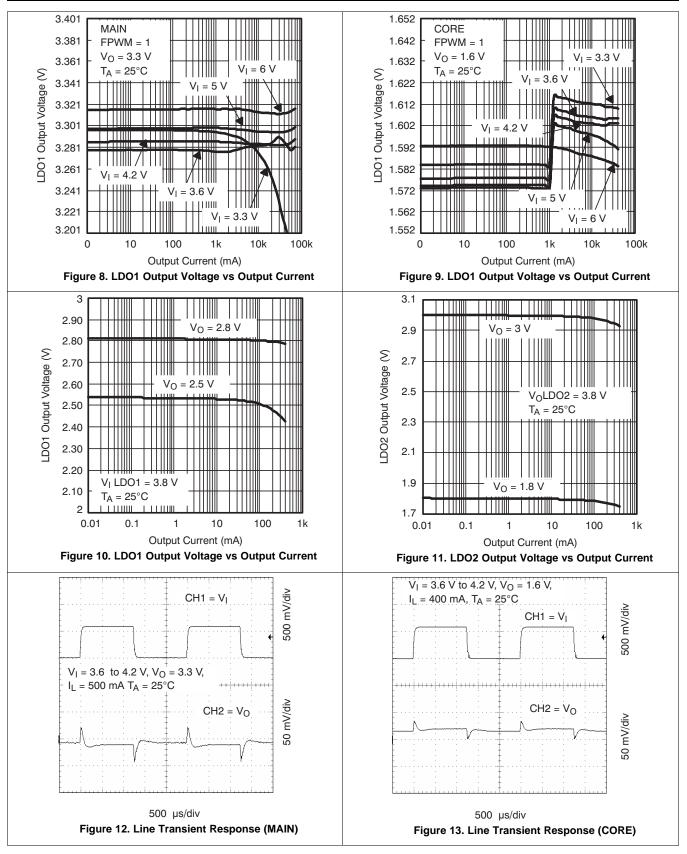

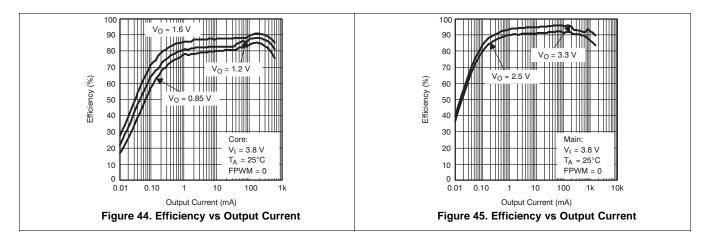

- 1-A, 95% Efficient Step-Down Converter for I/O and Peripheral Components (VMAIN)

- 400-mA, 90% Efficient Step-Down Converter for Processor Core (VCORE)

- 2x 200-mA LDOs for I/O and Peripheral Components, LDO Enable via Bus

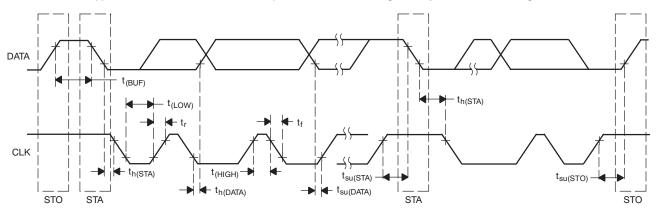

- Serial Interface Compatible With I<sup>2</sup>C, Supports 100-kHz, 400-kHz Operation

- LOW PWR Pin to Lower or Disable Processor Core Supply Voltage in Deep Sleep Mode

- 70-µA Quiescent Current

- 1% Reference Voltage

- Thermal Shutdown Protection

#### 2 Applications

- All Single Li-Ion Cell-Operated Products Requiring Multiple Supplies Including:

- PDA

- Cellular and Smart Phone

- Internet Audio Player

- Digital Still Camera

- **Digital Radio Player**

- Split Supply DSP and µP Solutions

### 3 Description

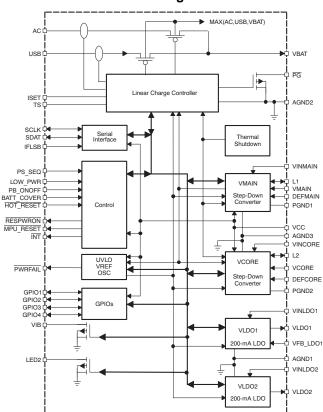

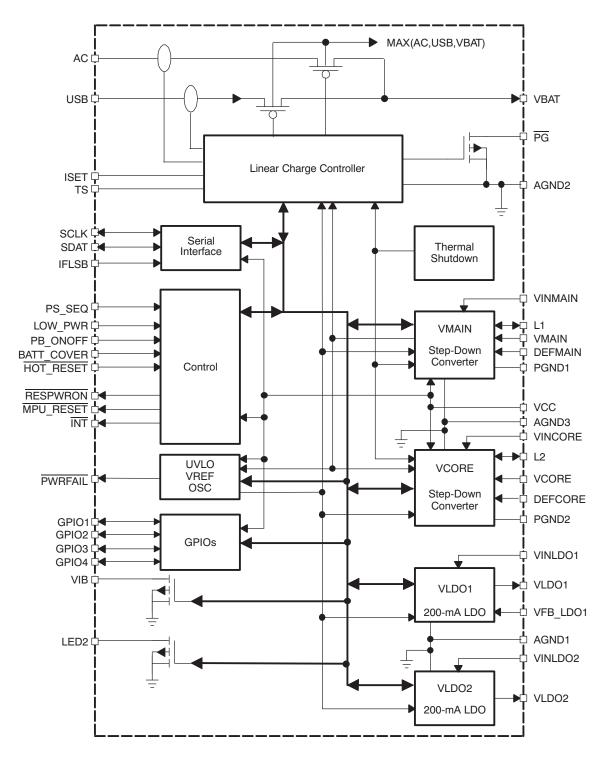

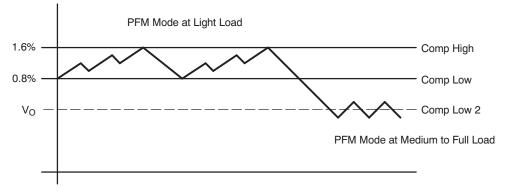

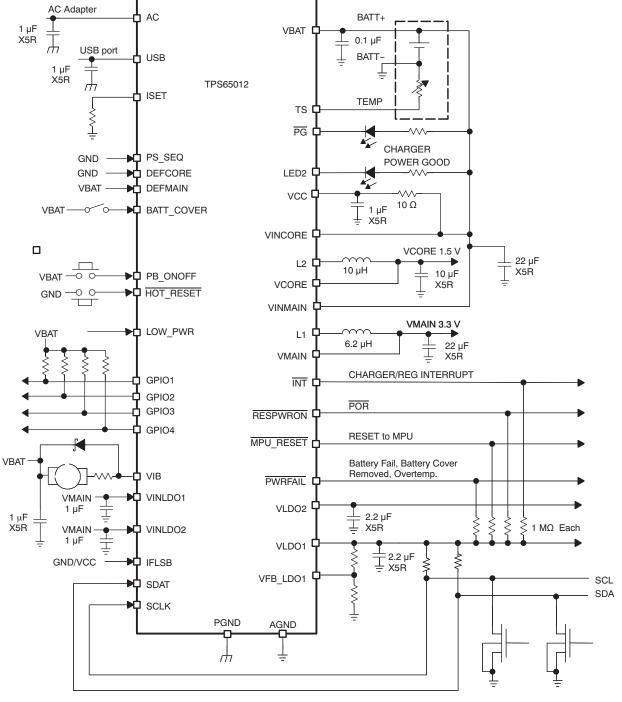

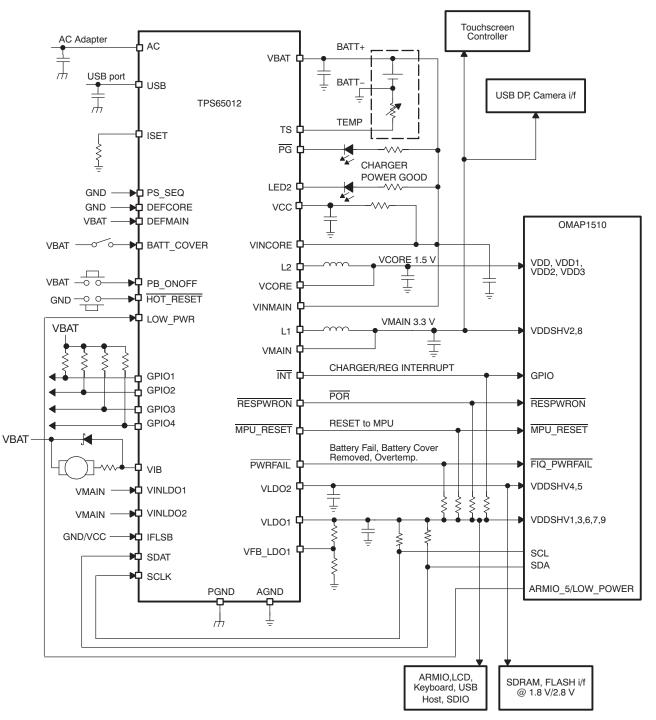

The TPS65012 device is an integrated power and battery management IC for applications powered by one Li-Ion or Li-Polymer cell and which require multiple power rails. The TPS65012 device provides two highly efficient, 1.25-MHz step down converters targeted at providing the core voltage and peripheral, I/O rails in a processor-based system. Both stepdown converters enter a low-power mode at light load for maximum efficiency across the widest possible range of load currents. The TPS65012 device also integrates two 200-mA LDO voltage regulators, which are enabled via the serial interface. Each LDO operates with an input voltage range between 1.8 V and 6.5 V, allowing them to be supplied from one of the step-down converters or directly from the battery.

The TPS65012 device has a highly integrated and flexible Li-Ion linear charger and system power management. It offers integrated USB-port and ACadapter supply management with autonomous powersource selection, power FET and current sensor, high accuracy current and voltage regulation, charge status, and charge termination.

Support &

Community

2.2

Tools &

Software

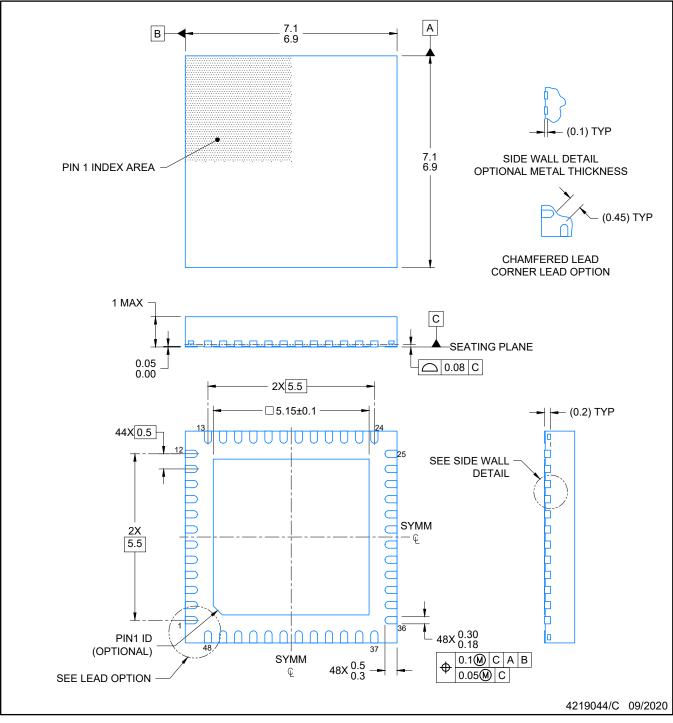

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS65012    | VQFN (48) | 7.00 mm x 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

### Block Diagram

### **TPS65012**

Features ..... 1

Applications ..... 1 Description ..... 1

Revision History..... 2

Pin Configuration and Functions ...... 3

Absolute Maximum Ratings ...... 5

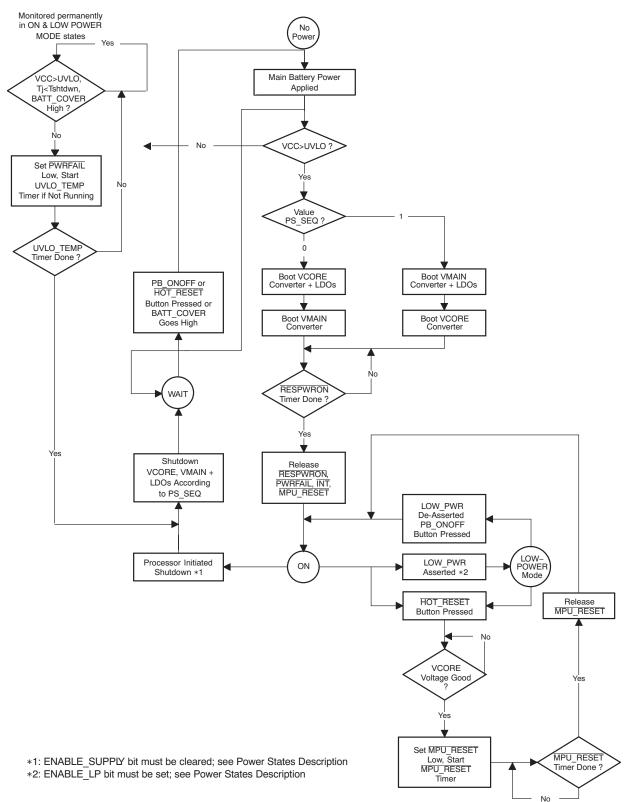

Detailed Description ..... 17 7.1 Overview ...... 17 7.2 Functional Block Diagram ...... 18

ESD Ratings......5

Recommended Operating Conditions......5

Thermal Information ...... 5 6.7 Serial Interface Timing Requirements...... 11 6.8 Dissipation Ratings ..... 11 6.9 Typical Characteristics ..... 12

1

2

3 4

5

6

7

6.1

6.2

6.3 6.4

# Table of Contents

|    | 7.3  | Feature Description               |                 |

|----|------|-----------------------------------|-----------------|

|    | 7.4  | Device Functional Modes           | 28              |

|    | 7.5  | Programming                       | 35              |

|    | 7.6  | Register Maps                     | 39              |

| 8  | Арр  | lication and Implementation       | 48              |

|    | 8.1  | Application Information           | 48              |

|    | 8.2  | Typical Applications              | 49              |

| 9  | Pow  | er Supply Recommendations         | 53              |

|    | 9.1  | LDO1 Output Voltage Adjustment    | 53              |

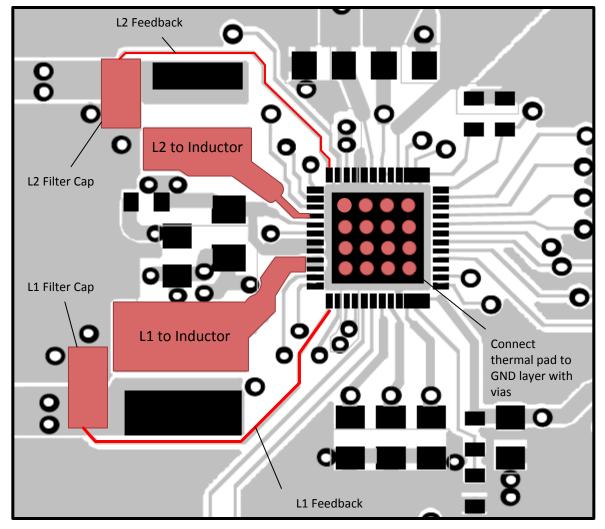

| 10 | Lay  | out                               | 53              |

|    | 10.1 | Layout Guidelines                 | 53              |

|    | 10.2 | Layout Example                    | 54              |

| 11 | Dev  | ice and Documentation Support     | 55              |

|    | 11.1 |                                   |                 |

|    | 11.2 | Trademarks                        | 55              |

|    | 11.3 | Electrostatic Discharge Caution   | 55              |

|    | 11.4 | Glossary                          | 55              |

| 12 | Mec  | hanical, Packaging, and Orderable |                 |

|    |      | rmation                           | <mark>55</mark> |

|    |      |                                   |                 |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision A (January 2005) to Revision B

Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device

www.ti.com

### 5 Pin Configuration and Functions

NC - No internal connection

#### **Pin Functions**

| PIN                 |            |     |                                                                                                                                                                                                 |

|---------------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | NO.        | I/O | DESCRIPTION                                                                                                                                                                                     |

| CHARGER SECTION     |            |     |                                                                                                                                                                                                 |

| AC                  | 40         | I   | Charger input voltage from AC adapter. The AC pin can be left open or can be connected to ground if the charger is not used.                                                                    |

| AGND2               | 44         |     | Analog ground connection. All analog ground pins are connected internally on the chip.                                                                                                          |

| ISET                | 37         | I   | External charge current setting resistor connection for use with AC adapter                                                                                                                     |

| NC                  | 27         |     | Connect this pin to GND.                                                                                                                                                                        |

| PG                  | 11         | 0   | Indicates when a valid power supply is present for the charger (open drain)                                                                                                                     |

| Thernal Pad         | -          |     | Connect the thermal pad to GND                                                                                                                                                                  |

| TS                  | 38         | I   | Battery temperature sense input                                                                                                                                                                 |

| USB                 | 43         | I   | Charger input voltage from USB port. The USB pin can be left open or can be connected to ground if the charger is not used.                                                                     |

| VBAT_A              | 41         | I   | Sense input for the battery voltage. Connect directly with the battery.                                                                                                                         |

| VBAT_B              | 42         | 0   | Power output of the battery charger. Connect directly with the battery.                                                                                                                         |

| SWITCHING REGULA    | TOR SECTIO | N   |                                                                                                                                                                                                 |

| AGND3               | 45         |     | Analog ground connection. All analog ground pins are connected internally on the chip.                                                                                                          |

| L1_A, L1_B          | 9,10       |     | Switch pin of VMAIN converter. The VMAIN inductor is connected here.                                                                                                                            |

| L2                  | 4          |     | Switch pin of VCORE converter. The VCORE inductor is connected here.                                                                                                                            |

| PGND1_A,<br>PGND1_B | 15,16      |     | Power ground for VMAIN converter                                                                                                                                                                |

| PGND2               | 46         |     | Power ground for VCORE converter                                                                                                                                                                |

| VCC                 | 6          | I   | Power supply for digital and analog circuitry of MAIN and CORE DC-DC converters. This must be connected to the same voltage supply as VINCORE and VINMAIN. Also supplies serial interface block |

| VCORE               | 48         | I   | VCORE feedback voltage sense input, connect directly to VCORE                                                                                                                                   |

**TPS65012** SLVS504B – MARCH 2004 – REVISED SEPTEMBER 2015

www.ti.com

NSTRUMENTS

Texas

### Pin Functions (continued)

| PIN                     |        |     |                                                                                                                                                                                                                        |

|-------------------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                    | NO.    | I/O | DESCRIPTION                                                                                                                                                                                                            |

| VINCORE                 | 5      | I   | Input voltage for VCORE step-down converter. This must be connected to the same voltage supply as VINMAIN and VCC.                                                                                                     |

| VINMAIN_A,<br>VINMAIN_B | 7,8    | I   | Input voltage for VMAIN step-down converter. This must be connected to the same voltage supply as VINCORE and VCC.                                                                                                     |

| VMAIN                   | 13     | I   | VMAIN feedback voltage sense input, connect directly to VMAIN                                                                                                                                                          |

| LDO REGULATOR SE        | CTION  |     |                                                                                                                                                                                                                        |

| AGND1                   | 21     |     | Analog ground connection. All analog ground pins are connected internally on the chip.                                                                                                                                 |

| VFB_LDO1                | 23     | I   | Feedback input from external resistive divider for LDO1                                                                                                                                                                |

| VINLDO1                 | 22     | I   | Input voltage for LDO1                                                                                                                                                                                                 |

| VINLDO2                 | 19     | I   | Input voltage for LDO2                                                                                                                                                                                                 |

| VLDO1                   | 24     | 0   | Output voltage for LDO1                                                                                                                                                                                                |

| VLDO2                   | 20     | 0   | Output and feedback voltage for LDO2                                                                                                                                                                                   |

| DRIVER SECTION          |        |     |                                                                                                                                                                                                                        |

| LED2                    | 2      | 0   | LED driver, with blink rate programmable via serial interface                                                                                                                                                          |

| VIB                     | 3      | 0   | Vibrator driver, enabled via serial interface                                                                                                                                                                          |

| CONTROL AND I2C SI      | ECTION |     |                                                                                                                                                                                                                        |

| BATT_COVER              | 39     | I   | Indicates if battery cover is in place                                                                                                                                                                                 |

| DEFCORE                 | 1      | I   | Input signal indicating default VCORE voltage, 0 = 1.5 V, 1 = 1.6 V                                                                                                                                                    |

| DEFMAIN                 | 12     | I   | Input signal indicating default VMAIN voltage, 0 = 3.0 V, 1 = 3.3 V                                                                                                                                                    |

| GPIO1                   | 26     | I/O | General-purpose open-drain input/output                                                                                                                                                                                |

| GPIO2                   | 25     | I/O | General-purpose open-drain input/output                                                                                                                                                                                |

| GPIO3                   | 18     | I/O | General-purpose open-drain input/output                                                                                                                                                                                |

| GPIO4                   | 17     | I/O | General-purpose open-drain input/output                                                                                                                                                                                |

| HOT_RESET               | 31     | I   | Push-button reset input used to reboot or wakeup processor via TPS65012                                                                                                                                                |

| IFLSB                   | 28     | I   | LSB of serial interface address used to distinguish two devices with the same address                                                                                                                                  |

| INT                     | 35     | 0   | Indicates a charge fault or termination, or if any of the regulator outputs are below the lower tolerance level, active low (open drain)                                                                               |

| LOW_PWR                 | 36     | I   | Input signal indicating deep sleep mode, VCORE is lowered to predefined value or disabled                                                                                                                              |

| MPU_RESET               | 32     | 0   | Open-drain reset output generated by user activated HOT_RESET                                                                                                                                                          |

| PB_ONOFF                | 47     | I   | Push-button enable pin, also used to wakeup processor from low-power mode                                                                                                                                              |

| PS_SEQ                  | 14     | I   | Sets power-up/down sequence of step-down converters                                                                                                                                                                    |

| PWRFAIL                 | 34     | 0   | Open-drain output. Active low when UVLO comparator indicates low VBAT condition or when shutdown is about to occur due to an overtemperature condition or when the battery cover is removed (BATT_COVER has gone low). |

| RESPWRON                | 33     | 0   | Open-drain system reset output, generated according to the state of the LDO1 output voltage.                                                                                                                           |

| SCLK                    | 30     | I   | Serial interface clock line                                                                                                                                                                                            |

| SDAT                    | 29     | I/O | Serial interface data/address                                                                                                                                                                                          |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                                                  | MIN  | MAX              | UNIT |

|----------------------------------------------------------------------------------|------|------------------|------|

| Input voltage on VAC pin with respect to AGND                                    |      | 20               | V    |

| Input voltage range on all other pins except AGND/PGND pins with respect to AGND | -0.3 | 7                | V    |

| HBM and CBM capabilities at pins VIB, PG, and LED2                               |      | 1                | kV   |

| Current at AC, VBAT, VINMAIN, L1, PGND1                                          |      | 1800             | mA   |

| Peak current at all other pins                                                   |      | 1000             | mA   |

| Continuous power dissipation                                                     |      | sipation<br>ings |      |

| Operating free-air temperature, T <sub>A</sub>                                   | -40  | 85               | °C   |

| Maximum junction temperature, T <sub>J</sub>                                     |      | 125              | °C   |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                     |      | 260              | °C   |

| Storage temperature range ,T <sub>stg</sub>                                      | -65  | 150              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>       | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(2)}$ | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

|                                                             |                                                   | MIN | NOM MAX | UNIT |

|-------------------------------------------------------------|---------------------------------------------------|-----|---------|------|

| V <sub>(AC)</sub>                                           | Supply voltage from AC adapter                    | 4.5 | 5.5     | V    |

| V <sub>(USB)</sub>                                          | Supply voltage from USB                           | 4.4 | 5.25    | V    |

| V <sub>I(MAIN)</sub> ,V <sub>I(CORE)</sub> ,V <sub>CC</sub> | Input voltage range step-down converters          | 2.5 | 6.0     | V    |

| V <sub>O(MAIN)</sub>                                        | Output voltage range for main step-down convertor | 2.5 | 3.3     | V    |

| V <sub>I(LDO1)</sub> , V <sub>I(LDO2)</sub>                 | Input voltage range for LDOs                      | 1.8 | 6.5     | V    |

| T <sub>A</sub>                                              | Operating ambient temperature range               | -40 | 85      | °C   |

| TJ                                                          | Operating junction temperature range              | -40 | 125     | °C   |

### 6.4 Thermal Information

|                       |                                              | TPS65012   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGZ (VQFN) | UNIT |

|                       |                                              | 48 PIN     |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 27.0       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 14.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 4.6        | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.2        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 4.6        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1        | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, SPRA953.

SLVS504B-MARCH 2004-REVISED SEPTEMBER 2015

www.ti.com

### 6.5 Electrical Characteristics

$V_{I(MAIN)} = V_{I(CORE)} = V_{CC} = V_{I(LDO1)} = V_{I(LDO2)} = 3.6 \text{ V}, \text{ } \text{T}_{\text{A}} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}, \text{ typical values are at } \text{T}_{\text{A}} = 25^{\circ}\text{C} \text{ battery charger specifications are valid in the range } 0^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C} \text{ unless otherwise noted}$

|                           | PARAMETER                                                                                                           | TEST CONDITIONS                                                         | MIN                 | TYP  | MAX             | UNIT |

|---------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|------|-----------------|------|

| CONTROL SI                | GNALS: LOW_PWR, SCLK, SDAT (INPUT)                                                                                  |                                                                         |                     |      |                 |      |

| V <sub>IH</sub>           | High level input voltage                                                                                            | $I_{IH} = 20 \ \mu A^{(1)}$                                             | 2                   |      | V <sub>CC</sub> | V    |

| V <sub>IL</sub>           | Low level input voltage                                                                                             | I <sub>IL</sub> = 10 μA                                                 | 0                   |      | 0.8             | V    |

| IB                        | Input bias current                                                                                                  |                                                                         |                     | 0.01 | 1.0             | μA   |

| CONTROL SI                | GNALS: PB_ONOFF, HOT_RESET, BATT_C                                                                                  | OVER                                                                    |                     |      | 1               |      |

| VIH                       | High level input voltage                                                                                            | I <sub>IH</sub> = 20 μA <sup>(1)</sup>                                  | 0.8 V <sub>CC</sub> |      | 6               | V    |

| V <sub>IL</sub>           | Low level input voltage                                                                                             | I <sub>IL</sub> = 10 μA                                                 | 0                   |      | 0.4             | V    |

| R <sub>(pb_onoff)</sub>   | Pulldown resistor at PB_ONOFF                                                                                       |                                                                         |                     | 1000 |                 | kΩ   |

| R <sub>(hot_reset)</sub>  | Pullup resistor at HOT_RESET, connected to VCC                                                                      |                                                                         |                     | 1000 |                 | kΩ   |

| R(batt_cover)             | Pulldown resistor at BATT_COVER                                                                                     |                                                                         |                     | 2000 |                 | kΩ   |

| t(glitch)                 | De-glitch time at all 3 pins                                                                                        |                                                                         | 38                  | 56   | 77              | ms   |

| t <sub>(batt_cover)</sub> | Delay after t <sub>(glitch)</sub> (PWRFAIL goes low)<br>before supplies are disabled when<br>BATT_COVER goes low.   |                                                                         | 1.68                | 2.4  | 3.2             | ms   |

| CONTROL SIG               | GNALS: MPU_RESET, PWRFAIL, RESPWR                                                                                   | ON, INT, SDAT (OUTPUT)                                                  |                     |      |                 |      |

| V <sub>OH</sub>           | High level output voltage                                                                                           |                                                                         |                     |      | 6               | V    |

| V <sub>OL</sub>           | Low level output voltage                                                                                            | I <sub>IL</sub> = 10 mA                                                 | 0                   |      | 0.3             | V    |

| td(mpu_nreset)            | Duration of low pulse at MPU_RESET                                                                                  |                                                                         | 100                 |      |                 | μs   |

| d(nrespwron)              | Duration of low pulse at RESPWRON                                                                                   | CHGCONFIG<7> = 0 (Default)                                              | 800                 | 1000 | 1200            |      |

|                           | after VLDO1 is in regulation                                                                                        | CHGCONFIG<7> = 1                                                        | 49                  | 69   | 89              | ms   |

| t <sub>d(uvlo)</sub>      | Time between UVLO going active<br>(PWRFAIL going low) and supplies being<br>disabled                                |                                                                         | 1.68                | 2.4  | 3.2             | ms   |

| t <sub>d(overtemp)</sub>  | Time between chip over-temperature<br>condition being recognized (PWRFAIL<br>going low) and supplies being disabled |                                                                         | 1.68                | 2.4  | 3.2             | ms   |

| SUPPLY PIN:               | VCC                                                                                                                 | · · · ·                                                                 |                     |      |                 |      |

| I <sub>(Q)</sub>          | Operating quiescent current                                                                                         | $V_I = 3.6 V$ , current into Main + Core + $V_{CC}$                     |                     |      | 58              | μA   |

| I <sub>O(SD)</sub>        | Shutdown supply current                                                                                             | $V_I$ = 3.6 V, BATT_COVER = GND,<br>Current into Main + Core + $V_{CC}$ |                     | 15   | 25              | μA   |

| VMAIN STEP-               | DOWN CONVERTER                                                                                                      |                                                                         |                     |      |                 |      |

| VI                        | Input voltage range                                                                                                 |                                                                         | 2.5                 |      | 6.0             | V    |

| 0                         | Maximum output current                                                                                              |                                                                         | 1000                |      |                 | mA   |

| O(SD)                     | Shutdown supply current                                                                                             | BATT_COVER = GND                                                        |                     | 0.1  | 1               | μA   |

| DS(on)                    | P-channel MOSFET on-resistance                                                                                      | $V_{I(MAIN)} = V_{GS} = 3.6 V$                                          |                     | 110  | 210             | mΩ   |

| lkg(p)                    | P-channel leakage current                                                                                           | V <sub>(DS)</sub> = 6.0 V                                               |                     |      | 1               | μA   |

| DS(on)                    | N-channel MOSFET on-resistance                                                                                      | $V_{I(MAIN)} = V_{GS} = 3.6 V$                                          |                     | 110  | 200             | mΩ   |

| lkg(N)                    | N-channel leakage current                                                                                           | V <sub>(DS)</sub> = 6.0 V                                               |                     |      | 1               | μA   |

| IL                        | P-channel current limit                                                                                             | 2.5 V< V <sub>I(MAIN)</sub> < 6.0 V                                     | 1.4                 | 1.75 | 2.1             | A    |

| fs                        | Oscillator frequency                                                                                                |                                                                         | 1                   | 1.25 | 1.5             | MHz  |

(1) If the input voltage is higher than  $V_{CC}$ , an additional input current, limited by an internal 10-k $\Omega$  resister, flows.

### **Electrical Characteristics (continued)**

$V_{I(MAIN)} = V_{I(CORE)} = V_{CC} = V_{I(LDO1)} = V_{I(LDO2)} = 3.6 \text{ V}, \text{ } \text{T}_{\text{A}} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}, \text{ typical values are at } \text{T}_{\text{A}} = 25^{\circ}\text{C} \text{ battery charger specifications are valid in the range } 0^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C} \text{ unless otherwise noted}$

|                      | PARAMETER                 |          | TEST CONDITIONS                                                                                            | MIN | TYP  | MAX | UNIT |

|----------------------|---------------------------|----------|------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                      |                           |          | $V_{I(MAIN)} = 2.7 \text{ V to } 6.0 \text{ V}; I_0 = 0 \text{ mA}$                                        | 0%  |      | 3%  |      |

|                      |                           | 2.5 V    | $V_{I(MAIN)} = 2.7 \text{ V to } 6.0 \text{ V};$<br>0 mA ≤ I <sub>O</sub> ≤ 1000 mA                        | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(MAIN)} = 2.95 \text{ V to } 6.0 \text{ V; } I_0 = 0 \text{ mA}$                                      | 0%  |      | 3%  |      |

|                      |                           | 2.75 V   | $V_{I(MAIN)} = 2.95 \text{ V to 6.0 V;}$<br>0 mA ≤ I <sub>O</sub> ≤ 1000 mA                                | 3%  |      | 3%  |      |

| V <sub>O(MAIN)</sub> | Fixed output voltage      |          | $V_{I(MAIN)} = 3.2 \text{ V to } 6.0 \text{ V}; \text{ I}_{O} = 0 \text{ mA}$                              | 0%  |      | 3%  |      |

|                      |                           | 3.0 V    | $V_{I(MAIN)} = 3.2 \text{ V to } 6.0 \text{ V};$<br>0 mA ≤ I <sub>O</sub> ≤ 1000 mA                        | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(MAIN)} = 3.5 \text{ V to } 6.0 \text{ V}; I_0 = 0 \text{ mA}$                                        | 0%  |      | 3%  |      |

|                      |                           | 3.3 V    | $V_{I(MAIN)} = 3.5 V \text{ to } 6.0 V;$<br>0 mA ≤ I <sub>0</sub> ≤ 1000 mA                                | 3%  |      | 3%  |      |

|                      | Line regulation           |          | $V_{I(MAIN)} = V_{O(MAIN)} + 0.5 V (min. 2.5 V)$<br>to 6.0 V, I <sub>O</sub> = 10 mA                       |     | 0.5  |     | %/V  |

|                      | Load regulation           |          | I <sub>O</sub> = 10 mA to 1000 mA                                                                          |     | 0.12 |     | %/A  |

| R <sub>(VMAIN)</sub> | VMAIN discharge resistant | се       |                                                                                                            |     | 400  |     | Ω    |

| . ,                  | P-DOWN CONVERTER          |          | ·                                                                                                          |     |      |     |      |

| VI                   | Input voltage range       |          |                                                                                                            | 2.5 |      | 6.0 | V    |

| I <sub>0</sub>       | Maximum output current    |          |                                                                                                            | 400 |      |     | mA   |

| O(SD)                | Shutdown supply current   |          | BATT_COVER = GND                                                                                           |     | 0.1  | 1   | μA   |

| DS(on)               | P-channel MOSFET on-res   | sistance | $V_{I(CORE)} = V_{GS} = 3.6 \text{ V}$                                                                     |     | 275  | 530 | mΩ   |

| l <sub>lkg(p)</sub>  | P-channel leakage current |          | $V_{\rm DS} = 6.0 \text{ V}$                                                                               |     | 0.1  | 1   | μA   |

| r <sub>DS(on)</sub>  | N-channel MOSFET on-re    |          | $V_{I(CORE)} = V_{GS} = 3.6 V$                                                                             |     | 275  | 500 | mΩ   |

| lkg(N)               | N-channel leakage current |          | $V_{\rm DS} = 6.0 \text{ V}$                                                                               |     | 0.1  | 1   | μA   |

| L                    | P-channel current limit   |          | 2.5 V< V <sub>I(CORE)</sub> < 6.0 V                                                                        | 600 | 700  | 900 | mA   |

| s                    | Oscillator frequency      |          |                                                                                                            | 1   | 1.25 | 1.5 | MHz  |

| 3                    |                           |          | $V_{I(CORE)} = 2.5 V \text{ to } 6.0 V;$<br>$I_{O} = 0 \text{ mA}, C_{O} = 22 \mu \text{F}$                | 0%  |      | 3%  |      |

|                      |                           | 0.85 V   | $V_{I(CORE)} = 2.5 \text{ V to } 6.0 \text{ V};$<br>0 mA ≤ I <sub>0</sub> ≤ 400 mA, C <sub>0</sub> = 22 µF | 3%  |      | 3%  |      |

|                      |                           | 1.0 V    |                                                                                                            | 0%  |      | 3%  |      |

|                      |                           | 1.0 V    |                                                                                                            | 3%  |      | 3%  |      |

|                      |                           | 1.1 V    |                                                                                                            | 0%  |      | 3%  |      |

|                      |                           |          |                                                                                                            | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(CORE)}$ = 2.5 V to 6.0 V; $I_O$ = 0 mA                                                               | 0%  |      | 3%  |      |

| V <sub>O(CORE)</sub> | Fixed output voltage      | 1.2 V    | $V_{I(CORE)}$ = 2.5 V to 6.0 V;<br>0 mA ≤ I <sub>O</sub> ≤ 400 mA                                          | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(CORE)}$ = 2.5 V to 6.0 V; $I_{O}$ = 0 mA                                                             | 0%  |      | 3%  |      |

|                      |                           | 1.3 V    | $V_{I(CORE)}$ = 2.5 V to 6.0 V;<br>0 mA ≤ I <sub>O</sub> ≤ 400 mA                                          | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(CORE)}$ = 2.5 V to 6.0 V; $I_{O}$ = 0 mA                                                             | 0%  |      | 3%  |      |

|                      |                           | 1.4 V    | $V_{I(CORE)}$ = 2.5 V to 6.0 V;<br>0 mA ≤ I <sub>O</sub> ≤ 400 mA                                          | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(CORE)}$ = 2.5 V to 6.0 V; $I_O$ = 0 mA                                                               | 0%  |      | 3%  |      |

|                      |                           | 1.5 V    | $V_{I(CORE)} = 2.5 \text{ V to } 6.0 \text{ V};$<br>0 mA ≤ I <sub>O</sub> ≤ 400 mA                         | 3%  |      | 3%  |      |

|                      |                           |          | $V_{I(CORE)} = 2.5 \text{ V to } 6.0 \text{ V; } I_{O} = 0 \text{ mA}$                                     | 0%  |      | 3%  |      |

|                      |                           | 1.6 V    | $V_{I(CORE)} = 2.5 \text{ V to 6.0 V;}$<br>0 mA ≤ I <sub>O</sub> ≤ 400 mA                                  | 3%  |      | 3%  |      |

|                      | Line regulation           |          | $V_{I(CORE)} = V_{O(MAIN)} + 0.5 V$<br>(min. 2.5 V) to 6.00 V, I <sub>O</sub> = 10 mA                      |     | 1    |     | %/V  |

Copyright © 2004–2015, Texas Instruments Incorporated

XAS STRUMENTS

www.ti.com

## **Electrical Characteristics (continued)**

$V_{I(MAIN)} = V_{I(CORE)} = V_{CC} = V_{I(LDO1)} = V_{I(LDO2)} = 3.6 \text{ V}, \text{ } \text{T}_{\text{A}} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}, \text{ typical values are at } \text{T}_{\text{A}} = 25^{\circ}\text{C} \text{ battery charger specifications are valid in the range } 0^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C} \text{ unless otherwise noted}$

|                      | PARAMETER                                 | TEST CONDITIONS                                                              | MIN | TYP   | MAX     | UNIT |

|----------------------|-------------------------------------------|------------------------------------------------------------------------------|-----|-------|---------|------|

|                      | Load regulation                           | $I_{O} = 10 \text{ mA to } 400 \text{ mA}$                                   |     | 0.002 |         | %/mA |

| R <sub>(VCORE)</sub> | VCORE discharge resistance                |                                                                              |     | 400   |         | Ω    |

|                      | VLDO2 LOW-DROPOUT REGULATORS              |                                                                              |     |       |         |      |

| VI                   | Input voltage range                       |                                                                              | 1.8 |       | 6.5     | V    |

| Vo                   | LDO1 output voltage range                 |                                                                              | 0.9 |       | VINLDO1 | V    |

| V <sub>ref</sub>     | Reference voltage                         |                                                                              | 485 | 500   | 515     | mV   |

| Vo                   | LDO2 output voltage range                 |                                                                              | 1.8 |       | 3.0     | V    |

|                      | Manimum and a surger                      | Full-power mode                                                              | 200 |       |         | 0    |

| I <sub>O</sub>       | Maximum output current                    | Low-power mode                                                               | 30  |       |         | mA   |

| I <sub>(SC)</sub>    | LDO1 and LDO2 short-circuit current limit | VLDO1 = GND, VLDO2 = GND                                                     |     |       | 600     | mA   |

|                      | Dropout voltage                           | I <sub>O</sub> = 200 mA, VINLDO1,2 = 1.8 V                                   |     |       | 300     | mV   |

|                      | Total accuracy                            |                                                                              |     |       | ±3%     |      |

|                      | Line regulation                           | VINLDO1,2 = VLDO1,2 + 0.5 V<br>(min. 2.5 V) to 6.5 V, I <sub>O</sub> = 10 mA |     | 0.75  |         | %/V  |

|                      | Load regulation                           | $I_0 = 10 \text{ mA to } 200 \text{ mA}$                                     |     | 0.011 |         | %/mA |

|                      | Regulation time                           | Load change from 10% to 90%                                                  |     |       | 0.1     | ms   |

|                      |                                           | Low-power mode                                                               |     | 0.1   |         | ms   |

| I <sub>(QFP)</sub>   | LDO quiescent current (each LDO)          | Full-power mode                                                              |     | 16    | 30      | μΑ   |

| I <sub>(QLPM)</sub>  | LDO quiescent current (each LDO)          | Low-power mode                                                               |     | 12    | 18      | μΑ   |

| I <sub>O(SD)</sub>   | LDO shutdown current (each LDO)           |                                                                              |     | 0.1   | 1       | μΑ   |

| I <sub>lkg(FB)</sub> | Leakage current feedback                  |                                                                              |     | 0.01  | 0.1     | μA   |

### 6.6 Battery Charger Electrical Characteristics

$\underline{V_{O(REG)} + V_{(DO-MAX)} \leq V_{(CHG)} = V_{(AC)} \text{ or } V_{(USB)}, \text{ } I_{(TERM)} < I_O \leq 1 \text{ A}, \text{ } 0^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$

|                       | PARAMETER                                            | TEST CONDITIONS                                                                                                                          | MIN  | TYP  | MAX  | UNIT |

|-----------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>(AC)</sub>     | Input voltage range                                  |                                                                                                                                          | 4.5  |      | 5.5  | V    |

| V <sub>(USB)</sub>    | Input voltage range                                  |                                                                                                                                          | 4.35 |      | 5.25 | V    |

| I <sub>CC(VCHG)</sub> | Supply current                                       | $V_{(CHG)} > V_{(CHG)}$ min                                                                                                              |      | 1.2  | 2    | mA   |

| I <sub>CC(SLP)</sub>  | Sleep current                                        | Sum of currents into VBAT pin,<br>$V_{(CHG)} < V_{(SLP-ENTRY)},$<br>$0^{\circ}C \le T_{J} \le 85^{\circ}C$                               |      | 2    | 5    | μΑ   |

|                       | 0                                                    | Current into USB pin                                                                                                                     |      |      | 45   | μA   |

| I <sub>CC(STBY)</sub> | Standby current                                      | Current into AC pin                                                                                                                      |      | 200  | 400  |      |

| VOLTAGE R             | EGULATOR                                             |                                                                                                                                          |      |      |      |      |

| Vo                    | Output voltage                                       | V <sub>(CHG)</sub> min ≥ 4.5 V                                                                                                           | 4.15 | 4.20 | 4.25 | V    |

|                       | Dropout voltage (V <sub>(AC)</sub> - VBAT)           | $\label{eq:VO(REG)} \begin{split} V_{O(REG)} + V_{(DO-MAX)} &\leq V_{(CHG)}, \\ I_{O(OUT)} &= 1 \ A \end{split}$                         |      | 500  | 800  | mV   |

| V <sub>DO</sub>       | Dropout voltage (V <sub>(USB)</sub> - VBAT)          | $\label{eq:VO(REG)} \begin{split} V_{O(REG)} + V_{(DO-MAX)} &\leq V_{(CHG)}, \\ I_{O(OUT)} &= 0.5 ~A \end{split}$                        |      | 300  | 500  | mV   |

|                       | Dropout voltage (V <sub>(USB)</sub> - VBAT)          | $\label{eq:VO(REG)} \begin{split} V_{O(REG)} + V_{(DO-MAX)} &\leq V_{(CHG)}, \\ I_{O(OUT)} &= 0.1 \ A \end{split}$                       |      | 100  | 150  | mV   |

| CURRENT R             | EGULATION                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                    |      |      |      |      |

| I <sub>O(AC)</sub>    | Output current range for AC operation <sup>(1)</sup> | $\label{eq:V_CHG} \begin{array}{l} V_{CHG} \geq 4.5 \ V, \ V_{I(OUT)} > V_{(LOWV)}, \\ V_{(AC)} - V_{I(BAT)} > V_{(DO-MAX)} \end{array}$ | 100  |      | 1000 | mA   |

$\mathsf{KSET} \times \mathsf{V}_{(\mathsf{SET})}$ I<sub>O(AC)</sub> R<sub>(ISET)</sub>

8 Submit Documentation Feedback

### **Battery Charger Electrical Characteristics (continued)**

|                     | PARAMETER                                                                                                                        | TEST CONDITIONS                                                                                                                                                                      | MIN                            | TYP                          | MAX                            | UNIT |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|--------------------------------|------|

|                     | Output current set voltage for AC operation at<br>ISET pin. 100% output current I <sup>2</sup> C register<br>CHGCONFIG<4:3> = 11 |                                                                                                                                                                                      | 2.45                           | 2.50                         | 2.55                           | V    |

| / <sub>(SET)</sub>  | 75% output current I <sup>2</sup> C register<br>CHGCONFIG<4:3> = 10                                                              | $V_{min} \ge 4.5 \text{ V}, V_{I(BAT)} > V_{(LOWV)}, V_{(AC)}$ -                                                                                                                     | 1.83                           | 1.91                         | 1.99                           | V    |

| ()                  | 50% output current I <sup>2</sup> C register<br>CHGCONFIG<4:3> = 01                                                              | - V <sub>I(BAT)</sub> > V <sub>(DO-MAX)</sub>                                                                                                                                        | 1.23                           | 1.31                         | 1.39                           | V    |

|                     | 32% output current I <sup>2</sup> C register<br>CHGCONFIG<4:3> = 00                                                              |                                                                                                                                                                                      | 0.76                           | 0.81                         | 0.86                           | V    |

| (0FT                |                                                                                                                                  | 100 mA < I <sub>O</sub> < 1000 mA                                                                                                                                                    | 310                            | 330                          | 350                            |      |

| SET                 | Output current set factor for AC operation                                                                                       | 10 mA < I <sub>O</sub> < 100 mA                                                                                                                                                      | 300                            | 340                          | 380                            |      |

|                     | Output output rooms for LISP operation                                                                                           | $ \begin{array}{l} V_{(CHG)} \mbox{ min } \geq 4.35 \ V, \ V_{I(BAT)} > \\ V_{(LOWV)}, \ V_{(USB)} - V_{I(BAT)} > V_{(DO-MAX)}, \\ I^2 C \ register \ CHGCONFIG<2> = 0 \end{array} $ | 80                             |                              | 100                            | mA   |

| O(USB)              | Output current range for USB operation                                                                                           | $ \begin{array}{l} V_{(CHG)} \mbox{ min } \geq 4.5 \ V, \ V_{I(BAT)} > V_{(LOWV)}, \\ V_{USB} - V_{I(BAT)} > V_{(DO-MAX)}, \\ I^2 C \ register \ CHGCONFIG<2> = 1 \end{array} $      | 400                            |                              | 500                            | mA   |

| R <sub>(ISET)</sub> | Resistor range at ISET pin                                                                                                       |                                                                                                                                                                                      | 825                            |                              | 8250                           | Ω    |

| RECHARGE            | CURRENT REGULATION, SHORT-CIRCUIT CURR                                                                                           | ENT, AND BATTERY DETECTION CUR                                                                                                                                                       | RENT                           |                              |                                |      |

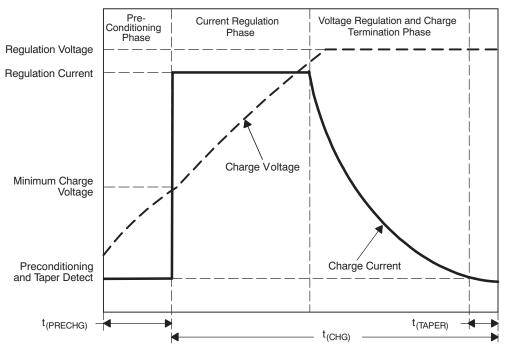

| (LOWV)              | Precharge to fast-charge transition threshold, voltage on VBAT pin.                                                              | $V_{(CHG)}$ min ≥ 4.5 V                                                                                                                                                              | 2.8                            | 3.0                          | 3.2                            | V    |

|                     | De-glitch time                                                                                                                   | $V_{(CHG)}$ min ≥ 4.5 V, $V_{I(OUT)}$<br>decreasing below threshold; 100-ns fall time, 10-mV overdrive                                                                               | 250                            | 375                          | 500                            | ms   |

| (PRECHG)            | Precharge current <sup>(2)</sup>                                                                                                 | $0 \le V_{I(OUT)} < V_{(LOWV)}, t < t_{(PRECHG)}$                                                                                                                                    | 10                             |                              | 100                            | mA   |

| (DETECT)            | Battery detection current                                                                                                        |                                                                                                                                                                                      |                                | 200                          |                                | μA   |

| V(SET-PRECHG)       | Voltage at ISET pin                                                                                                              | $0 \le V_{I(OUT)} < V_{(LOWV)}, t < t_{(PRECHG)}$                                                                                                                                    | 240                            | 255                          | 270                            | mV   |

| CHARGE TAPI         | ER AND TERMINATION DETECTION                                                                                                     |                                                                                                                                                                                      |                                |                              |                                |      |

| (TAPER)             | Taper current detect range (3)                                                                                                   | $V_{I(OUT)} > V_{(RCH)}, t < t_{(TAPER)}$                                                                                                                                            | 10                             |                              | 100                            | mA   |

| (SET_TAPER)         | Voltage at ISET pin for charge TAPER detection                                                                                   | $V_{I(OUT)} > V_{(RCH)}, t < t_{(TAPER)}$                                                                                                                                            | 235                            | 250                          | 265                            | mV   |

| (SET_TERM)          | Voltage at ISET pin for charger termination detection <sup>(4)</sup>                                                             | V <sub>I(OUT)</sub> > V <sub>(RCH)</sub>                                                                                                                                             | 11                             | 18                           | 25                             | mV   |

|                     | De-glitch time for I <sub>(TAPER)</sub>                                                                                          | $V_{(CHG)}$ min $\ge 4.5$ V, charging current increasing or decreasing above and below; 100-ns fall time, 10-mV overdrive                                                            | 250                            | 375                          | 500                            | ms   |

|                     | De-glitch time for $I_{(TERM)}$                                                                                                  | V <sub>(CHG)</sub> min ≥ 4.5 V, charging current<br>decreasing below;100-ns fall time,<br>10-mV overdrive                                                                            | 250                            | 375                          | 500                            | ms   |

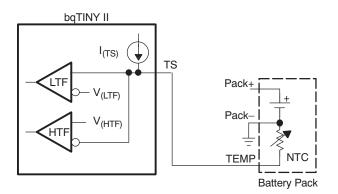

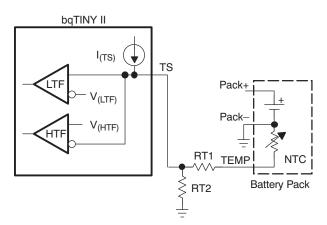

| EMPERATUR           | E COMPARATOR                                                                                                                     |                                                                                                                                                                                      |                                |                              |                                |      |

| / <sub>(LTF)</sub>  | Low (cold) temperature threshold                                                                                                 |                                                                                                                                                                                      | 2.475                          | 2.50                         | 2.525                          | V    |

| (HTF)               | High (hot) temperature threshold                                                                                                 |                                                                                                                                                                                      | 0.485                          | 0.5                          | 0.515                          | V    |

| (TS)                | TS current source                                                                                                                |                                                                                                                                                                                      | 95                             | 102                          | 110                            | μA   |

|                     | De-glitch time for temperature fault                                                                                             |                                                                                                                                                                                      | 250                            | 375                          | 500                            | ms   |

| BATTERY REC         | CHARGE THRESHOLD                                                                                                                 | · · ·                                                                                                                                                                                |                                |                              |                                |      |

| / <sub>(RCH)</sub>  | Recharge threshold                                                                                                               | V <sub>(CHG)</sub> min≥ 4.5 V                                                                                                                                                        | V <sub>O(REG)</sub> -<br>0.115 | V <sub>O(REG)</sub> -<br>0.1 | V <sub>O(REG)</sub> -<br>0.085 | V    |

$V_{O(REG)} + V_{(DO-MAX)} \le V_{(CHG)} = V_{(AC)} \text{ or } V_{(USB)}, I_{(TERM)} < I_O \le 1 \text{ A}, 0^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$

$$I_{(PRECHG)} = \frac{KSET \times V_{(SET\_PRECHG)}}{R_{(ISET)}}$$

$$I_{(TAPER)} = \frac{KSET \times V_{(SET\_TAPER)}}{R_{(ISET)}}$$

$$I_{(TERM)} = \frac{KSET \times V_{(SET\_TAPER)}}{R_{(ISET)}}$$

$$(4)$$

TEXAS INSTRUMENTS

www.ti.com

### **Battery Charger Electrical Characteristics (continued)**

### $V_{O(REG)} + V_{(DO-MAX)} \le V_{(CHG)} = V_{(AC)} \text{ or } V_{(USB)}, I_{(TERM)} < I_O \le 1 \text{ A}, 0^{\circ}C < T_A < 85^{\circ}C$

|                          | PARAMETER                                                 |                                 | TEST CONDITIONS                                                                                                                                                                 | MIN                                                     | TYP   | MAX                                                    | UNIT |

|--------------------------|-----------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|--------------------------------------------------------|------|

|                          | De-glitch time                                            |                                 | $\begin{array}{l} V_{\rm (CHG)} \mbox{ min} \geq 4.5 \mbox{ V},  V_{\rm (OUT)} \\ \mbox{ decreasing below threshold; 100-ns} \\ \mbox{ fall time, 10-mV overdrive} \end{array}$ | 250                                                     | 375   | 500                                                    | ms   |

| TIMERS                   |                                                           |                                 |                                                                                                                                                                                 |                                                         |       |                                                        |      |

| (PRECHG)                 | Precharge timer                                           |                                 | $V_{(CHG)}$ min ≥ 4.5 V                                                                                                                                                         | 1500                                                    | 1800  | 2160                                                   | S    |

| (TAPER)                  | Taper timer                                               |                                 | V <sub>(CHG)</sub> min≥ 4.5 V                                                                                                                                                   | 1500                                                    | 1800  | 2160                                                   | S    |

| t <sub>(CHG)</sub>       | Charge timer                                              |                                 | V <sub>(CHG)</sub> min≥ 4.5 V                                                                                                                                                   | 15000                                                   | 18000 | 21600                                                  | S    |

| SLEEP AND S              | TANDBY                                                    |                                 |                                                                                                                                                                                 |                                                         |       |                                                        |      |

| V <sub>(SLP-ENTRY)</sub> | Sleep-mode entry threshold, $\overline{PG}$ output = high |                                 | 2.3 V $\leq$ V <sub>I(OUT)</sub> $\leq$ V <sub>O(REG)</sub>                                                                                                                     |                                                         |       | V <sub>(CHG)</sub> ≤<br>V <sub>I(OUT)</sub><br>+150 mV | V    |

| V <sub>(SLP_EXIT)</sub>  | Sleep-mode exit threshol                                  | d, $\overline{PG}$ output = low | 2.3 V $\leq$ V <sub>I(OUT)</sub> $\leq$ V <sub>O(REG)</sub>                                                                                                                     | V <sub>(CHG)</sub> ≥<br>V <sub>I(OUT)</sub> +19<br>0 mV |       |                                                        | V    |

|                          | De-glitch time for sleep n                                | node entry and exit             | AC or USB decreasing below<br>threshold; 100-ns fall time, 10-mV<br>overdrive                                                                                                   | 200                                                     | 375   | 500                                                    | ms   |

| t <sub>(USB_DEL)</sub>   | Delay between valid USE<br>and start of charging pro-     |                                 |                                                                                                                                                                                 |                                                         | 375   |                                                        | ms   |

| CHARGER PO               | WER-ON-RESET, UVLO, A                                     |                                 |                                                                                                                                                                                 | 1                                                       |       |                                                        |      |

| V <sub>(CHGUVLO)</sub>   | Charger under-voltage lo                                  |                                 | V <sub>(CHG)</sub> decreasing                                                                                                                                                   | 2.27                                                    | 2.5   | 2.75                                                   | V    |

| (000)                    | Hysteresis                                                |                                 |                                                                                                                                                                                 |                                                         | 27    |                                                        | mV   |

| V <sub>(CHGOVLO)</sub>   | Charger over-voltage loc                                  | kout                            | V <sub>(AC)</sub> increasing                                                                                                                                                    |                                                         | 6.6   |                                                        | V    |

| (01100720)               | Hysteresis                                                |                                 |                                                                                                                                                                                 |                                                         |       | 0.5                                                    | V    |

| CHARGER OV               | /ER TEMPERATURE SUSP                                      | END                             |                                                                                                                                                                                 | 1                                                       |       |                                                        |      |

| T <sub>(suspend)</sub>   | Temperature at which ch operation                         | arger suspends                  |                                                                                                                                                                                 |                                                         | 145   |                                                        | °C   |

| T <sub>(hyst)</sub>      | Hysteresis of suspend th                                  | reshold                         |                                                                                                                                                                                 |                                                         | 20    |                                                        | °C   |

| LOGIC SIGNA              | LS DEFMAIN, DEFCORE, I                                    | PS_SEQ, IFLSB                   |                                                                                                                                                                                 |                                                         |       |                                                        |      |

| V <sub>IH</sub>          | High level input voltage                                  |                                 | I <sub>IH</sub> = 20 μA                                                                                                                                                         | V <sub>CC</sub> -0.5                                    |       | V <sub>cc</sub>                                        | V    |

| V <sub>IL</sub>          | Low level input voltage                                   |                                 | I <sub>IL</sub> = 10 μA                                                                                                                                                         | 0                                                       |       | 0.4                                                    | V    |

| I <sub>IB</sub>          | Input bias current                                        |                                 |                                                                                                                                                                                 |                                                         | 0.01  | 1.0                                                    | μA   |

| LOGIC SIGNA              | LS GPIO1-4                                                |                                 |                                                                                                                                                                                 | •                                                       |       |                                                        |      |

| V <sub>OL</sub>          | Low level output voltage                                  |                                 | $I_{OL}$ = 1 mA, configured as an open-<br>drain output                                                                                                                         |                                                         |       | 0.3                                                    | V    |

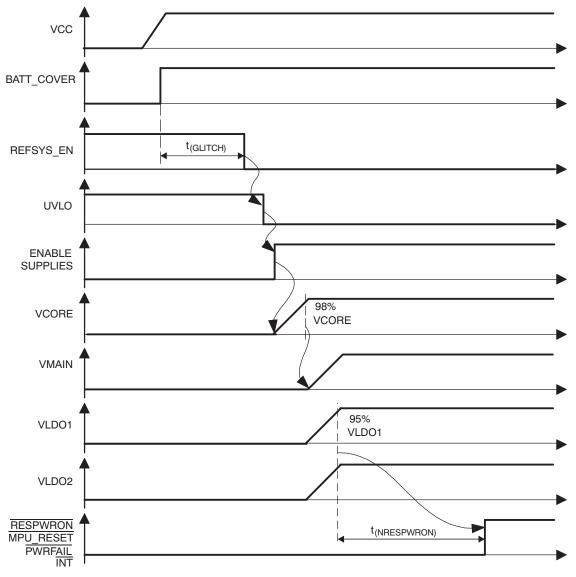

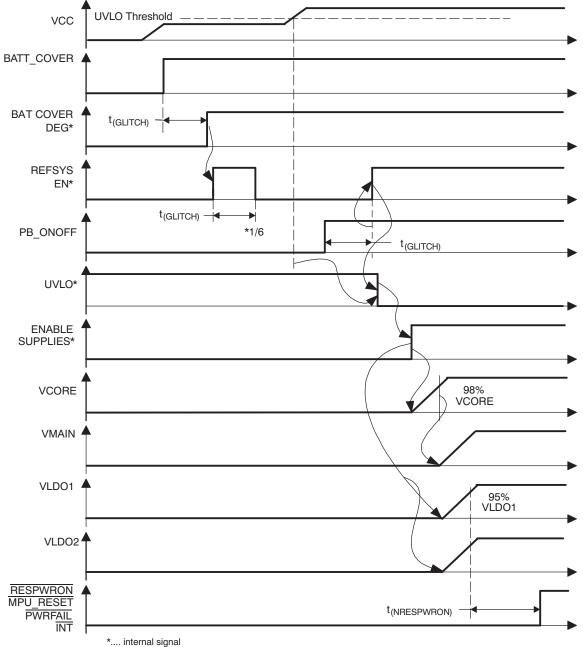

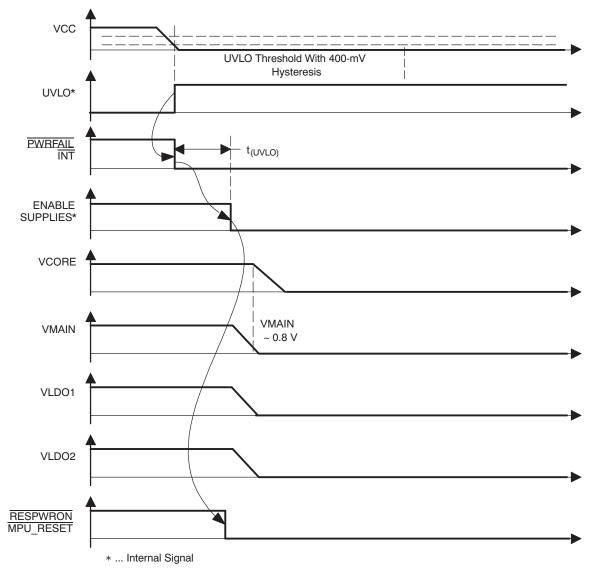

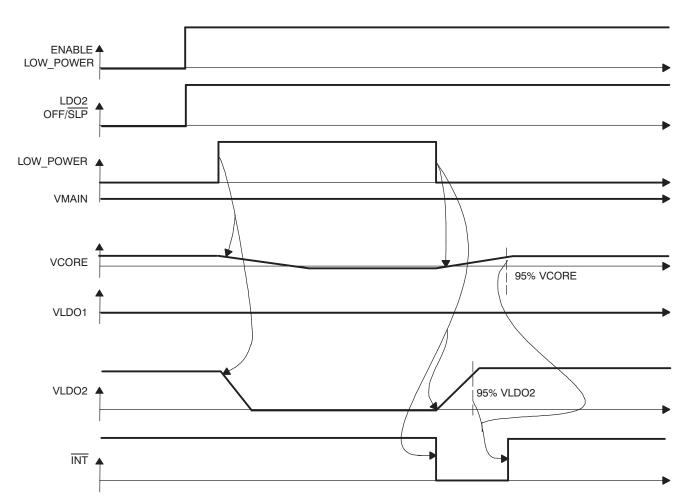

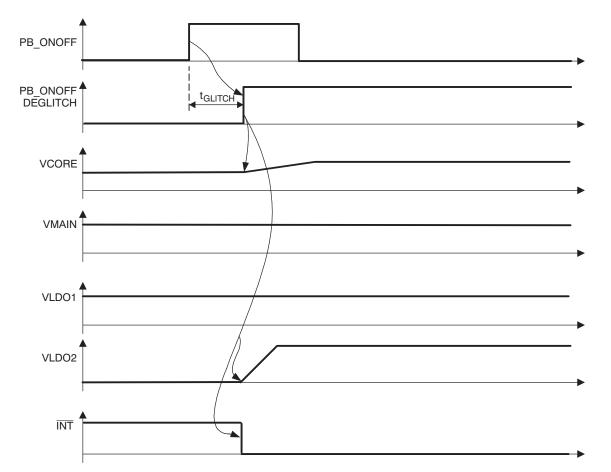

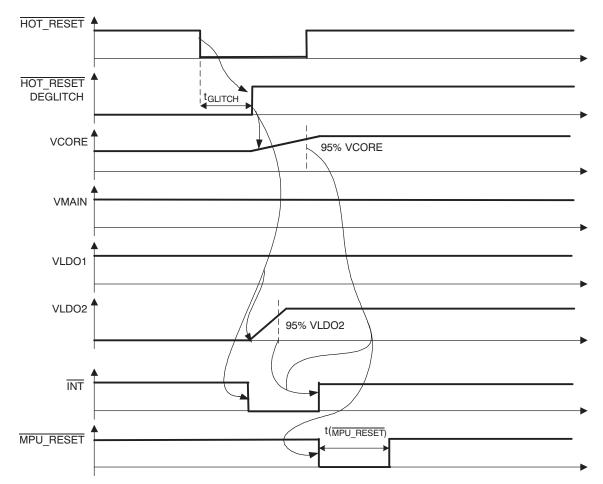

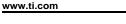

| V <sub>OH</sub>          | High level output voltage                                 |                                 | Configured as an open-drain output                                                                                                                                              |                                                         |       | 6                                                      | V    |