# TPS23734 IEEE 802.3bt Type 3 Class 1-4 PoE PD with High Efficiency DC-DC Controller

### 1 Features

- Complete IEEE 802.3bt Type 3 (Class 1-4) and 802.3at PoE PD Solution

- EA Gen 2 Logo-Ready (PoE 2 PD Controller)

- Robust 100 V, 0.3 Ω (typ) Hotswap MOSFET

- Supports Power Levels for up to 30-W Operation

- Integrated PWM Controller for Flyback or Active Clamp Forward Configuration

- Flyback Control with Primary-Side Regulation

- Supports CCM Operation

- ±1.5% (tvp. 5-V Output) Load Regulation (0-100% load range) — with Sync FET

- ±3% (typ, 12-V Output) Load Regulation (5-100% load range) — Diode Rectified

- Also supports secondary-side regulation

- Soft-Start Control with Advanced Startup and **Hiccup Mode Overload Protection**

- Soft-Stop Shutdown

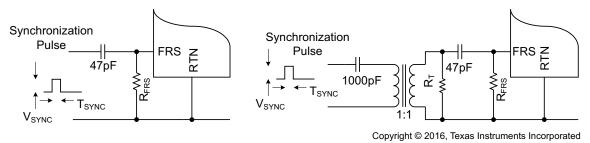

- Adjustable Frequency with Synchronization

- Programmable Frequency Dithering for EMI

- Automatic Maintain Power Signature (MPS)

- Auto-adjust to PSE Type and Load Current with Auto-stretch

- Primary Adapter Priority Input

- -40°C to 125°C Junction Temperature Range

## 2 Applications

- Video and VoIP Telephones

- **Access Points**

- **Security Cameras**

- Redundant Power Feeds or Power Sharing

# 3 Description

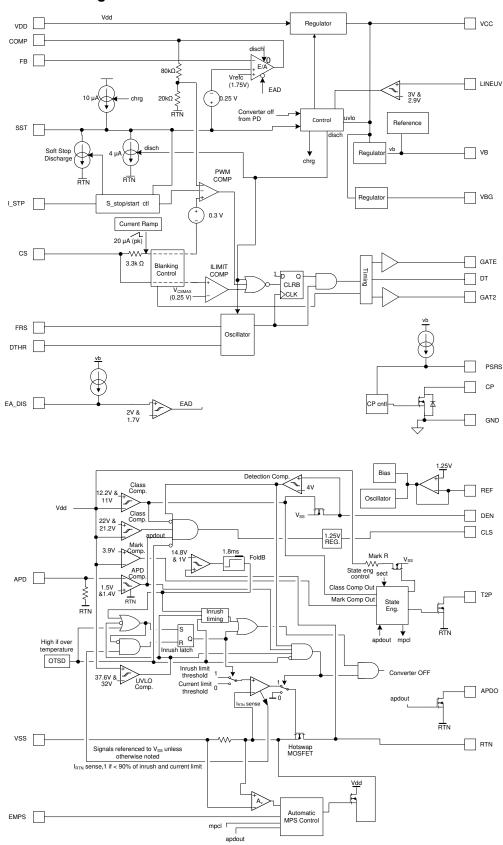

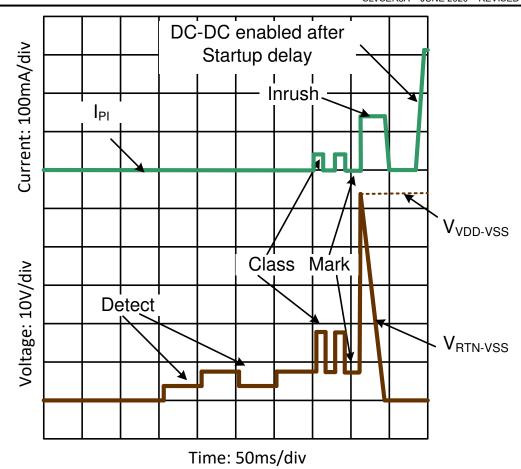

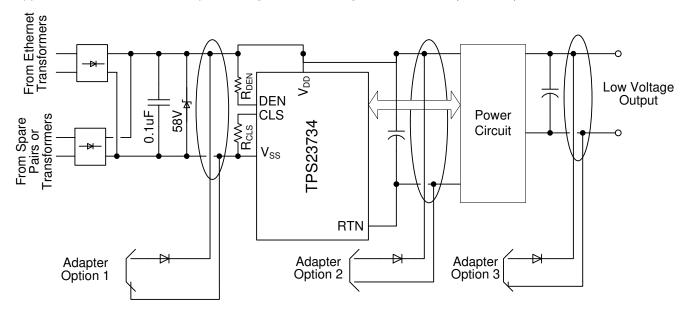

The TPS23734 device combines a Power over Ethernet (PoE) powered device (PD) interface, and a current-mode DC-DC controller optimized for flyback and active clamp forward (ACF) switching regulator designs. In the case of flyback configuration, the use of primary-side regulation (PSR) is supported. The PoE interface supports the IEEE 802.3bt and IEEE 802.3at standards for applications needing up to 25.5 W or less at PD input.

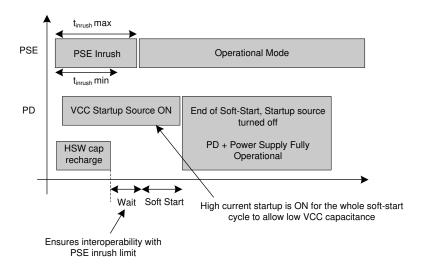

Programmable spread spectrum frequency dithering (SSFD) is provided to minimize the size and cost of EMI filter. Advanced Startup with adjustable soft-start helps to use minimal bias capacitor while simplifying converter startup and hiccup design, also ensuring that IEEE 802.3bt/at startup requirements are met.

The soft-stop feature minimizes stress on switching power FETs, allowing FET BOM cost reduction.

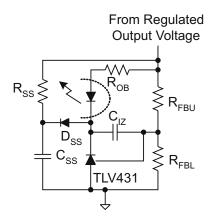

The PSR feature of the DC-DC controller uses feedback from an auxiliary winding for control of the output voltage, eliminating the need for external shunt regulator and optocoupler. It is optimized for continuous conduction mode (CCM), and can work with secondary side synchronous rectification, resulting in optimum efficiency, regulation accuracy and step load response over multiple outputs.

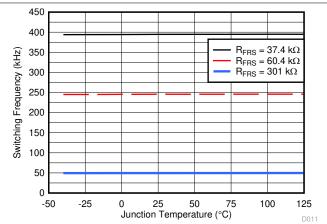

The DC-DC controller features slope compensation and blanking. Typical switching frequency is 250 kHz.

The automatic MPS enables applications with low power modes or multiple power feeds. It automatically adjusts its pulsed current amplitude and duration according to PSE Type and system conditions, to maintain power while minimizing consumption.

## Device Information (1)

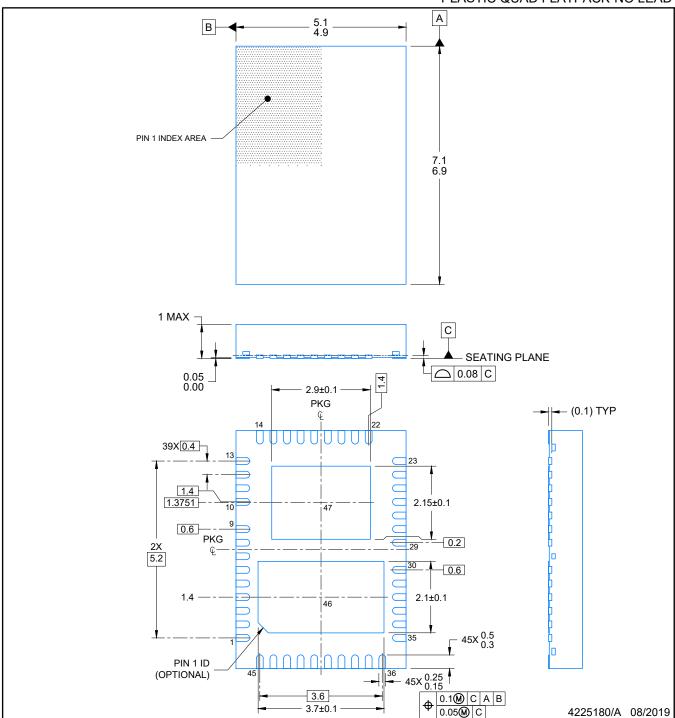

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS23734    | VSON (45) | 7.00 mm × 5.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

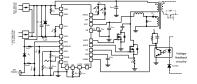

Simplified Application

# **Table of Contents**

| 1 Features                                       | 1   | 8.4 Device Functional Modes             | 28 |

|--------------------------------------------------|-----|-----------------------------------------|----|

| 2 Applications                                   |     | 9 Application and Implementation        |    |

| 3 Description                                    | .1  | 9.1 Application Information             |    |

| 4 Revision History                               | . 2 | 9.2 Typical Application                 |    |

| 5 Device Comparison Table                        | .3  | 10 Power Supply Recommendations         | 45 |

| 6 Pin Configuration and Functions                |     | 11 Layout                               |    |

| 7 Specifications                                 |     | 11.1 Layout Guidelines                  |    |

| 7.1 Absolute Maximum Ratings                     |     | 11.2 Layout Example                     |    |

| 7.2 ESD Ratings                                  | . 6 | 11.3 EMI Containment                    | 46 |

| 7.3 Recommended Operating Conditions             | .7  | 11.4 Thermal Considerations and OTSD    | 46 |

| 7.4 Thermal Information                          | .7  | 11.5 ESD                                | 46 |

| 7.5 Electrical Characteristics: DC-DC Controller |     | 12 Device and Documentation Support     | 47 |

| Section                                          | . 7 | 12.1 Documentation Support              |    |

| 7.6 Electrical Characteristics PoE               | 10  | 12.2 Support Resources                  |    |

| 7.7 Typical Characteristics                      | 14  | 12.3 Trademarks                         |    |

| 8 Detailed Description                           |     | 12.4 Electrostatic Discharge Caution    | 47 |

| 8.1 Overview                                     | 18  | 12.5 Glossary                           |    |

| 8.2 Functional Block Diagram                     | 19  | 13 Mechanical, Packaging, and Orderable |    |

| 8.3 Feature Description                          |     | Information                             | 47 |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision * (June 2020) to Revision A (September 2020)                             | Page |

|---|-----------------------------------------------------------------------------------------------|------|

| • | Updated the numbering format for tables, figures and cross-references throughout the document | 1    |

| • | Changed status from "Advance Information" to "Production Data"                                | 1    |

|   | · ·                                                                                           |      |

# **5 Device Comparison Table**

| KEY FEATURES                                   | TPS23730                           | TPS23731  | TPS23734  |

|------------------------------------------------|------------------------------------|-----------|-----------|

| Class Range                                    | 1-6                                | 1-4       | 1-4       |

| ACF Support                                    | Yes                                | No        | Yes       |

| SSFD                                           | Yes                                | Yes       | Yes       |

| Soft-stop                                      | Yes                                | Yes       | Yes       |

| Advanced Startup                               | Yes                                | Yes       | Yes       |

| PSR (Flyback)                                  | Yes                                | Yes       | Yes       |

| Auto MPS                                       | Yes                                | Yes       | Yes       |

| PPD                                            | Yes                                | No        | No        |

| APD                                            | Yes                                | Yes       | Yes       |

| PoE allocated power and AUX power indicator(s) | TPH/TPL (parallel) or TPL (serial) | T2P, APDO | T2P, APDO |

# **6 Pin Configuration and Functions**

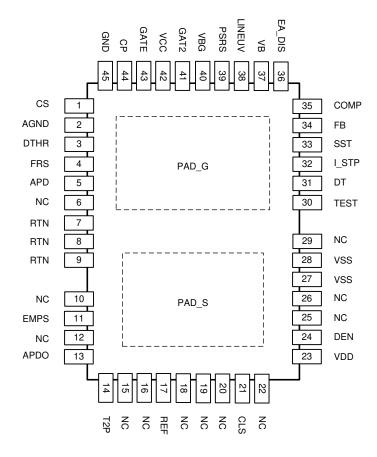

Figure 6-1. RMT Package 45-Pin VSON Top View

# **Pin Functions**

|         | PIN    |     | DECODINE COLUMN                                                                                                                                                                                                                                                                                                                                                            |  |

|---------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.     | NAME   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |  |

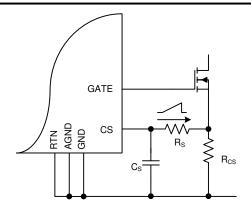

| 1       | CS     | I/O | DC-DC controller current sense input. Connect directly to the external power current sense resistor.                                                                                                                                                                                                                                                                       |  |

| 2       | AGND   | -   | AGND is the DC-DC converter analog return. Tie to RTN and GND on the circuit board.                                                                                                                                                                                                                                                                                        |  |

| 3       | DTHR   | 0   | Used for spread spectrum frequency dithering. Connect a capacitor (determines the modulating frequency) from DTHR to RTN and a resistor (determines the amount of dithering) from DTHR to FRS. If dithering is not used, short DTHR to VB pin.                                                                                                                             |  |

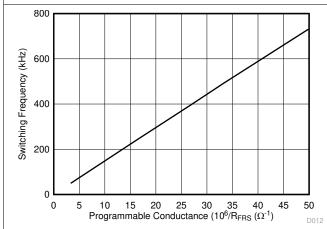

| 4       | FRS    | I   | This pin controls the switching frequency of the DC-DC converter. Tie a resistor from this pin to RTN to set the frequency.                                                                                                                                                                                                                                                |  |

| 5       | APD    | 1   | Primary auxiliary power detect input. Raise 1.5 V above RTN to disable pass MOSFET, also turning class off. If not used, connect APD to RTN.                                                                                                                                                                                                                               |  |

| 7, 8, 9 | RTN    | -   | RTN is the output of the PoE hotswap and the reference ground for the DC-DC controller.                                                                                                                                                                                                                                                                                    |  |

| 11      | EMPS   | I   | Automatic MPS enable input, referenced to RTN, internally pulled-up to 5-V internal rail. Tie to RTN to disable automatic MPS.                                                                                                                                                                                                                                             |  |

| 13      | APDO   | 0   | Active low output referenced to RTN, indicates that an auxiliary power adapter is detected via the APD input.                                                                                                                                                                                                                                                              |  |

| 14      | T2P    | 0   | Active low output that indicates a PSE has performed the IEEE 802.3at Type 2 hardware classification, or APD is active.                                                                                                                                                                                                                                                    |  |

| 17      | REF    | 0   | Internal 1.25-V voltage reference. Connect a 49.9-kΩ_1% resistor from REF to VSS.                                                                                                                                                                                                                                                                                          |  |

| 21      | CLS    | 0   | Connect a resistor from CLS to VSS to program the classification current.                                                                                                                                                                                                                                                                                                  |  |

| 23      | VDD    | _   | Positive input power rail for PoE interface circuit and source of DC-DC converter start-up current. Bypass with a 0.1 $\mu$ F to VSS and protect with a TVS.                                                                                                                                                                                                               |  |

| 24      | DEN    | I/O | Connect a 25.5-k $\Omega$ resistor from DEN to VDD to provide the PoE detection signature. Pulling pin to VSS during powered operation causes the internal hotswap MOSFET to turn off.                                                                                                                                                                                     |  |

| 27, 28  | VSS    | -   | Negative power rail derived from the PoE source.                                                                                                                                                                                                                                                                                                                           |  |

| 30      | TEST   | 0   | Used internally for test purposes only. Leave open.                                                                                                                                                                                                                                                                                                                        |  |

| 31      | DT     | 1   | Connect a resistor from DT to AGND to set the GATE to GAT2 dead time. Tie DT to VB to disable GAT2 operation.                                                                                                                                                                                                                                                              |  |

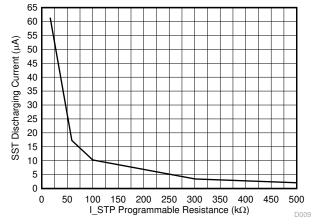

| 32      | I_STP  | I   | This pin sets the SST discharge current during a soft-stop event independently from the setting used during a regular soft-start event. Connect a resistor from this pin to AGND to set the DC/DC soft-stop rate.                                                                                                                                                          |  |

| 33      | SST    | I/O | A capacitor from SST to RTN pin sets the soft-start (I <sub>SSC</sub> charge current) and the hiccup timer (I <sub>SSD</sub> discharge current) for the DC-DC converter. Connect a capacitor from this pin to RTN to set the DC/DC startup rate.                                                                                                                           |  |

| 34      | FB     | I   | Converter error amplifier inverting (feedback) input. If flyback configuration with primary-side regulation, it is typically driven by a voltage divider and capacitor from the auxiliary winding, working with CP pin, FB also being connected to the COMP compensation network. If optocoupler feedback is enabled, tie FB to VB.                                        |  |

| 35      | COMP   | I/O | Compensation output of the DC-DC convertor error amplifier or control loop input to the PWM. If the internal error amplifier is used, connect the compensation networks from this pin to the FB pin to compensate the converter. If optocoupler feedback is enabled, the optocoupler and its network pulled up to VB directly drives the COMP pin.                         |  |

| 36      | EA_DIS | I   | Error Amplifier disable input, referenced to AGND, internally pulled-up to 5V internal rail. Leave EA_DIS open to disable the Error amplifier, to enable optocoupler feedback for example. Connect to AGND otherwise.                                                                                                                                                      |  |

| 37      | VB     | 0   | 5-V bias rail for DC/DC control circuits and the feedback optocoupler (when in use). Connect a 0.1-uF capacitor from this pin to AGND to provide bypassing.                                                                                                                                                                                                                |  |

| 38      | LINEUV | I   | LINEUV is used to monitor the bulk capacitor voltage to trigger a soft-stop event when an undervoltage condition is detected if APD is low. If not used, connect LINEUV to VB pin.                                                                                                                                                                                         |  |

| 39      | PSRS   | I   | PSR Sync enable input, referenced to AGND, internally pulled-up to 5V internal rail. PSRS works with CP pin to support flyback architecture using primary-side regulation. Leave PSRS open if the flyback output stage is configured with synchronous rectification and uses PSR. If diode rectification is used, or for applications not using PSR, connect PSRS to AGND. |  |

## www.ti.com

| Р                                                 | IN    | 1/0 | DESCRIPTION                                                                                                                                                         |  |

|---------------------------------------------------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.                                               | NAME  | I/O | DESCRIPTION                                                                                                                                                         |  |

| 40                                                | VBG   | 0   | 5-V bias rail for the switching FET gate driver circuit. For internal use only. Bypass with a 0.1-μF ceramic capacitor to GND pin.                                  |  |

| 41                                                | GAT2  | 0   | ate drive output for a second DC-DC converter switching MOSFET.                                                                                                     |  |

| 42                                                | VCC   | I/O | DC/DC converter bias voltage. The internal startup current source and converter bias winding output power this pin. Connect a 1µF minimum ceramic capacitor to RTN. |  |

| 43                                                | GATE  | 0   | Gate drive output for the main DC-DC converter switching MOSFET                                                                                                     |  |

| 44                                                | СР    | 0   | CP provides the clamp for the primary-side regulation loop. Connect this pin to the lower end bias winding of the flyback transformer.                              |  |

| 45                                                | GND   | -   | .Power ground used by the flyback power FET gate driver and CP. Connect to RTN.                                                                                     |  |

| 6, 10, 12,<br>15, 16,<br>18-20, 22,<br>25, 26, 29 | NC    | -   | No connect pin. Leave open.                                                                                                                                         |  |

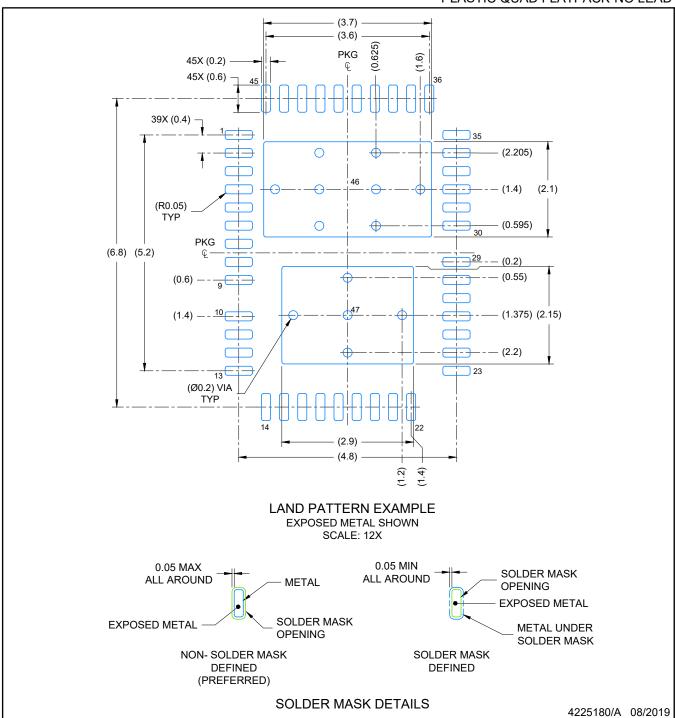

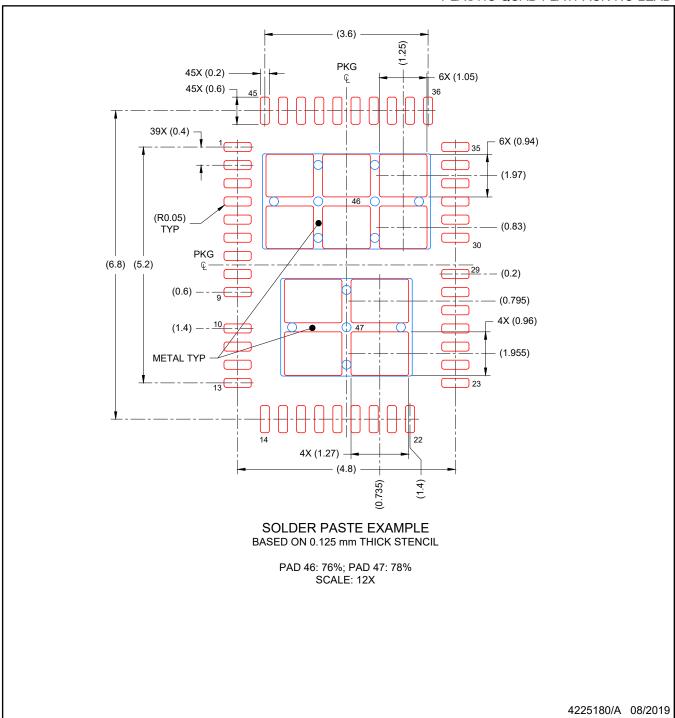

| 47                                                | PAD_S | -   | The exposed thermal pad must be connected to VSS. A large fill area is required to assist in heat dissipation.                                                      |  |

| 46                                                | PAD_G | -   | The exposed thermal pad must be connected to RTN. A large fill area is required to assist in heat dissipation.                                                      |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Voltage are with respect to V<sub>SS</sub> (unless otherwise noted)<sup>(1)</sup>

|                       | 35 (                                                                                                                                                                 | MIN                | MAX                | UNIT |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|--|

|                       | VDD, DEN, GND, AGND, RTN <sup>(2)</sup>                                                                                                                              | -0.3               | 100                |      |  |

| Input voltage         | VDD to RTN                                                                                                                                                           | -0.3               | 100                | V    |  |

|                       | APD, FB, CS, EA_DIS, LINEUV, PSRS, EMPS, all to RTN                                                                                                                  | -0.3               | 6.5                |      |  |

|                       | FRS <sup>(3)</sup> , COMP, VB <sup>(3)</sup> , VBG <sup>(3)</sup> , I_STP <sup>(3)</sup> , DTHR <sup>(3)</sup> , SST <sup>(3)</sup> , DT <sup>(3)</sup> , all to RTN | -0.3               | 6.5                |      |  |

|                       | VCC to RTN                                                                                                                                                           | -0.3               | 19                 |      |  |

|                       | GATE <sup>(3)</sup> , GAT2 <sup>(3)</sup> , all to RTN                                                                                                               | -0.3 V(            | CC+0.3             |      |  |

| Voltage               | CP to GND                                                                                                                                                            | -0.3               | 60                 | V    |  |

|                       | GND, AGND, all to RTN                                                                                                                                                | -0.3               | 0.3                |      |  |

|                       | REF <sup>(3)</sup> , CLS <sup>(3)</sup>                                                                                                                              | -0.3               | 6.5                |      |  |

|                       | T2P, APDO , all to RTN                                                                                                                                               | -0.3               | 19                 |      |  |

|                       | VB, VBG, VCC                                                                                                                                                         | Internally limited |                    |      |  |

| Sourcing current      | COMP                                                                                                                                                                 | Internally limited | Internally limited |      |  |

|                       | REF                                                                                                                                                                  | Internally limited |                    |      |  |

| Sourcing current      | CLS                                                                                                                                                                  |                    | 65                 | mA   |  |

|                       | RTN                                                                                                                                                                  | Internally limited |                    |      |  |

| Sinking current       | DEN                                                                                                                                                                  |                    | 1                  | mA   |  |

|                       | COMP                                                                                                                                                                 | Internally limited |                    |      |  |

| Sinking current       | T2P, APDO                                                                                                                                                            |                    | 10                 | mA   |  |

| Peak sourcing current | СР                                                                                                                                                                   |                    | 2                  | Α    |  |

| Peak sinking current  | СР                                                                                                                                                                   |                    | 0.7                | Α    |  |

| T <sub>J(max)</sub>   | Maximum junction temperature                                                                                                                                         | Internally Limited |                    | °C   |  |

| T <sub>stg</sub>      | Storage temperature                                                                                                                                                  | <b>–</b> 65        | 150                | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2)  $I_{RTN} = 0$  for  $V_{RTN} > 80$  V.

- (3) Do not apply voltage to these pins.

# 7.2 ESD Ratings

|                    |                          |                                                                                | VALUE  | UNIT  |

|--------------------|--------------------------|--------------------------------------------------------------------------------|--------|-------|

|                    |                          | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000  |       |

| \/                 | Electrostatic discharge  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500   |       |

| V <sub>(ESD)</sub> | Liectrostatic discriarge | IEC 61000-4-2 contact discharge <sup>(3)</sup>                                 | ±8000  | \ \ \ |

|                    |                          | IEC 61000-4-2 air-gap discharge <sup>(3)</sup>                                 | ±15000 |       |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) Surges per EN61000-4-2, 1999 applied between RJ-45 and output ground and between adapter input and output ground of the TPS23730, TPS23730EVM-093 evaluation module (documentation available on the web). These were the test levels, not the failure threshold.

Product Folder Links: TPS23734

# 7.3 Recommended Operating Conditions

Voltage with respect to V<sub>SS</sub> (unless otherwise noted)

|                     |                                               | MIN  | NOM  | MAX  | UNIT |

|---------------------|-----------------------------------------------|------|------|------|------|

|                     | VDD, RTN, GND, AGND                           | 0    |      | 60   |      |

|                     | VCC to RTN                                    | 0    |      | 16   |      |

| Input voltage range | APD, EA_DIS, LINEUV, PSRS, FB, all to RTN     | 0    |      | VB   | V    |

|                     | CS to RTN                                     | 0    |      | 2    |      |

|                     | CP to GND                                     | 0    |      | 45   |      |

| Voltage range       | COMP to RTN                                   |      |      | VB   | V    |

| Voltage range       | T2P, APDO, all to RTN                         | 0    |      | VCC  | V    |

| Sinking current     | RTN                                           |      |      | 0.65 | Α    |

| Sinking current     | T2P, APDO                                     |      |      | 3    | mA   |

| Sourcing current    | VCC                                           |      |      | 20   | А    |

| Sourcing current    | VB                                            |      |      | 5    | mA   |

| Compositornos       | VB, VBG <sup>(1)</sup>                        | 0.08 | 0.1  | 1    |      |

| Capacitance         | VCC                                           | 0.7  | 1    | 100  | μF   |

| Resistance          | I_STOP                                        | 16.5 |      | 499  | ΚΩ   |

| Resistance          | CLS <sup>(1)</sup>                            | 30   |      |      | Ω    |

|                     | REF <sup>(1)</sup>                            | 48.9 | 49.9 | 50.9 | kΩ   |

|                     | Synchronization pulse width input (when used) | 35   |      |      | ns   |

| TJ                  | Operating junction temperature                | -40  |      | 125  | °C   |

<sup>(1)</sup> Voltage should not be externally applied to this pin.

### 7.4 Thermal Information

|                                | THERMAL METRIC                                         | R (VSON) 48 PINS | UNIT |

|--------------------------------|--------------------------------------------------------|------------------|------|

| R <sub>0JA</sub> (1)           | Junction-to-ambient thermal resistance                 | 38.5             |      |

| R <sub>θJC(top)</sub>          | Junction-to-case (top) thermal resistance              | 23.6             |      |

| R <sub>0JB</sub> (1)           | Junction-to-board thermal resistance                   | 19.3             |      |

| Ψ <sub>JT</sub> <sup>(1)</sup> | Junction-to-top characterization parameter             | 6.8              | °C/W |

| Ψ <sub>JB</sub> <sup>(1)</sup> | Junction-to-board characterization parameter           | 19.3             |      |

| R <sub>0JC(bot_POE)</sub>      | Junction-to-case (bottom PAD_S pad) thermal resistance | 3.9              |      |

| R <sub>0</sub> JC(bot_DCDC)    | Junction-to-case (bottom PAD_G pad) thermal resistance | 9.1              |      |

<sup>(1)</sup> Thermal metrics are not JEDEC standard values and are based on the TPS23731EVM-095 evaluation board.

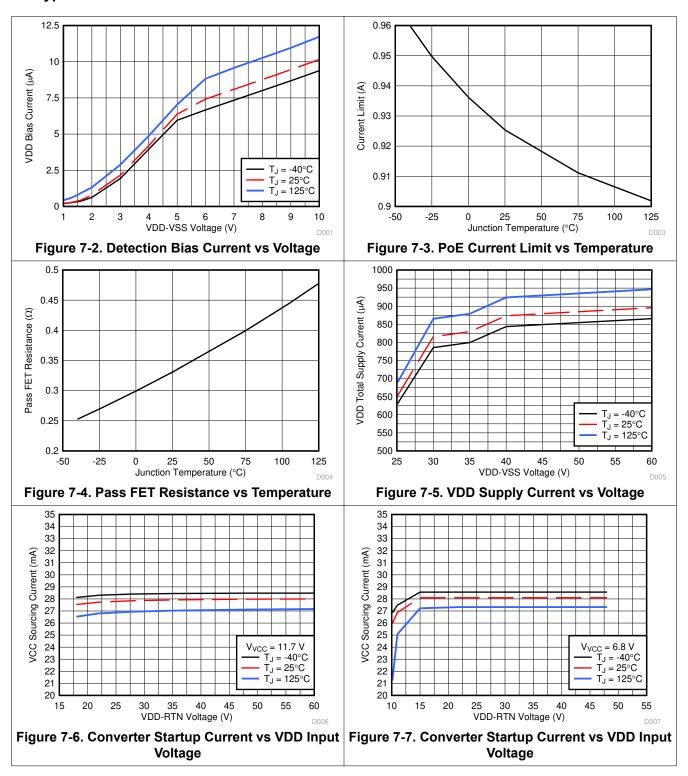

## 7.5 Electrical Characteristics: DC-DC Controller Section

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB;  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ; 8.5 V  $\leq$  V $_{VCC}$   $\leq$  16 V; - 40°C  $\leq$  T $_{J}$   $\leq$  125°C. Positive currents are into pins unless otherwise noted. Typical values are at 25°C. IV $_{VSS}$  = V $_{PTN}$ 1, all voltages referred to V $_{PTN}$ 1, V $_{AGND}$  and V $_{CND}$  unless otherwise noted.

|                      | PARAMETER            | TEST CONDITIONS                       | MIN  | TYP  | MAX  | UNIT |  |

|----------------------|----------------------|---------------------------------------|------|------|------|------|--|

| DC-DC SUPPLY (VCC)   |                      |                                       |      |      |      |      |  |

| V <sub>CUVLO</sub> _ |                      | V <sub>VCC</sub> rising               | 8    | 8.25 | 8.5  | V    |  |

| V <sub>CUVLO_F</sub> | Undervoltage lockout | $V_{VCC}$ falling, $V_{FB} = V_{RTN}$ | 5.85 | 6.1  | 6.35 | V    |  |

| V <sub>CUVLO</sub> _ |                      | Hysteresis <sup>(1)</sup>             | 2    | 2.15 | 2.3  | V    |  |

# 7.5 Electrical Characteristics: DC-DC Controller Section (continued)

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB;  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ; 8.5 V  $\leq$  V $_{VCC}$   $\leq$  16 V; - 40°C  $\leq$  T $_{J}$   $\leq$  125°C. Positive currents are into pins unless otherwise noted. Typical values are at 25°C. [V $_{VSS}$  = V $_{RTN}$ ], all voltages referred to V $_{RTN}$ , V $_{AGND}$  and V $_{GND}$  unless otherwise noted.

|                      | PARAMETER                           | TEST CONDITIONS                                                                                               | MIN   | TYP                  | MAX   | UNIT           |

|----------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|----------------------|-------|----------------|

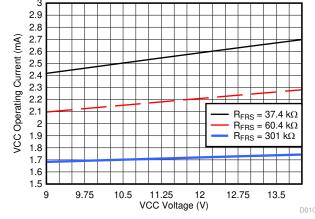

| I <sub>RUN</sub>     | Operating current                   | $V_{VCC}$ = 10 V, $V_{FB}$ = $V_{RTN}$ , $R_{DT}$ = 24.9 k $\Omega$ , CP with 2- $k\Omega$ pull up to 30 V    | 1.4   | 2                    | 2.4   | mA             |

|                      |                                     | V <sub>APD</sub> = 2.5V                                                                                       |       |                      |       |                |

|                      | Startup source current              | V <sub>VDD</sub> ≥ 28V, V <sub>VCC</sub> = 11.7 V                                                             | 21.5  | 30                   | 34    |                |

| I <sub>VC_ST</sub>   |                                     | V <sub>VDD</sub> = 10.2V, V <sub>VCC</sub> = 8.6 V                                                            | 1     | 6                    | 17.5  | mA             |

|                      |                                     | V <sub>VDD</sub> = 10.2V, V <sub>VCC</sub> = 6.8 V                                                            | 8     | 16                   | 32    |                |

|                      | Ota tan fine O                      | $V_{VDD}$ = 10.2 V, $V_{VCC}(0)$ = 0 V, measure time until $V_{CUVLO\_R}$                                     | 0.25  | 0.7                  | 1.15  | ms             |

| t <sub>ST</sub>      | Startup time, $C_{VCC} = 1 \mu F$   | $V_{VDD}$ = 35 V, $V_{VCC}(0)$ = 0 V, measure time until $V_{CUVLO\_R}$                                       | 0.24  | 0.35                 | 0.48  | ms             |

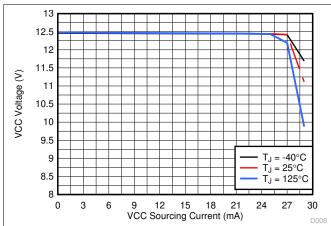

|                      | V00 - t - t                         | Measure V <sub>VCC</sub> during startup, I <sub>VCC</sub> = 0 mA                                              | 11    | 12.5                 | 14    |                |

| $V_{VC\_ST}$         | VCC startup voltage                 | Measure V <sub>VCC</sub> during startup, I <sub>VCC</sub> = 21.5 mA                                           | 11    | 12.5                 | 14    | V              |

| .,                   | V00 6 1 1                           | V <sub>LINEUV</sub> < V <sub>LIUVF</sub> , Measure V <sub>VCC</sub> during soft-stop, I <sub>VCC</sub> = 0 mA | 11    | 12.5                 | 14    | .,             |

| V <sub>VC_SSTP</sub> | VCC soft-stop voltage               | $V_{LINEUV}$ < $V_{LIUVF}$ , Measure $V_{VCC}$ during soft-stop, $I_{VCC}$ = 21.5 mA                          | 11    | 12.5                 | 14    | V              |

| V <sub>B</sub>       |                                     |                                                                                                               |       |                      |       |                |

|                      | Voltage                             | $V_{FB} = V_{RTN}, 8.5 \text{ V} \le V_{VCC} \le 16 \text{ V}, 0 \le I_{VB} \le 5 \text{ mA}$                 | 4.75  | 5.0                  | 5.25  | V              |

| DC-DC TI             | IMING (FRS)                         | 15 1,                                                                                                         |       |                      |       |                |

| f <sub>SW</sub>      | Switching frequency                 | V <sub>FB</sub> = V <sub>RTN</sub> , Measure at GATE                                                          | 223   | 248                  | 273   | kHz            |

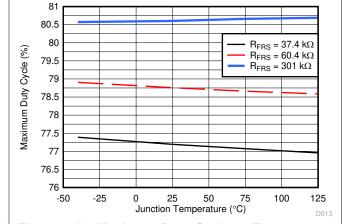

| D <sub>MAX</sub>     | Duty cycle                          | $V_{FB} = V_{RTN}$ , $R_{DT} = 24.9$ kΩ, Measure at GATE                                                      | 74.5% | 78.5%                | 82.5% |                |

| V <sub>SYNC</sub>    | Synchronization                     | Input threshold                                                                                               | 2     | 2.2                  | 2.4   | V              |

|                      | NCY DITHERING RAMP GENE             | RATOR (DTHR)                                                                                                  | -     |                      |       |                |

|                      |                                     |                                                                                                               |       | 3 x I <sub>FRS</sub> |       | μA             |

| I <sub>DTRCH</sub>   | Charging (sourcing) current         | 0.5 V < V <sub>DTHR</sub> < 1.5 V                                                                             | 47.2  | 49.6                 | 52.1  | μA             |

|                      |                                     |                                                                                                               |       | 3 x I <sub>FRS</sub> |       | μA             |

| I <sub>DTRDC</sub>   | Discharging (sinking) current       | 0.5 V < V <sub>DTHR</sub> < 1.5 V                                                                             | 47.2  | 49.6                 | 52.1  | <u>.</u><br>μΑ |

| V <sub>DTUT</sub>    | Dithering upper threshnold          | V <sub>DTHR</sub> rising until I <sub>DTHR</sub> > 0                                                          | 1.41  | 1.513                | 1.60  | · V            |

| V <sub>DTLT</sub>    | Dithering lower threshold           | V <sub>DTHR</sub> falling until I <sub>DTHR</sub> < 0                                                         | 0.43  | 0.487                | 0.54  | V              |

| VDTPP                | Dithering pk-pk amplitude           | SHIK 0 SHIK                                                                                                   | 1.005 | 1.026                | 1.046 | V              |

| ERROR A              | AMPLIFIER (FB, COMP)                |                                                                                                               |       |                      |       |                |

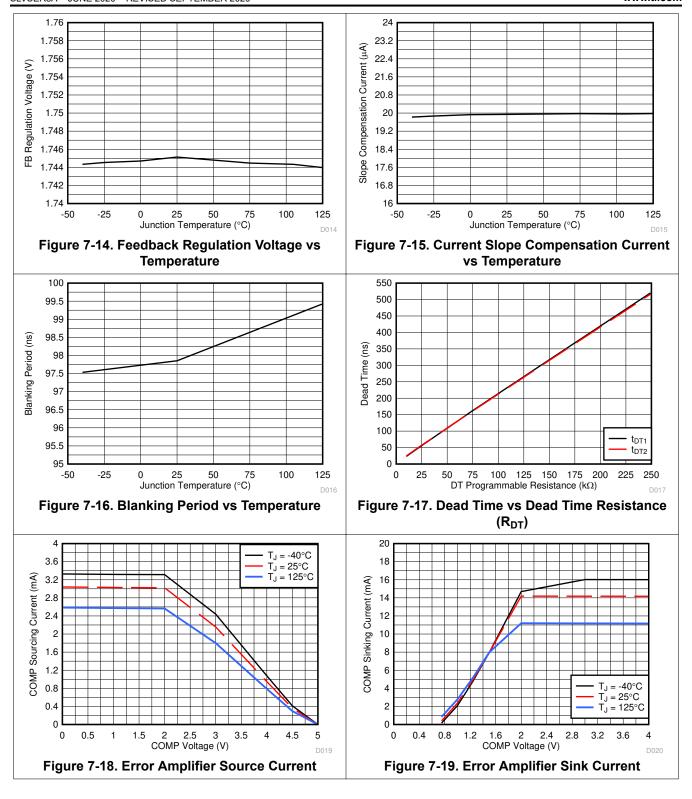

| V <sub>REFC</sub>    | Feedback regulation voltage         |                                                                                                               | 1.723 | 1.75                 | 1.777 | V              |

| I <sub>FB_LK</sub>   | FB leakage current (source or sink) | V <sub>FB</sub> = 1.75 V                                                                                      |       |                      | 0.5   | μΑ             |

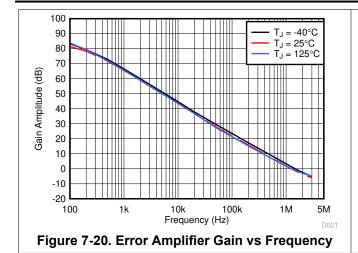

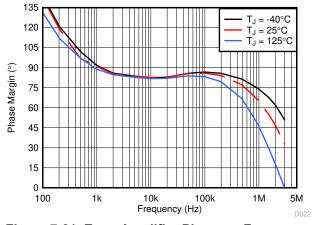

| G <sub>BW</sub>      | Small signal unity gain bandwidth   |                                                                                                               | 0.9   | 1.2                  |       | MHz            |

| A <sub>OL</sub>      | Open loop voltage gain              |                                                                                                               | 70    | 80                   |       | db             |

| V <sub>ZDC</sub>     | 0% duty-cycle threshold             | V <sub>COMP</sub> falling until GATE switching stops                                                          | 1.35  | 1.5                  | 1.65  | V              |

| I <sub>COMPH</sub>   | COMP source current                 | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>COMP</sub> = 3 V                                                  | 1     |                      |       | mA             |

| I <sub>COMPL</sub>   | COMP sink current                   | V <sub>FB</sub> = V <sub>VB</sub> , V <sub>COMP</sub> = 1.25 V                                                | 2.1   | 6                    |       | mA             |

| V <sub>COMPH</sub>   | COMP high voltage                   | $V_{FB}$ = $V_{RTN}$ , 15 kΩ from COMP to RTN                                                                 | 4     |                      | VB    | V              |

| V <sub>COMPL</sub>   | COMP low voltage                    | $V_{FB} = V_{VB}$ , 15 k $\Omega$ from COMP to VB                                                             |       |                      | 1.1   | V              |

Product Folder Links: TPS23734

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

# 7.5 Electrical Characteristics: DC-DC Controller Section (continued)

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB;  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ; 8.5 V  $\leq$  V $_{VCC}$   $\leq$  16 V; - 40°C  $\leq$  T $_{J}$   $\leq$  125°C. Positive currents are into pins unless otherwise noted. Typical values are at 25°C. IV $_{VSS}$  = V $_{PTN}$ 1, all voltages referred to V $_{PTN}$ 1, V $_{ACND}$  and V $_{CND}$  unless otherwise noted.

|                      | PARAMETER                                       | TEST CONDITI                                                                                | IONS                                                                                                                               | MIN   | TYP   | MAX   | UNIT |  |

|----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|--|

|                      | COMP input resistance, error amplifier disabled | EA_DIS open                                                                                 |                                                                                                                                    | 70    | 100   | 130   | kΩ   |  |

|                      | COMP to CS gain                                 | $\Delta V_{CS} / \Delta V_{COMP}$ , $0 V < V_{CS} < 0.2$                                    | 0.19                                                                                                                               | 0.2   | 0.21  | V/V   |      |  |

| SOFT-ST              | ART, SOFT-STOP (SST, I_STP)                     |                                                                                             | ,                                                                                                                                  |       |       | '     |      |  |

| I <sub>SSC</sub>     | Charge current                                  | SST charging, 6.35 V ≤ V <sub>VCC</sub> ≤ 1                                                 | 16 V                                                                                                                               | 7.5   | 10    | 12.5  | μA   |  |

| I <sub>SSD</sub>     | Discharge current                               | SST discharging, 6.35 V ≤ V <sub>VCC</sub>                                                  | ≤ 16 V                                                                                                                             | 3     | 4     | 5     | μΑ   |  |

| V <sub>SFST</sub>    | Soft-start lower threshold                      |                                                                                             |                                                                                                                                    | 0.15  | 0.2   | 0.25  | V    |  |

| V <sub>STUOF</sub>   | Startup turn off threshold                      | V <sub>SST</sub> rising until VCC startup turr                                              | ns off                                                                                                                             | 1.99  | 2.1   | 2.21  | V    |  |

| V                    | Soft-start offset voltage, closed-loop mode     | $V_{FB} = V_{RTN}$ , $V_{SST}$ rising until star                                            | t of switching                                                                                                                     | 0.2   | 0.25  | 0.3   | V    |  |

| V <sub>SSOFS</sub>   | Soft-start offset voltage, peak current mode    | $V_{COMP} = V_{VB}$ , $V_{SST}$ rising until stated                                         | art of switching,                                                                                                                  | 0.55  | 0.6   | 0.65  | V    |  |

| V <sub>SSCL</sub>    | Soft-start clamp                                |                                                                                             |                                                                                                                                    | 2.3   |       | 2.6   | V    |  |

| 1                    | SST discharge current in soft-                  | $R_{I\_STP}$ = 499 k $\Omega$ , $V_{LINEUV}$ < $V_{LIUV}$                                   | /F                                                                                                                                 | 1.5   | 2     | 2.5   | μA   |  |

| I <sub>SSD_SP</sub>  | stop mode                                       | $R_{I\_STP}$ = 16.5 k $\Omega$ , , $V_{LINEUV}$ < $V_{LIU}$                                 | JVF                                                                                                                                | 52.5  | 60.6  | 67.5  | μΑ   |  |

| V <sub>SSTPEN</sub>  | End of soft-stop threshold                      | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>LINEUV</sub> < V <sub>LIUVF</sub>               |                                                                                                                                    | 0.15  | 0.2   | 0.25  | V    |  |

| CURREN               | T SENSE (CS)                                    |                                                                                             |                                                                                                                                    |       |       |       |      |  |

| $V_{CSMAX}$          | Maximum threshold voltage                       | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>CS</sub> rising                                 |                                                                                                                                    | 0.227 | 0.25  | 0.273 | V    |  |

| t <sub>OFFD_IL</sub> | Current limit turn off delay                    | V <sub>CS</sub> = 0.3 V                                                                     |                                                                                                                                    | 25    | 41    | 60    | ns   |  |

| t <sub>OFFD_PW</sub> | PWM comparator turn off delay                   | V <sub>CS</sub> = 0.15 V, EA_DIS open, V <sub>COMP</sub> = 2 V                              |                                                                                                                                    | 25    | 41    | 60    | ns   |  |

|                      | Blanking delay                                  | In additition to t <sub>OFFD_IL</sub> and t <sub>OFFD_PW</sub>                              |                                                                                                                                    | 75    | 95    | 115   | ns   |  |

| V <sub>SLOPE</sub>   | Internal slope compensation voltage             | V <sub>FB</sub> = V <sub>RTN</sub> , Peak voltage at maximum duty cycle, referred to CS     |                                                                                                                                    | 51    | 66    | 79    | mV   |  |

| I <sub>SL_EX</sub>   | Peak slope compensation current                 | V <sub>FB</sub> = V <sub>RTN</sub> , I <sub>CS</sub> at maximum duty component)             | y cycle (ac                                                                                                                        | 14    | 20    | 26    | μΑ   |  |

|                      | Bias current                                    | DC component of CS current                                                                  |                                                                                                                                    | -3    | -2    | -1    | μA   |  |

| LINE UNI             | DERVOLTAGE, SOFT-STOP (L                        | INEUV)                                                                                      | ,                                                                                                                                  |       |       | '     |      |  |

| V <sub>LIUVF</sub>   | LINEUV falling threshold                        | V <sub>LINEUV</sub> falling                                                                 |                                                                                                                                    | 2.86  | 2.918 | 2.976 | V    |  |

| $V_{LIUVH}$          | voltage                                         | Hysteresis <sup>(1)</sup>                                                                   |                                                                                                                                    | 57    | 82    | 107   | mV   |  |

|                      | Leakage current                                 | V <sub>LINEUV</sub> = 3 V                                                                   |                                                                                                                                    |       |       | 1     | μΑ   |  |

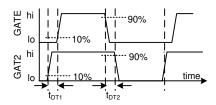

| DEAD TII             | ME (DT)                                         |                                                                                             |                                                                                                                                    |       |       |       |      |  |

| t <sub>DT1</sub>     |                                                 | $R_{DT}$ = 24.9 kΩ, GAT2 ↑ to GATE ↑                                                        | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>PSRS</sub> = 0 V, EA_DIS open, V <sub>COMP</sub> = V <sub>VB</sub> , C <sub>GATE</sub> | 40    | 50    | 62.5  |      |  |

| t <sub>DT2</sub>     | Dood time                                       | $R_{DT} = 24.9 \text{ k}\Omega, \text{ GATE }\downarrow \text{ to}$                         |                                                                                                                                    | 40    | 50    | 62.5  | no   |  |

| t <sub>DT1</sub>     | - Dead time                                     | R <sub>DT</sub> = 75 kΩ, GAT2 ↑ to GATE                                                     | = 1 nF, C <sub>GAT2</sub> = 0.5<br>nF,                                                                                             | 120   | 150   | 188   | ns   |  |

| t <sub>DT2</sub>     |                                                 | $R_{DT}$ = 75 kΩ, GATE ↓ to GAT2 $V_{VCC}$ = 10 V                                           |                                                                                                                                    | 120   | 150   | 188   |      |  |

| GATE                 | 1                                               | 1                                                                                           | Į.                                                                                                                                 |       |       |       |      |  |

|                      | Peak source current                             | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>VCC</sub> = 10 V, V <sub>GATE</sub> measurement | = 0 V, pulsed                                                                                                                      | 0.3   | 0.5   | 0.8   | Α    |  |

|                      | 1                                               | +                                                                                           |                                                                                                                                    |       |       |       |      |  |

# 7.5 Electrical Characteristics: DC-DC Controller Section (continued)

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB;  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ; 8.5 V  $\leq$  V $_{VCC}$   $\leq$  16 V; - 40°C  $\leq$  T $_{J}$   $\leq$  125°C. Positive currents are into pins unless otherwise noted. Typical values are at 25°C. [V $_{VSS}$  = V $_{RTN}$ ], all voltages referred to V $_{RTN}$ , V $_{AGND}$  and V $_{GND}$  unless otherwise noted.

|                      | PARAMETER                  | TEST CONDITIONS                                                                                            | MIN   | TYP   | MAX   | UNIT |

|----------------------|----------------------------|------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                      | Peak sink current          | V <sub>FB</sub> = V <sub>RTN</sub> , V <sub>VCC</sub> = 10 V, V <sub>GATE</sub> = 10 V, pulsed measurement | 0.6   | 0.9   | 1.45  | Α    |

|                      | Rise time <sup>(2)</sup>   | $t_{prr10-90}$ , $C_{GATE}$ = 1 nF , $V_{VCC}$ = 10 V                                                      |       | 30    |       | ns   |

|                      | Fall time <sup>(2)</sup>   | t <sub>pff90-10</sub> , C <sub>GATE</sub> = 1 nF , V <sub>VCC</sub> = 10 V                                 |       | 15    |       | ns   |

| GAT2                 |                            |                                                                                                            |       |       |       |      |

|                      | Peak source current        | $V_{FB}$ = $V_{RTN}$ , $V_{VCC}$ = 10 V, $R_{DT}$ = 24.9 k $\Omega$ , $V_{GAT2}$ = 0 V, pulsed measurement | 0.3   | 0.5   | 0.8   | Α    |

|                      | Peak sink current          | $V_{FB} = V_{RTN}$ , $V_{VCC} = 10$ V, $R_{DT} = 24.9$ k $\Omega$ , $V_{GAT2} = 10$ V, pulsed measurement  | 0.3   | 0.45  | 0.72  | Α    |

|                      | Rise time <sup>(2)</sup>   | $t_{prr10-90}$ , $C_{GAT2}$ = 0.5 nF , $V_{VCC}$ = 10 V                                                    |       | 15    |       | ns   |

|                      | Fall time <sup>(2)</sup>   | $t_{pff90-10}$ , $C_{GAT2}$ = 0.5 nF , $V_{VCC}$ = 10 V                                                    |       | 15    |       | ns   |

| CLAMPII              | NG FET (CP)                |                                                                                                            |       |       | !     |      |

| R <sub>DS(ON)C</sub> | CP FET on resistance       | I <sub>CP</sub> = 100 mA                                                                                   |       | 1.5   | 3.3   | Ω    |

| CLAMPII              | NG DIODE (CP)              |                                                                                                            |       | -     |       |      |

| V <sub>FCP</sub>     | CP Diode forward voltage   | V <sub>PSRS</sub> = 0 V, I <sub>CP</sub> = 15 mA                                                           | 0.45  | 0.6   | 0.85  | V    |

|                      | CP Leakage current         | V <sub>PSRS</sub> = 0 V, V <sub>CP</sub> = 45 V                                                            |       |       | 20    | μA   |

| AUXILIA              | RY POWER DETECTION (AP     | D, APDO)                                                                                                   |       |       | 1     |      |

| V <sub>APDEN</sub>   | ADD the sealer of the seal | V <sub>APD</sub> rising                                                                                    | 1.42  | 1.5   | 1.58  | V    |

| V <sub>APDH</sub>    | APD threshold voltage      | Hysteresis <sup>(1)</sup>                                                                                  | 0.075 | 0.095 | 0.115 | V    |

|                      | Leakage current            | V <sub>APD</sub> = 5 V                                                                                     |       |       | 1     | μA   |

| V <sub>APL</sub>     | APDO output low voltage    | V <sub>APD</sub> = 5 V, I <sub>APDO</sub> = 1 mA, startup has completed                                    |       | 0.27  | 0.5   | V    |

|                      | Leakage current            | V <sub>APDO</sub> = 10 V                                                                                   |       |       | 1     | μA   |

| THERMA               | L SHUTDOWN                 | '                                                                                                          |       |       |       |      |

|                      | Turnoff temperature        |                                                                                                            | 145   | 155   | 165   | °C   |

|                      | Hysteresis <sup>(2)</sup>  |                                                                                                            |       | 15    |       | °C   |

<sup>(1)</sup> The hysteresis tolerance tracks the rising threshold for a given device.

#### 7.6 Electrical Characteristics PoE

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ;  $-40^{\circ}C \leq T_{J} \leq 125^{\circ}C$ . Positive currents are into pins unless otherwise noted. Typical values are at 25°C.

$V_{VCC-RTN} = 0$  V, all voltages referred to  $V_{VSS}$  unless otherwise noted.

| PARAMETER        |                        | TEST CONDITIONS                                                                | MIN  | TYP  | MAX   | UNIT |

|------------------|------------------------|--------------------------------------------------------------------------------|------|------|-------|------|

| PD DETEC         | TION (DEN)             |                                                                                |      |      |       |      |

|                  | Detection bias current | DEN open, $V_{VDD}$ = 10 V, Not in mark, Measure $I_{VDD} + I_{RTN}$           | 3.5  | 6.9  | 13.9  | μA   |

| I <sub>lkg</sub> | DEN leakage current    | $V_{DEN} = V_{VDD} = 60 \text{ V}$ , Float RTN, Measure $I_{DEN}$              |      | 0.1  | 5     | μA   |

|                  |                        | Measure $I_{VDD} + I_{DEN} + I_{RTN}$ , $V_{VDD} = 1.4 \text{ V}$              | 53.5 | 56.5 | 58.6  | μA   |

|                  | Detection current      | Measure $I_{VDD} + I_{DEN} + I_{RTN}$ , $V_{VDD} = 10 \text{ V}$ , Not in mark | 391  | 398  | 406.2 | μΑ   |

Product Folder Links: TPS23734

<sup>(2)</sup> These parameters are provided for reference only, and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

# 7.6 Electrical Characteristics PoE (continued)

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ;  $-40^{\circ}C \leq T_{J} \leq$  125°C. Positive currents are into pins unless otherwise noted. Typical values are at 25°C.

$V_{VCC-RTN}$  = 0 V, all voltages referred to  $V_{VSS}$  unless otherwise noted.

| PARAMETER            |                                                   | TEST CONDITIONS                                                                              |                                                                                                               | MIN  | TYP   | MAX  | UNIT |

|----------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| V <sub>PD_DIS</sub>  | Hotswap disable threshold                         | DEN falling                                                                                  |                                                                                                               | 3    | 4     | 5    | V    |

| PD CLAS              | SIFICATION (CLS)                                  |                                                                                              |                                                                                                               |      |       |      |      |

|                      |                                                   | R <sub>CLS</sub> = 806 Ω                                                                     | 13 V $\leq$ V <sub>DD</sub> $\leq$ 21 V,<br>Measure I <sub>VDD</sub> + I <sub>DEN</sub> +<br>I <sub>RTN</sub> | 1.9  | 2.5   | 2.9  | mA   |

|                      |                                                   | R <sub>CLS</sub> = 130 Ω                                                                     | 13 V $\leq$ V <sub>DD</sub> $\leq$ 21 V,<br>Measure I <sub>VDD</sub> + I <sub>DEN</sub> +<br>I <sub>RTN</sub> | 9.9  | 10.6  | 11.3 | mA   |

| I <sub>CLS</sub>     | Classification signature current                  | R <sub>CLS</sub> = 69.8 Ω                                                                    | 13 V $\leq$ V <sub>DD</sub> $\leq$ 21 V,<br>Measure I <sub>VDD</sub> + I <sub>DEN</sub> +<br>I <sub>RTN</sub> | 17.6 | 18.6  | 19.4 | mA   |

|                      |                                                   | R <sub>CLS</sub> = 46.4 Ω                                                                    | 13 V $\leq$ V <sub>DD</sub> $\leq$ 21 V,<br>Measure I <sub>VDD</sub> + I <sub>DEN</sub> +<br>I <sub>RTN</sub> | 26.5 | 27.9  | 29.3 | mA   |

|                      |                                                   | R <sub>CLS</sub> = 32 Ω                                                                      | 13 V $\leq$ V <sub>DD</sub> $\leq$ 21 V,<br>Measure I <sub>VDD</sub> + I <sub>DEN</sub> +<br>I <sub>RTN</sub> | 37.8 | 39.9  | 42   | mA   |

| I <sub>CLS</sub>     | Classification signature current, 3rd class event | R <sub>CLS</sub> = 32 Ω                                                                      | 13 V $\leq$ V <sub>DD</sub> $\leq$ 21 V,<br>Measure I <sub>VDD</sub> + I <sub>DEN</sub> +<br>I <sub>RTN</sub> | 38   | 39.9  | 42   | mA   |

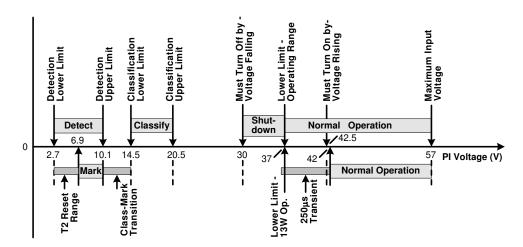

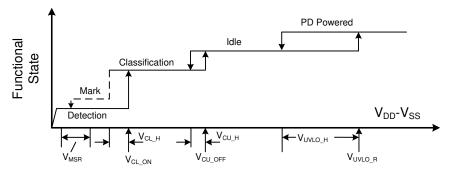

| V <sub>CL_ON</sub>   | Classification regulator lower threshold rising   | V <sub>VDD</sub> rising, I <sub>CLS</sub> ↑                                                  |                                                                                                               | 11.4 | 12.2  | 13   | V    |

| V <sub>CL_H</sub>    | Classification regulator lower threshold          | Hysteresis <sup>(1)</sup>                                                                    | Hysteresis <sup>(1)</sup>                                                                                     |      | 1.2   | 1.6  | V    |

| V <sub>CU_OFF</sub>  | Classification regulator                          | $V_{VDD}$ rising, $I_{CLS} \downarrow$                                                       | / <sub>VDD</sub> rising, I <sub>CLS</sub> ↓                                                                   |      | 22    | 23   | V    |

| V <sub>CU_H</sub>    | upper threshold                                   | Hysteresis <sup>(1)</sup>                                                                    |                                                                                                               | 0.5  | 0.77  | 1    | V    |

| V <sub>MSR</sub>     | Mark state reset threshold                        | V <sub>VDD</sub> falling                                                                     |                                                                                                               | 3    | 3.9   | 5    | V    |

|                      | Mark state resistance                             | 2-point measuremen                                                                           | nt at 5 V and 10.1 V                                                                                          | 6    | 10    | 12   | kΩ   |

| likg                 | Leakage current                                   | $V_{VDD}$ = 60 V, $V_{CLS}$ = $I_{CLS}$                                                      | 0 V, V <sub>DEN</sub> = V <sub>VSS</sub> , Measure                                                            |      |       | 1    | μΑ   |

| t <sub>LCF_PD</sub>  | Long first class event timing                     | Class 1st event time duration for new MPS                                                    |                                                                                                               | 76   | 81.5  | 87   | ms   |

| RTN (PAS             | S DEVICE)                                         |                                                                                              |                                                                                                               |      |       |      |      |

|                      | ON-resistance                                     |                                                                                              |                                                                                                               |      | 0.3   | 0.55 | Ω    |

| LIM                  | Current limit                                     | V <sub>RTN</sub> = 1.5 V, pulsed measurement                                                 |                                                                                                               | 0.75 | 0.925 | 1.1  | Α    |

| IRSH                 | inrush current limit                              | $V_{RTN}$ = 2 V, $V_{VDD}$ : 20 V $\rightarrow$ 48 V, measure $I_{RTN}$ , pulsed measurement |                                                                                                               | 100  | 140   | 180  | mA   |

|                      | Inrush current limit with nonstandard UVLO        |                                                                                              |                                                                                                               | 100  | 140   | 180  | mA   |

|                      | Inrush termination                                | Percentage of inrust                                                                         | n current.                                                                                                    | 80%  | 90%   | 99%  |      |

| t <sub>INR_DEL</sub> | iniusii terriliiatiori                            | Inrush delay                                                                                 |                                                                                                               | 80   | 84    | 88   | ms   |

|                      | Foldback voltage threshold                        | V <sub>RTN</sub> rising                                                                      |                                                                                                               | 13.5 | 14.8  | 16.1 | V    |

# 7.6 Electrical Characteristics PoE (continued)

Unless otherwise noted,  $V_{VDD}$  = 48 V;  $R_{DEN}$  = 25.5 k $\Omega$ ;  $R_{FRS}$  = 60.4 k $\Omega$ ;  $R_{I\_STP}$  = 499 k $\Omega$ ; CLS, T2P, APDO, and PSRS open; CS, EA\_DIS, APD, EMPS, AGND and GND connected to RTN; FB, LINEUV, DT and DTHR connected to VB  $C_{VB}$  =  $C_{VBG}$  = 0.1  $\mu$ F;  $C_{VCC}$  = 1  $\mu$ F;  $C_{SST}$  = 0.047  $\mu$ F;  $R_{REF}$  = 49.9 k $\Omega$ ;  $-40^{\circ}C \leq T_{J} \leq 125^{\circ}C$ . Positive currents are into pins unless otherwise noted. Typical values are at 25°C.

$V_{VCC-RTN}$  = 0 V, all voltages referred to  $V_{VSS}$  unless otherwise noted.

|                      | PARAMETER                                       | TEST CO                                                                                              | NDITIONS                          | MIN   | TYP   | MAX   | UNIT |

|----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------|-------|-------|-------|------|

|                      | Foldback deglitch time                          | V <sub>RTN</sub> rising to when curre<br>inrush current limit. This<br>operating condition or du     | applies in normal                 | 1.5   | 1.8   | 2.1   | ms   |

|                      | Leakage current                                 | $V_{VDD} = V_{RTN} = 100 \text{ V}, V_{D}$                                                           | <sub>DEN</sub> = V <sub>VSS</sub> |       |       | 70    | μA   |

| PSE TYPE             | INDICATION (T2P)                                |                                                                                                      |                                   |       |       | '     |      |

|                      | Output low voltage                              | I <sub>T2P</sub> = 1 mA, after 2- or 3 startup has completed, V                                      |                                   |       | 0.27  | 0.5   | V    |

|                      | Leakage current                                 | V <sub>T2P-RTN</sub> = 10 V, V <sub>RTN</sub> =                                                      | 0 V                               |       |       | 1     | μA   |

| PD INPUT             | SUPPLY (VDD)                                    |                                                                                                      |                                   |       |       |       |      |

| $V_{UVLO\_R}$        | Undervoltage lockout threshold                  | V <sub>VDD</sub> rising                                                                              |                                   | 35.8  | 37.6  | 39.5  | V    |

| V <sub>UVLO_F</sub>  | Undervoltage lockout threshold                  | V <sub>VDD</sub> falling                                                                             |                                   | 30.5  | 32    | 33.6  | V    |

| V <sub>UVLO_H</sub>  | Undervoltage lockout threshold                  | Hysteresis (1)                                                                                       |                                   | 5.7   | 6.0   | 6.3   | V    |

| I <sub>VDD_ON</sub>  | Operating current                               | 40 V ≤ V <sub>VDD</sub> ≤ 60 V, Startup completed, V <sub>VCC</sub> = 10 V, Measure I <sub>VDD</sub> |                                   |       | 650   | 1040  | μΑ   |

| I <sub>VDD_OFF</sub> | Off-state current                               | RTN, GND and VCC open, V <sub>VDD</sub> = 30 V, Measure I <sub>VDD</sub>                             |                                   |       |       | 730   | μΑ   |

| MPS                  |                                                 |                                                                                                      |                                   |       |       |       |      |

| I <sub>MPSL</sub>    | MPS total VSS current for Type 1-2 PSE          | EMPS open, inrush delay has completed, 0 mA ≤<br>I <sub>RTN</sub> ≤ 10 mA, measure I <sub>VSS</sub>  |                                   | 10    | 12.5  | 15.5  | mA   |

| I <sub>MPSH</sub>    | MPS total VSS current for Type 3-4 PSE          | EMPS open, inrush dela<br>I <sub>RTN</sub> ≤ 16 mA, measure I                                        | y has completed, 0 mA ≤<br>vss    | 16.25 | 19    | 21.5  | mA   |

|                      |                                                 | MPS pulsed current duty-cycle                                                                        | EMPS open                         | 26.2% | 26.6% | 26.9% |      |

| t <sub>MPSL</sub>    | MPS pulsed mode duty cycle for Type 1-2 PSE     | MPS pulsed current ON time                                                                           | EMPS open                         | 76    | 81.5  | 87    | ms   |

|                      |                                                 | MPS pulsed current OFF time                                                                          | EMPS open                         |       | 225   | 245   | ms   |

|                      |                                                 | MPS pulsed current duty-cycle, no pulse stretching                                                   | EMPS open                         | 2.9%  | 3.0%  | 3.1%  |      |

|                      | MPS pulsed mode duty-<br>cycle for Type 3-4 PSE | MPS pulsed current ON time, no pulse stretching                                                      | EMPS open                         | 7.2   | 7.7   | 8.1   | ms   |

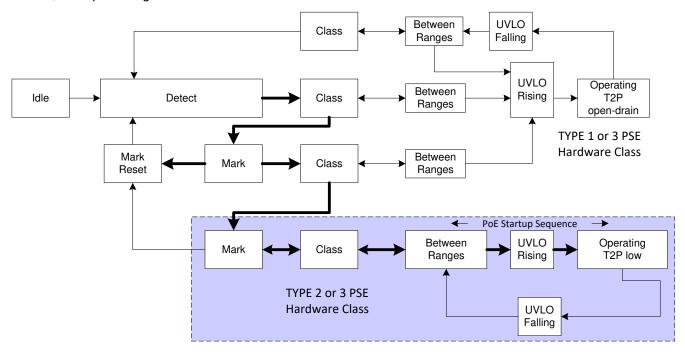

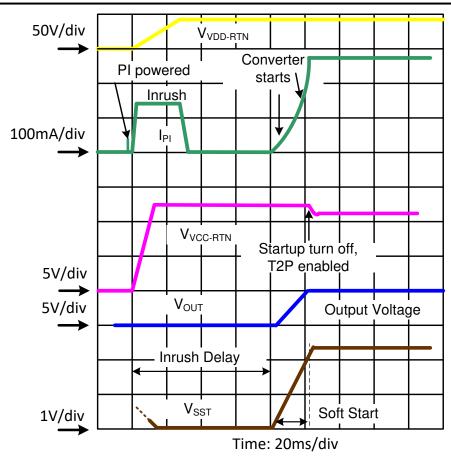

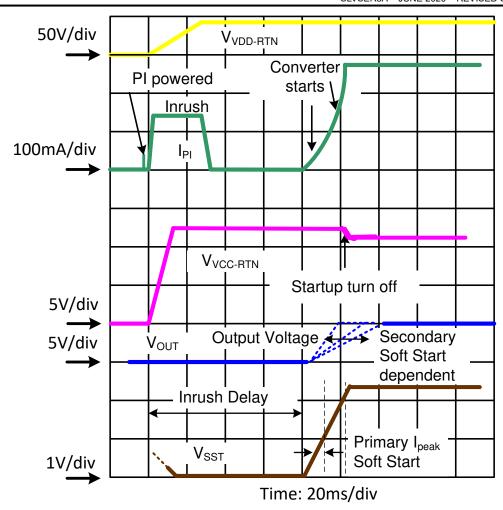

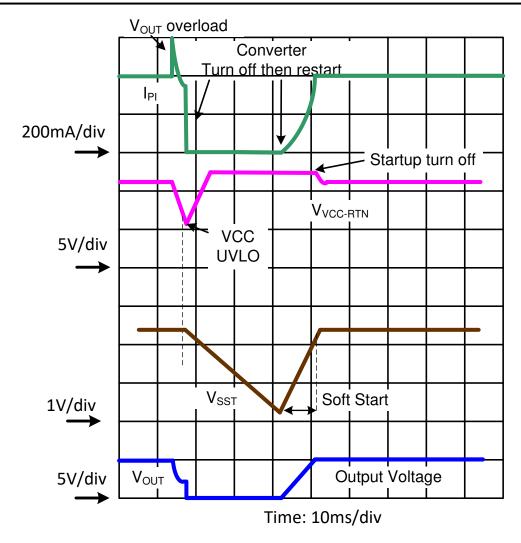

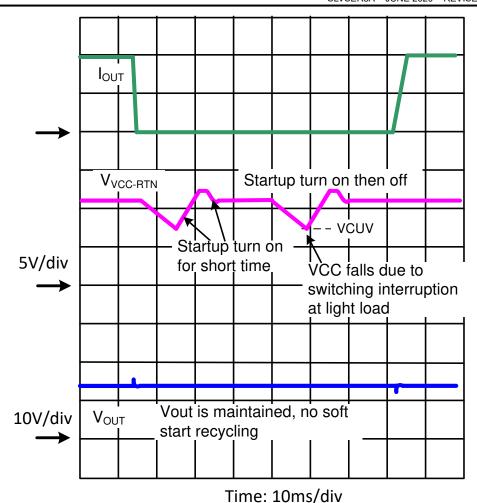

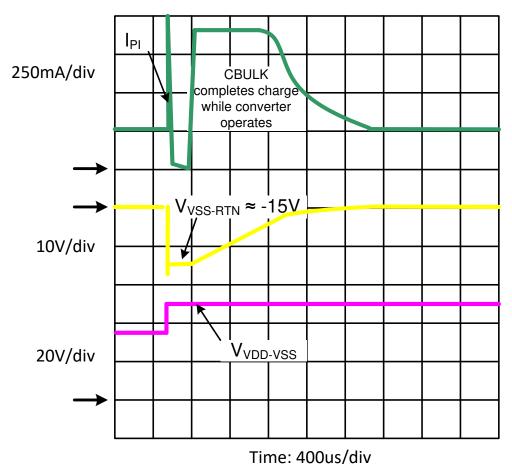

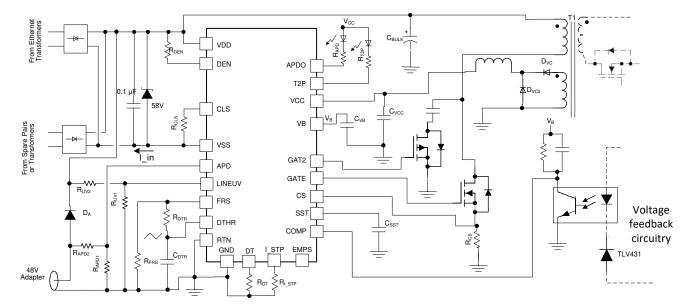

|                      |                                                 | MPS pulsed current<br>OFF time                                                                       | EMPS open                         | 238   | 250   | 265   | ms   |