# 互补型开关场效应晶体管 (FET) 驱动器

查询样品: UC1715-SP

#### 特性

- 单输入(脉宽调制 (PWM) 和晶体管-晶体管逻辑电路 (TTL) 兼容)

- 高电流功率 FET 驱动器,

1A 拉电流 / 2A 灌电流

- 辅助输出 FET 驱动器,0.5A 拉电流 / 1A 灌电流

- 电源与独立可编程辅助输出间的时间延迟范围 **50ns** 至 **700ns**

- 针对每个输出可单独配置时间延迟或真正零电压运行

- 开关频率达到 1MHz

- 典型值为 50ns 的传播延迟

- ENBL 引脚激活 220µA 睡眠模式

- 睡眠模式中电源输出低电平有效

- 同步整流器驱动器

#### 说明

UC1715 是一款被设计成为互补型开关提供驱动波形的高速驱动器。 互补型开关配置通常用于同步整流电路和有源钳位/复位电路,它可提供零电压切换。 为了便捷软开关转换,这个驱动器提供两个输出波形间的独立可编程延迟。 此延迟引脚还具有真正零电压感测功能,这个功能可在采用零电压时实现相应开关的立即激活。 这个器件的运行需要一个 PWM 类型输入,而且此器件可与常见的 PWM 控制器对接。

#### ORDERING INFORMATION(1)

| TJ             | PACKAGE | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|---------|-----------------------|------------------|

| –55°C to 125°C | CFP (W) | 5962-0052102VFA       | 5962-0052102VFA  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ZHCSAU7 -MAY 2013

## **DEVICE INFORMATION**

### **PIN FUNCTIONS**

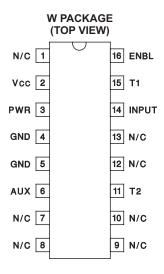

| PIN             |                              |     | PERCEIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME            | NO.                          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| N/C             | 1, 7, 8,<br>9, 10,<br>12, 13 | -   | N/C pins are not bonded out. External connections will not affect device functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| V <sub>CC</sub> | 2                            | ı   | The $V_{CC}$ input range is from 7 V to 20 V. This pin should be bypassed with a capacitor to GND consistent with peak load current demands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| PWR             | 3                            | 0   | The PWR output waits for the T1 delay after the INPUT's rising edge before switching on, but switches off immediately at INPUT's falling edge (neglecting propagation delays). This output is capable of sourcing 1-A and sinking 2-A of peak gate drive current. PWR output includes a passive, self-biased circuit which holds this pin active low, when ENBL ≥ 0.8 V regardless of VCC's voltage.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| GND             | 4, 5                         | -   | This is the reference pin for all input voltages and the return point for all device currents. It carries the full peak sinking current from the outputs. Any tendency for the outputs to ring below GND voltage must be damped or clamped such that GND remains the most negative potential.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| AUX             | 6                            |     | The AUX switches immediately at INPUT's rising edge but waits through the T2 delay after INPUT's falling edge before switching. AUX is capable of sourcing 0.5-A and sinking 1-A of drive current. During sleep mode, AUX is inactive with a high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

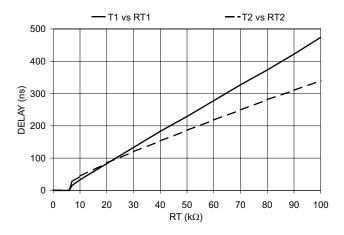

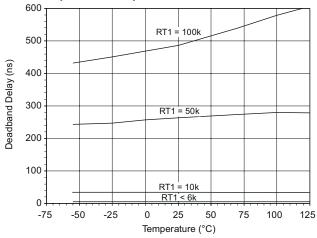

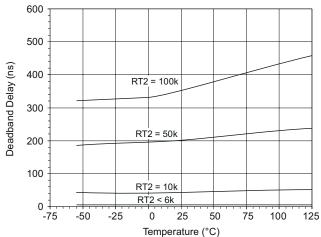

| T2              | 11                           |     | This pin functions in the same way as T1 but controls the time delay between PWR turn-off and activation of the AUX switch.  The resistor on this pin sets the charging current on internal timing capacitors to provide independent time control. The nominal voltage level at this pin is 3 V and the current is internally limited to 1 mA. The total delay from INPUT to output includes a propagation delay in addition to the programmable timer but since the propagation delays are approximately equal, the relative time delay between the two outputs can be assumed to be solely a function of the programmed delays. The relationship of the time delay vs. RT is shown in the Typical Characteristics curves. |  |  |  |  |  |

| INPUT           | 14                           | I   | The input switches at TTL logic levels (approximately 1.4 V) but the allowable range is from 0 V to 20 V, allowing direct connection to most common IC PWM controller outputs. The rising edge immediately switches the AUX output, and initiates a timing delay, T1, before switching on the PWR output. Similarly, the INPUT falling edge immediately turns off the PWR output and initiates a timing delay, T2, before switching the AUX output.  It should be noted that if the input signal comes from a controller with FET drive capability, this signal provides another option. INPUT and PWR provide a delay only at the leading edge while INPUT and AUX provide the delay at the trailing edge.                 |  |  |  |  |  |

| T1              | 15                           |     | A resistor to ground programs the time delay between AUX switch turn-off and PWR turn-on. The resistor on this pin sets the charging current on internal timing capacitors to provide independent time control. The nominal voltage level at this pin is 3 V and the current is internally limited to 1 mA. The total delay from INPUT to output includes a propagation delay in addition to the programmable timer but since the propagation delays are approximately equal, the relative time delay between the two outputs can be assumed to be solely a function of the programmed delays. The relationship of the time delay vs. RT is shown in the Typical Characteristics curves.                                    |  |  |  |  |  |

| ENBL            | 16                           | I   | The ENBL input switches at TTL logic levels (approximately 1.2 V), and its input range is from 0 V to 20 V. The ENBL input will place the device into sleep mode when it is a logical low. The current into VCC during the sleep mode is typically 220 $\mu$ A.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

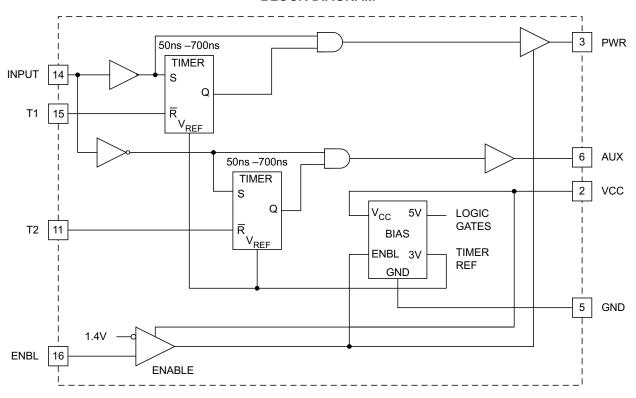

#### **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS(1) (2)

over operating free-air temperature range (unless otherwise noted)

| $V_{CC}$          | Supply voltage                                   | 20 V                |         |

|-------------------|--------------------------------------------------|---------------------|---------|

|                   | Dawes drives                                     | Continuous          | -100 mA |

|                   | Power driver                                     | Peak <sup>(3)</sup> | -1 A    |

| I <sub>OH</sub>   | A. william a deitam                              | Continuous          | -100 mA |

|                   | Auxiliary driver                                 | Peak <sup>(3)</sup> | -500 mA |

|                   | Power driver                                     | Continuous          | 100 mA  |

|                   | Power driver                                     | Peak <sup>(3)</sup> | 2 A     |

| I <sub>OL</sub>   | A. william a deitam                              | Continuous          | 100 mA  |

|                   | Auxiliary driver                                 | Peak <sup>(3)</sup> | 1 A     |

| $V_{I}$           | Input voltage range (INPUT, ENBL)                | -0.3 V to 20 V      |         |

| $T_{J}$           | Maximum operating junction temperature           | 150°C               |         |

| T <sub>stg</sub>  | Storage temperature range                        | −65°C to 150°C      |         |

| T <sub>lead</sub> | Maximum lead temperature (soldering, 10 seconds) | 300°C               |         |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltages are with respect to ground. Currents are positive into, negative out of the specified terminal.

<sup>(3)</sup> RMS drive current on any pin to be restricted to 672 mA.

ZHCSAU7 -MAY 2013 www.ti.com.cn

### THERMAL INFORMATION

|               | (4)                                                 | UC1715-SP |       |

|---------------|-----------------------------------------------------|-----------|-------|

|               | THERMAL METRIC <sup>(1)</sup>                       | W         | UNITS |

|               |                                                     | 16 PINS   |       |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance (2)          | 72.9      |       |

| $\theta_{JC}$ | Junction-to-case thermal resistance (3)             | 8.25      | °C/W  |

| $\theta_{JB}$ | Junction-to-board thermal resistance <sup>(4)</sup> | 43.4      |       |

- (1) 有关传统和新的热 度量的更多信息,请参阅*IC 封装热度量*应用报告, SPRA953。 (2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的指定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然 对流条件下的结至环 境热阻。

- 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但 可在 ANSI SEMI 标准 G30-88 中能找到内容接近的说明。

- (4) 按照 JESD51-8 中的说明,通过 在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结板热阻。

## **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 15 V, ENBL  $\geq$  2 V,  $R_T1$  = 100 k $\Omega$  from T1 to GND,  $R_T2$  = 100 k $\Omega$  from T2 to GND,  $T_A$  =  $T_J$  = -55°C to 125°C (unless otherwise noted)

| PARAMETER                                                   | TEST CONDITIONS                                                                | MIN TYP | MAX  | UNIT |

|-------------------------------------------------------------|--------------------------------------------------------------------------------|---------|------|------|

| Overall                                                     |                                                                                | ·       |      |      |

| V <sub>CC</sub>                                             |                                                                                | 7       | 18   | V    |

| I <sub>CC</sub> , nominal                                   | ENBL = 3 V                                                                     |         | 25   | mA   |

| I <sub>CC</sub> , sleep mode                                | ENBL = 0.8 V                                                                   |         | 300  | μA   |

| Power Driver (PWR)                                          |                                                                                |         |      |      |

| Pre turn-on PWR output, low                                 | $V_{CC} = 0 \text{ V}, I_{OUT} = 10 \text{ mA}, \text{ENBL} \le 0.8 \text{ V}$ |         | 2    | V    |

| DMD + 11 + 04 )                                             | INPUT = 0.8 V, I <sub>OUT</sub> = 40 mA                                        |         | 1    |      |

| PWR output low, sat. (V <sub>PWR</sub> )                    | INPUT = 0.8 V, I <sub>OUT</sub> = 100 mA                                       |         | 1.5  | V    |

| DWD                                                         | INPUT = 3 V, I <sub>OUT</sub> = −40 mA                                         |         | 3    | .,   |

| PWR output high, sat. (V <sub>CC</sub> - V <sub>PWR</sub> ) | INPUT = 3 V, I <sub>OUT</sub> = −100 mA                                        |         | 3    | V    |

| Rise time                                                   | C <sub>L</sub> = 2200 pF                                                       |         | 60   | ns   |

| Fall time                                                   | C <sub>L</sub> = 2200 pF                                                       |         | 60   | ns   |

| T1 delay, AUX to PWR (1)                                    | INPUT rising edge, $R_T 1 = 10 \text{ k}\Omega$ , see (2)                      | 45      | 200  | ns   |

| T1 delay, AUX to PWR <sup>(1)</sup>                         | INPUT rising edge, $R_T 1 = 100 \text{ k}\Omega$ , see <sup>(2)</sup>          | 250     | 1300 | ns   |

| PWR prop delay                                              | INPUT falling edge, 50%, see (3)                                               |         | 300  | ns   |

| Auxiliary Driver (AUX)                                      |                                                                                |         |      |      |

| AUX pre turn-on AUX output low (V <sub>PAUX</sub> )         | V <sub>CC</sub> = 0 V, ENBL ≤ 0.8 V, I <sub>OUT</sub> = 10 mA                  |         | 2    | V    |

|                                                             | V <sub>IN</sub> = 3 V, I <sub>OUT</sub> = 40 mA                                |         | 1    |      |

| AUX output low, sat. (V <sub>AUX</sub> )                    | V <sub>IN</sub> = 3 V, I <sub>OUT</sub> = 100 mA                               |         | 1.5  | V    |

|                                                             | V <sub>IN</sub> = 0.8 V, I <sub>OUT</sub> = -40 mA                             |         | 3    |      |

| AUX output high, sat. $(V_{CC} - V_{AUX})$                  | V <sub>IN</sub> = 0.8 V, I <sub>OUT</sub> = -100 mA                            |         | 3    | V    |

| Rise time                                                   | C <sub>1</sub> = 2200 pF                                                       |         | 60   | ns   |

| Fall time                                                   | C <sub>1</sub> = 2200 pF                                                       |         | 60   | ns   |

| T2 delay, PWR to AUX <sup>(1)</sup>                         | INPUT falling edge, $R_T 2 = 10 \text{ k}\Omega$ , see <sup>(2)</sup>          | 45      | 130  | ns   |

| T2 delay, PWR to AUX <sup>(1)</sup>                         | INPUT falling edge, $R_T 2 = 100 \text{ k}\Omega$ , see <sup>(2)</sup>         | 200     | 700  | ns   |

| AUX prop delay                                              | INPUT rising edge, 50%, see (3)                                                |         | 185  | ns   |

| Enable (ENBL)                                               |                                                                                |         |      |      |

| Input threshold                                             |                                                                                |         | 2.8  | V    |

| Input current, I <sub>IH</sub>                              | ENBL = 15 V                                                                    | -10     | 10   | μA   |

| Input current, I <sub>II</sub>                              | ENBL = 0 V                                                                     | -15     | 15   | μA   |

| T1                                                          |                                                                                |         |      | la   |

| Current limit                                               | T1 = 0 V                                                                       | -2      | -0.5 | mA   |

| Nominal voltage at T1                                       |                                                                                | 2.7     | 3.3  | V    |

| Minimum T1 delay                                            | T1 = 2.5 V, see (2)                                                            | 2       | 80   | ns   |

| T2                                                          | 11 = 2.5 V, 666                                                                |         |      | 110  |

| Current limit                                               | T2 = 0 V                                                                       | -2      | -0.5 | mA   |

| Nominal voltage at T12                                      |                                                                                | 2.7     | 3.3  | V    |

| Minimum T2 delay                                            | T2 = 2.5 V, see <sup>(2)</sup>                                                 | 2.1     | 80   | ns   |

| Input (INPUT)                                               | 12 - 2.0 v, 300                                                                |         | 00   | 110  |

| Input (INPOT)                                               |                                                                                |         | 2.8  | V    |

| •                                                           | ENBL = 15 V                                                                    | 10      | 10   |      |

| Input current, I <sub>IH</sub>                              |                                                                                | -10     |      | μΑ   |

| Input current, I <sub>IL</sub>                              | ENBL = 0 V                                                                     | -20     | 20   | μΑ   |

<sup>(1)</sup> The parameter is guaranteed to the limit specified by characterization, but not production tested.

<sup>(2)</sup> T1 and T2 delay is defined as the time between the 50% transition point of AUX (PWR) and the 50% transition point of PWR (AUX) with no capacitive load on either output.

<sup>(3)</sup> Propagation delays are measured from the 50% point of the input signal to the 50% point of the output signal's transition with no load on outputs.

ZHCSAU7 -MAY 2013 www.ti.com.cn

#### TYPICAL CHARACTERISTICS

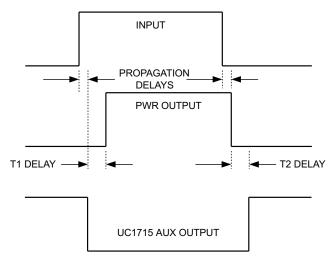

- A. T1 delay is defined from the 50% point of the transition edge of AUX to the 10% of the rising edge of PWR. T2 delay is defined from the 90% of the falling edge of PWR to the 50% point of the transition edge of AUX.

- B. Propagation delay times are measured from the 50% point of the input signal to the 10% point of the output signal's transition with no load on outputs.

Figure 1. Time Relationships

Figure 2. T1 Delay, T2 Delay vs. R<sub>T</sub>

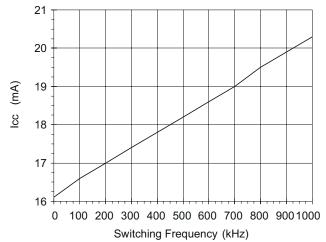

Figure 3.  $I_{CC}$  vs Switching Frequency With No Load and 50% Duty Cycle  $R_T1=R_T2=50~k\Omega$

## **TYPICAL CHARACTERISTICS (continued)**

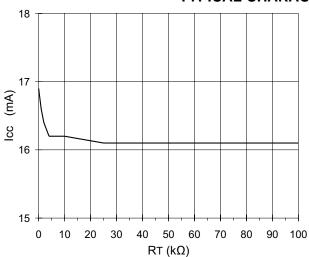

Figure 4.  $I_{CC}$  vs  $R_T$  With Opposite  $R_T$  = 50 k $\Omega$

Figure 5. T1 Deadband vs. Temperature AUX to PWR

Figure 6. T2 Deadband vs. Temperature PWR to AUX

ZHCSAU7 -MAY 2013 www.ti.com.cn

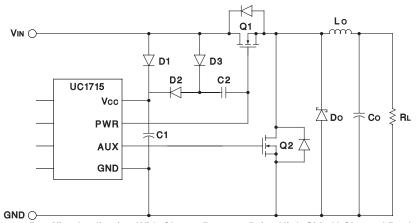

#### **TYPICAL APPLICATIONS**

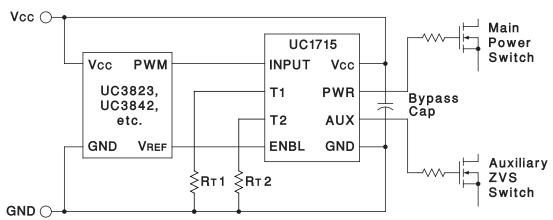

Figure 7. Typical Application With Timed Delays

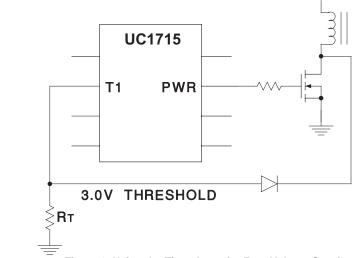

Figure 8. Using the Timer Input for Zero-Voltage Sensing

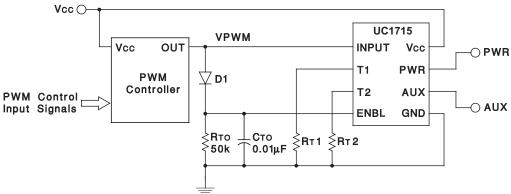

Figure 9. Self-Actuated Sleep Mode With Absence of Input PWM Signal. Wake Up Occurs With First Pulse While Turn-Off is Determined by the (RTO CTO) Time Constant

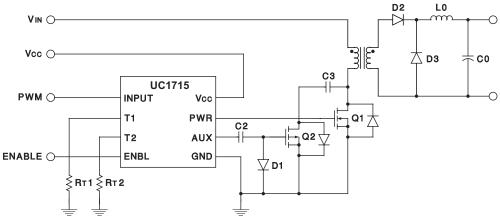

## **TYPICAL APPLICATIONS (continued)**

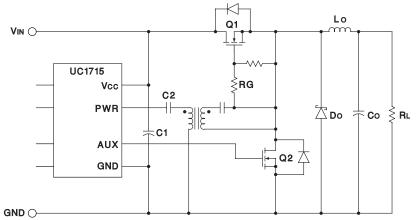

Figure 10. Using the UC1715 as a Complementary Synchronous Rectifier Switch Driver With N-Channel FETs

Figure 11. Synchronous Rectifier Application With Charge Pump to Drive High-Side N-Channel Buck Switch. V<sub>IN</sub> is Limited to 10 V as V<sub>CC</sub> Will Rise to Approximately 2V<sub>IN</sub>

Figure 12. Typical Forward Converter Topology With Active Reset Provided by the UC1714 Driving N-channel switch (Q1) and P-Channel Auxilliary Switch (Q2)

**STRUMENTS**

ZHCSAU7 -MAY 2013 www.ti.com.cn

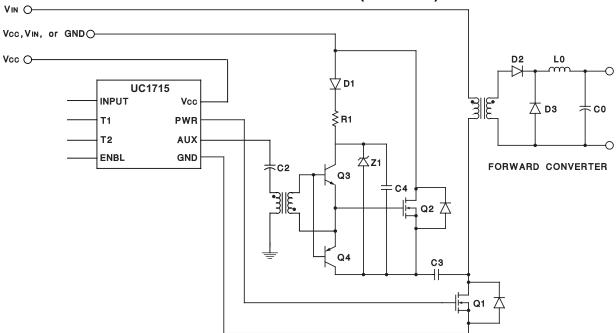

## **TYPICAL APPLICATIONS (continued)**

Figure 13. Using N-Channel Active Reset Switch With Floating Drive Command

### PACKAGE OPTION ADDENDUM

11-Jan-2021

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5)           | Samples |

|------------------|--------|--------------|--------------------|------|----------------|---------------------|-------------------------------|--------------------|--------------|-----------------------------------|---------|

| 5962-0052102VFA  | ACTIVE | CFP          | W                  | 16   | 1              | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type | -55 to 125   | 5962-0052102VF<br>A<br>UC1715W-SP | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

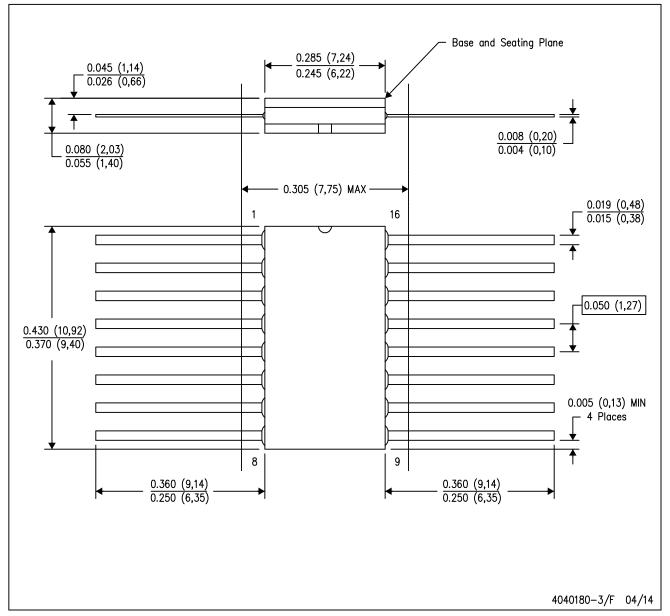

# W (R-GDFP-F16)

## CERAMIC DUAL FLATPACK

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL STD 1835 GDFP2-F16

### 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司