ADS5463-SP SGLS378G –MARCH 2008–REVISED OCTOBER 2017

# ADS5463-SP Class V, 12-Bit, 500-MSPS Analog-to-Digital Converter

#### 1 Features

- 500-MSPS Sample Rate

- Available With Radiation Hardness Specified (RHA) - Total Ionizing Dose 100 krad(Si), ELDRS Free 100 krad(Si)

- 12-Bit Resolution, 10-Bits Effective Number of Bits (ENOB)

- SNR > 64.5 dBFS at 450 MHz and 500 MSPS

- SFDR > 64.0 dBc at 450 MHz and 500 MSPS

- 2.2-V<sub>PP</sub> Differential Input Voltage

- LVDS-Compatible Outputs

- Total Power Dissipation: 2.2 W

- Offset Binary Output Format

- Output Data Transitions on the Rising and Falling Edges of a Half-Rate Output Clock

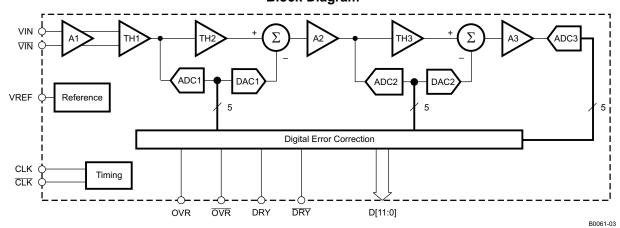

- On-Chip Analog Buffer, Track and Hold, and Reference Circuit

- Available in a 84-Pin Ceramic Nonconductive Tie-Bar Package (HFG)

- Military Temperature Range (–55°C to 125°C T<sub>case</sub>)

## 2 Applications

- Test and Measurement Instrumentation

- Software-Defined Radio

- Data Acquisition

- Power Amplifier Linearization

- Communication Instrumentation

- Radar

- Engineering Evaluation (/EM) Samples are Available<sup>(1)</sup>

### 3 Description

The ADS5463 is a 12-bit, 500-MSPS analog-to-digital converter (ADC) that operates from both a 5-V supply and 3.3-V supply, while providing LVDS-compatible digital outputs from the 3.3-V supply. The ADS5463 input buffer isolates the internal switching of the onboard track and hold (T and H) from disturbing the signal source. An internal reference generator is also provided to simplify the system design further. The ADS5463 has outstanding low noise and linearity over input frequency.

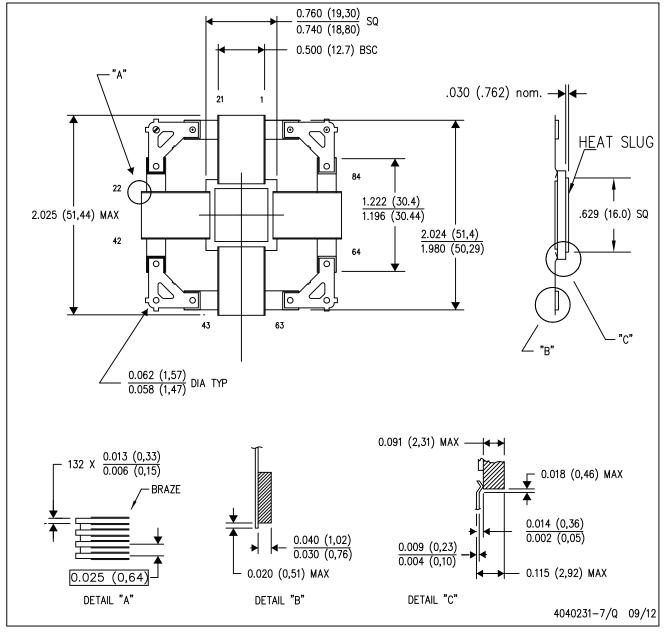

The ADS5463 is available in a 84-pin ceramic nonconductive tie-bar package (HFG). The ADS5463 is built on state-of-the-art Texas Instruments complementary bipolar process (BiCom3X) and is specified over the full military temperature range ( $-55^{\circ}$ C to  $125^{\circ}$ C  $T_{case}$ ).

### Device Information<sup>(2)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)     |

|-------------|----------|---------------------|

| ADS5463-SP  | CFP (84) | 16.51 mm × 16.51 mm |

- (1) These units are intended for engineering evaluation only. They are processed to a non-compliant flow (for example, no burn-in, and so forth) and are tested to temperature rating of 25°C only. These units are not suitable for qualification, production, radiation testing or flight use. Parts are not warranted for performance on full MIL specified temperature range of -55°C to 125°C or operating life.

- (2) For all available packages, see the orderable addendum at the end of the data sheet.

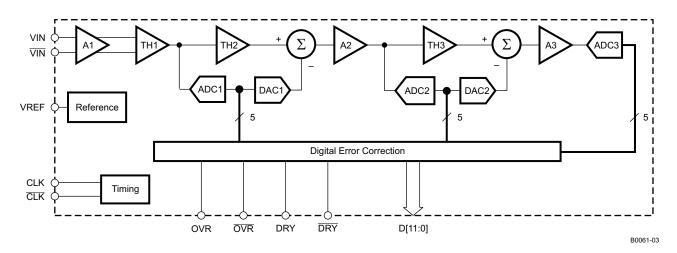

#### **Block Diagram**

A

**Page**

#### **Table of Contents**

| 1 | Features 1                                   |    | 7.1 Overview                                        | 21   |

|---|----------------------------------------------|----|-----------------------------------------------------|------|

| 2 | Applications 1                               |    | 7.2 Functional Block Diagram                        | 21   |

| 3 | Description 1                                |    | 7.3 Feature Description                             | 21   |

| 4 | Revision History2                            |    | 7.4 Device Functional Modes                         | 21   |

| 5 | Pin Configuration and Functions              | 8  | Application and Implementation                      | 22   |

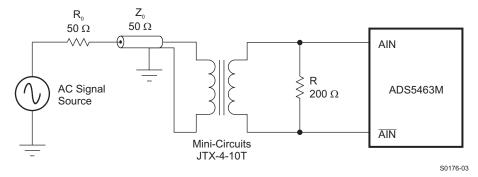

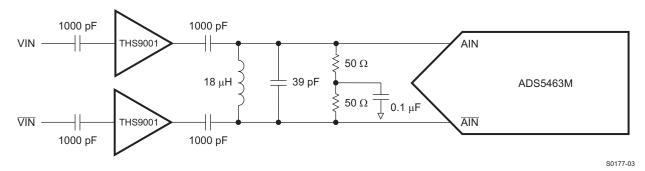

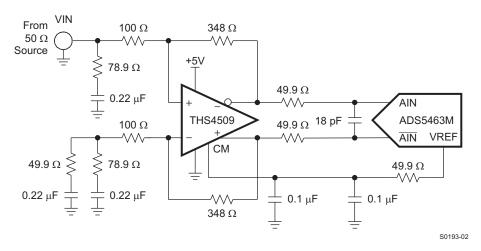

| 6 | Specifications4                              |    | 8.1 Application Information                         | 22   |

| U | 6.1 Absolute Maximum Ratings                 |    | 8.2 Typical Application                             | 25   |

|   | 6.2 ESD Ratings                              | 9  | Power Supply Recommendations                        | 27   |

|   | 6.3 Recommended Operating Conditions         | 10 | Layout                                              | . 28 |

|   | 6.4 Thermal Information                      |    | 10.1 Layout Guidelines                              |      |

|   | 6.5 Electrical Characteristics: ADS5463-RHA  |    | 10.2 Layout Example                                 |      |

|   | 6.6 Electrical Characteristics: ADS5463-RHA  | 11 | Device and Documentation Support                    | 29   |

|   | 6.7 Electrical Characteristics: ADS5463-RHA  |    | 11.1 Device Support                                 |      |

|   | 6.8 Electrical Characteristics: ADS5463-SP11 |    | 11.2 Receiving Notification of Documentation Update |      |

|   | 6.9 Electrical Characteristics: ADS5463-SP12 |    | 11.3 Community Resources                            | 30   |

|   | 6.10 Electrical Characteristics: ADS5463-SP  |    | 11.4 Trademarks                                     | 30   |

|   | 6.11 Timing Requirements                     |    | 11.5 Electrostatic Discharge Caution                | 30   |

|   | 6.12 Typical Characteristics                 |    | 11.6 Glossary                                       | 30   |

| 7 | Detailed Description                         | 12 | Mechanical, Packaging, and Orderable Information    |      |

### 4 Revision History

Changes from Revision F (November 2015) to Revision G

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| _    |                                                                                                                                                                                                                                                                                                                                          |                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •    | Changed R <sub>0JA</sub> from 24°C/W: to 17.9°C/W in the <i>Thermal Information</i> section                                                                                                                                                                                                                                              | 5              |

| •    | Changed R <sub>0.JC(top)</sub> from 12°C/W: to 3.1°C/W in the <i>Thermal Information</i> section                                                                                                                                                                                                                                         | <mark>5</mark> |

| •    | Changed R <sub>BJB</sub> from 10°C/W: to 6.1°C/W in the <i>Thermal Information</i> section                                                                                                                                                                                                                                               | <mark>5</mark> |

| •    | Added values for $\psi_{JT}$ , $\psi_{JB}$ , and $R_{\theta JC(bot)}$ in the <i>Thermal Information</i> section                                                                                                                                                                                                                          | <u>5</u>       |

| •    | Changed t <sub>DATA</sub> NOM and MAX values in the <i>Timing Requirements</i> section                                                                                                                                                                                                                                                   | 16             |

| •    | Changed t <sub>SKEW</sub> MIN and NOM values in the <i>Timing Requirements</i> section                                                                                                                                                                                                                                                   | 16             |

| •    | Added Receiving Notification of Documentation Updates section to the Device and Documentation Support section                                                                                                                                                                                                                            | 30             |

| _    |                                                                                                                                                                                                                                                                                                                                          |                |

| C    | hanges from Revision E (January 2014) to Revision F                                                                                                                                                                                                                                                                                      | Page           |

| C    | hanges from Revision E (January 2014) to Revision F  Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Machanical Revisation and Orderable Information section. | Page           |

| • CI | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation                                                                                                                                                                                                                            |                |

| •    | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and                                                                                                               |                |

Submit Documentation Feedback

Copyright © 2008–2017, Texas Instruments Incorporated

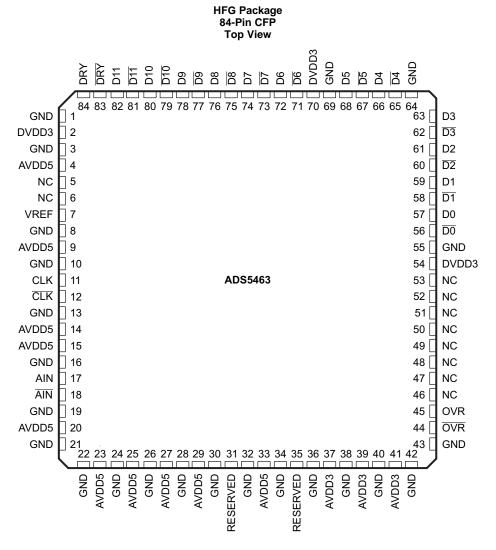

# 5 Pin Configuration and Functions

#### **Pin Functions**

|       | PIN                                                                                                 | DESCRIPTION                                                                                                        |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.                                                                                                 | DESCRIPTION                                                                                                        |  |  |  |

| AIN   | 17                                                                                                  | Differential input signal (positive).                                                                              |  |  |  |

| AIN   | 18                                                                                                  | Differential input signal (negative).                                                                              |  |  |  |

| AVDD5 | 4, 9, 14, 15, 20, 23, 25, 27, 29, 33                                                                | Analog power supply (5 V).                                                                                         |  |  |  |

| AVDD3 | 37, 39, 41                                                                                          | Analog power supply (3.3 V) (Suggestion for 250 MSPS: leave option to connect to 5 V for ADS5440/4 compatibility). |  |  |  |

| DVDD3 | 2, 54, 70                                                                                           | Output driver power supply (3.3 V).                                                                                |  |  |  |

| GND   | 1, 3, 8, 10, 13, 16,<br>19, 21, 22, 24, 26,<br>28, 30, 32, 34, 36,<br>38, 40, 42, 43, 55,<br>64, 69 | Ground.                                                                                                            |  |  |  |

| CLK   | 11                                                                                                  | Differential input clock (positive). Conversion initiated on rising edge.                                          |  |  |  |

| CLK   | 12                                                                                                  | Differential input clock (negative).                                                                               |  |  |  |

Copyright © 2008–2017, Texas Instruments Incorporated

### Pin Functions (continued)

|                                                    | PIN        | DESCRIPTION                                                                                                                                                             |

|----------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                               | NO.        | DESCRIPTION                                                                                                                                                             |

| <del>D0</del> , D0                                 | 56, 57     | LVDS digital output pair, least-significant bit (LSB).                                                                                                                  |

| D1-D3,<br>D1-D3                                    | 58–63      | LVDS digital output pair.                                                                                                                                               |

| <u>D4</u> – <u>D5</u> ,<br><u>D4</u> – <u>D5</u>   | 65–68      | LVDS digital output pairs.                                                                                                                                              |

| <u>D6</u> – <u>D10</u> ,<br><u>D6</u> – <u>D10</u> | 71–80      | LVDS digital output pairs.                                                                                                                                              |

| D11, D11                                           | 81, 82     | LVDS digital output pair, most-significant bit (MSB).                                                                                                                   |

| DRY, DRY                                           | 83, 84     | Data ready LVDS output pair.                                                                                                                                            |

| NC                                                 | 5–6, 46–53 | No connect (5 and 6 should be left floating, 46–53 are possible future bit additions for this pinout and therefore can be connected to a digital bus or left floating). |

| OVR, OVR                                           | 44, 45     | Overrange indicator LVDS output. A logic high signals an analog input in excess of the full-scale range.                                                                |

| RESERVED                                           | 31, 35     | Reserved for possible future control features.                                                                                                                          |

| VREF                                               | 7          | Reference voltage.                                                                                                                                                      |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                                                               |                                           |                                   | MIN  | MAX                            | UNIT |  |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|------|--------------------------------|------|--|

|                                                                                                               | AVDD5 to GND                              |                                   | 6    |                                |      |  |

| Supply voltage                                                                                                | AVDD3 to GND                              |                                   | 5    |                                | V    |  |

|                                                                                                               | DVDD3 to GND                              |                                   | 5    |                                |      |  |

|                                                                                                               |                                           | AC signal                         | -0.3 | (AVDD5 + 0.3)                  |      |  |

| AIN, $\overline{\text{AIN}}$ to $\overline{\text{GND}}^{(2)}$ AIN to $\overline{\overline{\text{AIN}}}^{(2)}$ | Voltage difference between pin and ground | DC signal, T <sub>J</sub> = 105°C | 0.4  | 4.4                            | V    |  |

|                                                                                                               | pin and ground                            | DC signal, T <sub>J</sub> = 125°C | 1.0  | 3.8                            |      |  |

|                                                                                                               |                                           | AC signal                         | -5.2 | 5.2                            |      |  |

| AIN to $\overline{\text{AIN}}^{(2)}$                                                                          | Voltage difference between these pins     | DC signal, T <sub>J</sub> = 105°C | -4   | 4                              | V    |  |

|                                                                                                               | πιεσε μπο                                 | DC signal, T <sub>J</sub> = 125°C | -2.8 | -2.8 2.8<br>-0.3 (AVDD5 + 0.3) |      |  |

| CLK to CLK <sup>(2)</sup> th                                                                                  |                                           | AC signal                         | -0.3 | (AVDD5 + 0.3)                  |      |  |

|                                                                                                               | Voltage difference between pin and ground | DC signal, T <sub>J</sub> = 105°C | 0.1  | 4.7                            | V    |  |

|                                                                                                               | pin and ground                            | DC signal, T <sub>J</sub> = 125°C | 1.1  | 3.7                            |      |  |

|                                                                                                               |                                           | AC signal                         | -3.3 | 3.3                            |      |  |

| CLK to CLK (2)                                                                                                | Voltage difference between these pins     | DC signal, T <sub>J</sub> = 105°C | -3.3 | 3.3                            | V    |  |

|                                                                                                               | tricse piris                              | DC signal, T <sub>J</sub> = 125°C | -2.6 | 2.6                            |      |  |

| Data output to GND <sup>(2)</sup>                                                                             | LVDS digital outputs                      |                                   | -0.3 | (DVDD3 + 0.3)                  | V    |  |

| Characterized case operating temperature, T <sub>C</sub>                                                      |                                           |                                   | -55  | 125                            | °C   |  |

| Maximum junction tempera                                                                                      | ture, T <sub>J</sub>                      |                                   | 150  |                                | °C   |  |

| Storage temperature, T <sub>stg</sub>                                                                         |                                           |                                   | -65  | 150                            | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Valid when supplies are within recommended operating range.

Submit Documentation Feedback

Copyright © 2008–2017, Texas Instruments Incorporated

#### 6.2 ESD Ratings

|                    |                               |                                                                     | VALUE | UNIT |

|--------------------|-------------------------------|---------------------------------------------------------------------|-------|------|

| \/                 | (ESD) Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±3000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge       | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                         | MIN         | NOM | MAX  | UNIT     |

|-----------------|-----------------------------------------|-------------|-----|------|----------|

| SUPPLIE         | S                                       |             |     |      |          |

| AVDD5           | Analog supply voltage                   | 4.75        | 5   | 5.25 | V        |

| AVDD3           | Analog supply voltage                   | 3           | 3.3 | 3.6  | V        |

| DVDD3           | Output driver supply voltage            | 3           | 3.3 | 3.6  | V        |

| ANALOG          | INPUT                                   |             |     |      |          |

|                 | Differential input                      |             | 2.2 |      | $V_{pp}$ |

| V <sub>CM</sub> | Input common mode                       |             | 2.4 |      | V        |

| DIGITAL         | OUTPUT                                  |             |     | ·    |          |

|                 | Maximum differential output load        |             | 10  |      | pF       |

| CLOCK II        | NPUT                                    |             |     |      |          |

|                 | CLK input sample rate (sine wave)       | 20          |     | 500  | MSPS     |

|                 | Clock amplitude, differential sine wave |             | 3   |      | $V_{pp}$ |

| ·               | Clock duty cycle                        |             | 50% |      |          |

| T <sub>c</sub>  | Operating case temperature              | <b>–</b> 55 |     | 125  | °C       |

#### 6.4 Thermal Information<sup>(1)</sup>

|                      |                                              | ADS5463-SP |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(2)</sup>                | HFG (CFP)  | UNIT |

|                      |                                              | 84 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 17.9       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 3.1        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.1        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.4        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 5.6        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.4        | °C/W |

<sup>(1)</sup> This CFP package has built-in vias that electrically and thermally connect the bottom of the die to a pad on the bottom of the package. To efficiently remove heat and provide a low-impedance ground path, a thermal land is required on the surface of the PCB directly underneath the body of the package. During normal surface mount flow solder operations, the heat pad on the underside of the package is soldered to this thermal land creating an efficient thermal path. Normally, the PCB thermal land has a number of thermal vias within it that provide a thermal path to internal copper areas (or to the opposite side of the PCB) that provide for more efficient heat removal. TI typically recommends an 11.9 mm² board-mount thermal pad. This allows maximum area for thermal dissipation, while keeping leads away from the pad area to prevent solder bridging. A sufficient quantity of thermal/electrical vias must be included to keep the device within recommended operating conditions. This pad must be electrically at ground potential.

(2) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: ADS5463-SP

### 6.5 Electrical Characteristics: ADS5463-RHA

Typical values at  $T_C = 25^{\circ}$ C, full temperature range is  $T_{C,MIN} = -55^{\circ}$ C to  $T_{C,MAX} = 125^{\circ}$ C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clock (unless otherwise noted)

| (driiioo           | otnerwise noted)                            |                                                             |                        |       |         |       |          |

|--------------------|---------------------------------------------|-------------------------------------------------------------|------------------------|-------|---------|-------|----------|

|                    | PARAMETER                                   | TEST C                                                      | ONDITIONS              | MIN   | TYP     | MAX   | UNIT     |

| Resoluti           | on                                          |                                                             |                        |       | 12      |       | Bits     |

| ANALO              | G INPUTS                                    |                                                             |                        |       |         |       |          |

|                    | Differential input range                    |                                                             |                        |       | 2.2     |       | $V_{PP}$ |

|                    | Input resistance (dc)                       | Each input to VCM                                           |                        |       | 500     |       | Ω        |

|                    | Input capacitance                           | Each input to ground                                        |                        |       | 2.5     |       | pF       |

|                    | Analog input bandwidth                      |                                                             |                        | 1000  | 2000    |       | MHz      |

| INTERN             | IAL REFERENCE VOLTAG                        | Ε                                                           |                        |       |         |       |          |

| V <sub>REF</sub>   | Reference voltage                           | Full temperature range                                      |                        | 2.38  | 2.4     | 2.42  | V        |

| DYNAM              | IIC ACCURACY                                |                                                             |                        | +     |         | ·     |          |

|                    | No missing codes                            |                                                             |                        |       | Assured |       |          |

| DNL                | Differential linearity error                | f <sub>IN</sub> = 210 MHz                                   | Full temperature range | -0.98 | ±0.95   | 1.2   | LSB      |

| INL                | Integral linearity error                    | f <sub>IN</sub> = 210 MHz                                   | Full temperature range | -3.5  | ±1.5    | 3.5   | LSB      |

|                    | Offset error                                | Full temperature range                                      |                        | -0.5  |         | 0.5   | %FS      |

|                    | Offset temperature coefficient              |                                                             |                        |       | 0.0009  |       | %FS/°C   |

|                    | Gain error                                  | Full temperature range                                      |                        | -5    |         | 5     | %FS      |

|                    | Gain temperature coefficient                |                                                             |                        |       | -0.02   |       | %FS/°C   |

| POWER              | SUPPLY                                      |                                                             |                        |       |         |       |          |

| I <sub>AVDD5</sub> | 5 V analog supply current                   |                                                             |                        |       |         | 345   | mA       |

| I <sub>AVDD3</sub> | 3.3 V analog supply current                 | V <sub>IN</sub> = full scale,<br>f <sub>IN</sub> = 300 MHz, | Full temperature range | 1     | 148     | mA    |          |

| I <sub>DVDD3</sub> | 3.3 V digital supply current(includes LVDS) | F <sub>S</sub> = 500 MSPS                                   |                        |       |         | 88    | mA       |

|                    | Power dissipation                           |                                                             |                        |       |         | 2.450 | W        |

Submit Documentation Feedback

Copyright © 2008–2017, Texas Instruments Incorporated

# 6.6 Electrical Characteristics: ADS5463-RHA

Typical values at  $T_C$  = 25°C, full temperature range is  $T_{C,MIN}$  = -55°C to  $T_{C,MAX}$  = 125°C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clock (unless otherwise noted)

|        | PARAMETER                   | TES                               | ST CONDITIONS          | MIN  | TYP  | MAX | UNIT |

|--------|-----------------------------|-----------------------------------|------------------------|------|------|-----|------|

| DYNAMI | IC AC CHARACTERISTICS       |                                   |                        |      |      | ·   |      |

|        |                             | f <sub>IN</sub> = 10 MHz          |                        |      | 65.4 |     |      |

|        |                             | $f_{\text{IN}} = 70 \text{ MHz}$  | <sub>IN</sub> = 70 MHz |      | 65.3 |     |      |

|        |                             |                                   | $T_C = 25^{\circ}C$    | 60.5 | 65.2 |     |      |

|        |                             | f <sub>IN</sub> = 100 MHz         | $T_C = T_{C,MAX}$      | 60.5 |      |     |      |

|        |                             |                                   | $T_C = T_{C,MIN}$      | 60.5 |      |     |      |

|        |                             |                                   | $T_C = 25^{\circ}C$    | 60   | 65   |     |      |

|        |                             | f <sub>IN</sub> = 210 MHz         | $T_C = T_{C,MAX}$      | 60   |      |     |      |

| SNR    | Signal-to-noise ratio       |                                   | $T_C = T_{C,MIN}$      | 60   |      |     | dBFS |

|        |                             |                                   | $T_C = 25^{\circ}C$    | 58   | 64.9 |     |      |

|        |                             | f <sub>IN</sub> = 300 MHz         | $T_C = T_{C,MAX}$      | 58   |      |     |      |

|        |                             |                                   | $T_C = T_{C,MIN}$      | 58   |      |     |      |

|        |                             | f <sub>IN</sub> = 450 MHz         |                        |      | 64.5 |     |      |

|        |                             | f <sub>IN</sub> = 650 MHz         |                        |      | 63.7 |     |      |

|        |                             | f <sub>IN</sub> = 900 MHz         |                        |      | 62.8 |     |      |

|        |                             | f <sub>IN</sub> = 1.0 GHz         |                        |      | 62.2 |     |      |

|        |                             | f <sub>IN</sub> = 10 MHz          |                        |      | 63.5 |     |      |

|        |                             | $f_{\text{IN}} = 70 \text{ MHz}$  |                        |      | 64.2 |     |      |

|        |                             | f <sub>IN</sub> = 100 MHz         | $T_C = 25^{\circ}C$    | 57.9 | 65   |     |      |

|        |                             |                                   | $T_C = T_{C,MAX}$      | 57.9 |      |     |      |

|        |                             |                                   | $T_C = T_{C,MIN}$      | 57.9 |      |     |      |

|        |                             |                                   | $T_C = 25^{\circ}C$    | 55.2 | 64   |     |      |

|        |                             | $f_{\text{IN}} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$      | 55.2 |      |     |      |

| SFDR   | Spurious free dynamic range |                                   | $T_C = T_{C,MIN}$      | 55.2 |      |     | dBc  |

|        |                             |                                   | T <sub>C</sub> = 25°C  | 51.2 | 64   |     |      |

|        |                             | f <sub>IN</sub> = 300 MHz         | $T_C = T_{C,MAX}$      | 51.2 |      |     |      |

|        |                             |                                   | $T_C = T_{C,MIN}$      | 51.2 |      |     |      |

|        |                             | $f_{\text{IN}} = 450 \text{ MHz}$ |                        |      | 64   |     |      |

|        |                             | f <sub>IN</sub> = 650 MHz         |                        |      | 61.6 |     |      |

|        |                             | f <sub>IN</sub> = 900 MHz         |                        |      | 54.5 |     |      |

|        |                             | $f_{IN} = 1.0 \text{ GHz}$        |                        |      | 51.6 |     |      |

Copyright © 2008–2017, Texas Instruments Incorporated

Product Folder Links: ADS5463-SP

# Electrical Characteristics: ADS5463-RHA (continued)

Typical values at  $T_C$  = 25°C, full temperature range is  $T_{C,MIN}$  = -55°C to  $T_{C,MAX}$  = 125°C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clock (unless otherwise noted)

|     | PARAMETER       | TES                        | ST CONDITIONS              | MIN   | TYP  | MAX | UNIT |

|-----|-----------------|----------------------------|----------------------------|-------|------|-----|------|

|     |                 | f <sub>IN</sub> = 10 MHz   |                            |       | 63.5 |     |      |

|     |                 | f <sub>IN</sub> = 70 MHz   | , = 70 MHz                 |       | 64.2 |     |      |

|     |                 |                            | $T_C = 25^{\circ}C$        | 57.9  | 65.4 |     |      |

|     |                 | $f_{IN} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$          | 57.9  |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$          | 57.9  |      |     |      |

|     |                 |                            | $T_C = 25^{\circ}C$        | 55.2  | 64.4 |     |      |

| HD2 |                 | $f_{IN} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$          | 55.2  |      |     |      |

|     | Second harmonic |                            | $T_C = T_{C,MIN}$          | 55.2. |      |     | dBc  |

|     |                 |                            | $T_C = 25^{\circ}C$        | 51.2  | 64.3 |     |      |

|     |                 | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$          | 51.2  |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$          | 51.2  |      |     |      |

|     |                 | $f_{IN} = 450 \text{ MHz}$ | f <sub>IN</sub> = 450 MHz  |       | 64.4 |     |      |

|     |                 | $f_{IN} = 650 \text{ MHz}$ | $f_{IN} = 650 \text{ MHz}$ |       | 67.1 |     |      |

|     |                 | $f_{IN} = 900 \text{ MHz}$ | f <sub>IN</sub> = 900 MHz  |       | 62.9 |     |      |

|     |                 | $f_{IN} = 1.0 \text{ GHz}$ | $f_{IN} = 1.0 \text{ GHz}$ |       | 58.6 |     |      |

|     |                 | $f_{IN} = 10 \text{ MHz}$  |                            |       | 104  |     |      |

|     |                 | $f_{IN} = 70 \text{ MHz}$  | f <sub>IN</sub> = 70 MHz   |       | 104  |     |      |

|     |                 | f <sub>IN</sub> = 100 MHz  | $T_C = 25^{\circ}C$        | 64    | 87   |     |      |

|     |                 |                            | $T_C = T_{C,MAX}$          | 64    |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$          | 64    |      |     |      |

|     |                 |                            | $T_C = 25^{\circ}C$        | 59    | 85   |     |      |

|     |                 | $f_{IN} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$          | 59    |      |     |      |

| HD3 | Third harmonic  |                            | $T_C = T_{C,MIN}$          | 59    |      |     | dBc  |

|     |                 |                            | $T_C = 25^{\circ}C$        | 61.9  | 76   |     |      |

|     |                 | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$          | 61.9  |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$          | 61.9  |      |     |      |

|     |                 | $f_{IN} = 450 \text{ MHz}$ |                            |       | 73.3 |     |      |

|     |                 | $f_{IN} = 650 \text{ MHz}$ |                            |       | 61.6 |     |      |

|     |                 | $f_{IN} = 900 \text{ MHz}$ |                            |       | 54.5 |     |      |

|     |                 | f <sub>IN</sub> = 1.0 GHz  |                            |       | 51.6 |     |      |

# 6.7 Electrical Characteristics: ADS5463-RHA

Typical values at  $T_C = 25^{\circ}$ C, full temperature range is  $T_{C,MIN} = -55^{\circ}$ C to  $T_{C,MAX} = 125^{\circ}$ C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clock (unless otherwise noted)

|        | PARAMETER                                    | TES                        | ST CONDITIONS         | MIN  | TYP  | MAX | UNIT |  |  |  |

|--------|----------------------------------------------|----------------------------|-----------------------|------|------|-----|------|--|--|--|

| YNAMIC | C AC CHARACTERISTICS (CON                    | IT.)                       |                       |      |      |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 10 MHz   |                       |      | 61.9 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 70 MHz   |                       |      | 62.2 |     |      |  |  |  |

|        |                                              |                            | T <sub>C</sub> = 25°C | 55.9 | 62   |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 100 MHz  | $T_C = T_{C,MAX}$     | 55.9 |      |     |      |  |  |  |

|        |                                              |                            | $T_C = T_{C,MIN}$     | 55.9 |      |     |      |  |  |  |

|        |                                              |                            | T <sub>C</sub> = 25°C | 53.8 | 62   |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 210 MHz  | $T_C = T_{C,MAX}$     | 53.8 |      |     |      |  |  |  |

| SINAD  | Signal-to-noise and distortion               |                            | $T_C = T_{C,MIN}$     | 53.8 |      |     | dBc  |  |  |  |

|        |                                              |                            | T <sub>C</sub> = 25°C | 50.2 | 61.9 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 300 MHz  | $T_C = T_{C,MAX}$     | 50.2 |      |     |      |  |  |  |

|        |                                              |                            | $T_C = T_{C,MIN}$     | 50.2 |      |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 450 MHz  |                       |      | 61.6 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 650 MHz  |                       |      | 59.4 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 900 MHz  |                       |      | 54.3 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 1.0 GHz  |                       |      | 51.4 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 10 MHz   |                       |      | 83.1 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 70 MHz   |                       |      | 80.2 |     |      |  |  |  |

|        |                                              |                            | $T_C = 25^{\circ}C$   | 68   | 81.8 |     |      |  |  |  |

|        |                                              | $f_{IN} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 68   |      |     |      |  |  |  |

|        |                                              |                            | $T_C = T_{C,MIN}$     | 68   |      |     |      |  |  |  |

|        |                                              |                            | $T_C = 25^{\circ}C$   | 62   | 77.5 |     |      |  |  |  |

|        | Manat hannania farana fathan                 | f <sub>IN</sub> = 210 MHz  | $T_C = T_{C,MAX}$     | 62   |      |     |      |  |  |  |

|        | Worst harmonic/spur (other than HD2 and HD3) |                            | $T_C = T_{C,MIN}$     | 62   |      |     | dBc  |  |  |  |

|        | ,                                            |                            | $T_C = 25^{\circ}C$   | 62   | 78.2 |     |      |  |  |  |

|        |                                              | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 62   |      |     |      |  |  |  |

|        |                                              |                            | $T_C = T_{C,MIN}$     | 62   |      |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 450 MHz  |                       |      | 80.6 |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 650 MHz  |                       |      | 80   |     |      |  |  |  |

|        |                                              | f <sub>IN</sub> = 900 MHz  |                       |      | 79.4 |     |      |  |  |  |

|        |                                              | $f_{IN} = 1.0 \text{ GHz}$ |                       |      | 77.6 |     |      |  |  |  |

Copyright © 2008–2017, Texas Instruments Incorporated

# **Electrical Characteristics: ADS5463-RHA (continued)**

Typical values at  $T_C$  = 25°C, full temperature range is  $T_{C,MIN}$  = -55°C to  $T_{C,MAX}$  = 125°C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clock (unless otherwise noted)

|         | PARAMETER                   | TES                               | ST CONDITIONS         | MIN   | TYP  | MAX   | UNIT |  |

|---------|-----------------------------|-----------------------------------|-----------------------|-------|------|-------|------|--|

|         |                             | f <sub>IN</sub> = 10 MHz          |                       |       | 63.5 |       |      |  |

|         |                             | $f_{IN} = 70 \text{ MHz}$         |                       |       | 64   |       |      |  |

|         |                             |                                   | T <sub>C</sub> = 25°C | 57.8  | 65.2 |       |      |  |

|         |                             | $f_{IN} = 100 \text{ MHz}$        | $T_C = T_{C,MAX}$     | 57.8  |      |       |      |  |

|         |                             |                                   | $T_C = T_{C,MIN}$     | 57.8  |      |       |      |  |

|         |                             |                                   | T <sub>C</sub> = 25°C | 55    | 64.1 |       |      |  |

|         |                             | $f_{IN} = 210 \text{ MHz}$        | $T_C = T_{C,MAX}$     | 55    |      |       |      |  |

| THD     | Total harmonic distortion   |                                   | $T_C = T_{C,MIN}$     | 55    |      |       | dBc  |  |

|         |                             |                                   | T <sub>C</sub> = 25°C | 51    | 63.8 |       |      |  |

|         |                             | $f_{IN} = 300 \text{ MHz}$        | $T_C = T_{C,MAX}$     | 51    |      |       |      |  |

|         |                             |                                   | $T_C = T_{C,MIN}$     | 51    |      |       |      |  |

|         |                             | f <sub>IN</sub> = 450 MHz         |                       |       | 63.7 |       |      |  |

|         |                             | $f_{IN} = 650 \text{ MHz}$        |                       |       | 60.5 |       |      |  |

|         |                             | $f_{\text{IN}} = 900 \text{ MHz}$ |                       |       | 53.9 |       |      |  |

|         |                             | $f_{IN} = 1.0 \text{ GHz}$        |                       |       | 50.8 |       |      |  |

|         |                             |                                   | T <sub>C</sub> = 25°C | 9     | 10.1 |       |      |  |

|         |                             | $f_{IN} = 100 \text{ MHz}$        | $T_C = T_{C,MAX}$     | 9     |      |       |      |  |

|         |                             |                                   | $T_C = T_{C,MIN}$     | 9     |      |       |      |  |

|         |                             |                                   | T <sub>C</sub> = 25°C | 8.65  | 10   |       |      |  |

| ENOB    | Effective number of bits    | $f_{IN} = 210 \text{ MHz}$        | $T_C = T_{C,MAX}$     | 8.65  |      |       | Bits |  |

|         |                             |                                   | $T_C = T_{C,MIN}$     | 8.65  |      |       |      |  |

|         |                             |                                   | T <sub>C</sub> = 25°C | 8.05  | 9.9  |       |      |  |

|         |                             | $f_{IN} = 300 \text{ MHz}$        | $T_C = T_{C,MAX}$     | 8.05  |      |       |      |  |

|         |                             |                                   | $T_C = T_{C,MIN}$     | 8.05  |      |       |      |  |

|         | RMS idle-channel noise      | Inputs tied to co                 | ommon-mode            |       | 0.7  |       | LSB  |  |

| LVDS DI | GITAL OUTPUTS               |                                   |                       |       |      |       |      |  |

| VOD     | Differential output voltage |                                   |                       | 247   | 350  | 454   | mV   |  |

| VOC     | Common mode output voltage  |                                   |                       | 1.125 |      | 1.375 | V    |  |

# 6.8 Electrical Characteristics: ADS5463-SP

Typical values at  $T_C$  = 25°C, full temperature range is  $T_{C,MIN}$  = -55°C to  $T_{C,MAX}$  = 125°C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clockover operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                   | TEST                                                        | CONDITIONS             | MIN   | TYP     | MAX   | UNIT     |

|--------------------|---------------------------------------------|-------------------------------------------------------------|------------------------|-------|---------|-------|----------|

| Resoluti           | on                                          |                                                             |                        |       | 12      |       | Bits     |

| ANALO              | G INPUTS                                    |                                                             |                        |       |         |       |          |

|                    | Differential input range                    |                                                             |                        |       | 2.2     |       | $V_{PP}$ |

|                    | Input resistance (dc)                       | Each input to VCM                                           |                        |       | 500     |       | Ω        |

|                    | Input capacitance                           | Each input to ground                                        |                        |       | 2.5     |       | pF       |

|                    | Analog input bandwidth                      |                                                             |                        | 1000  | 2000    |       | MHz      |

| INTERN             | AL REFERENCE VOLTAG                         | Ε                                                           |                        |       |         |       |          |

| $V_{REF}$          | Reference voltage                           | Full temperature rang                                       | е                      | 2.38  | 2.4     | 2.42  | V        |

| DYNAM              | IC ACCURACY                                 | •                                                           | •                      |       |         |       |          |

|                    | No missing codes                            |                                                             |                        |       | Assured |       |          |

| DNL                | Differential linearity error                | f <sub>IN</sub> = 210 MHz                                   | Full temperature range | -0.98 | ±0.95   | 1.2   | LSB      |

| INL                | Integral linearity error                    | f <sub>IN</sub> = 210 MHz                                   | Full temperature range | -2.9  | ±1.5    | 2.9   | LSB      |

|                    | Offset error                                | Full temperature rang                                       | е                      | -0.5  |         | 0.5   | %FS      |

|                    | Offset temperature coefficient              |                                                             |                        |       | 0.0009  |       | %FS/°C   |

|                    | Gain error                                  | Full temperature rang                                       | е                      | -5    |         | 5     | %FS      |

|                    | Gain temperature coefficient                |                                                             |                        |       | -0.02   |       | %FS/°C   |

| POWER              | SUPPLY                                      |                                                             |                        |       |         |       |          |

| I <sub>AVDD5</sub> | 5 V analog supply current                   |                                                             |                        |       |         | 335   | mA       |

| I <sub>AVDD3</sub> | 3.3 V analog supply current                 | V <sub>IN</sub> = full scale,<br>f <sub>IN</sub> = 300 MHz, | Full temperature range |       |         | 140   | mA       |

| I <sub>DVDD3</sub> | 3.3 V digital supply current(includes LVDS) | F <sub>S</sub> = 500 MSPS                                   |                        |       |         | 88    | mA       |

|                    | Power dissipation                           |                                                             |                        |       |         | 2.425 | W        |

Copyright © 2008–2017, Texas Instruments Incorporated Submit Documentation Feedback

## 6.9 Electrical Characteristics: ADS5463-SP

Typical values at  $T_C = 25^{\circ}$ C, full temperature range is  $T_{C,MIN} = -55^{\circ}$ C to  $T_{C,MAX} = 125^{\circ}$ C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clockover operating free-air temperature range (unless otherwise noted)

|       | PARAMETER                   | TES                               | ST CONDITIONS       | MIN  | TYP  | MAX | UNIT |  |  |  |

|-------|-----------------------------|-----------------------------------|---------------------|------|------|-----|------|--|--|--|

| DYNAM | IC AC CHARACTERISTICS       |                                   |                     | ·    |      |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 10 MHz          |                     |      | 65.4 |     |      |  |  |  |

|       |                             | $f_{IN} = 70 \text{ MHz}$         |                     |      | 65.3 |     |      |  |  |  |

|       |                             |                                   | $T_C = 25^{\circ}C$ | 64.1 | 65.2 |     |      |  |  |  |

|       |                             | $f_{IN} = 100 \text{ MHz}$        | $T_C = T_{C,MAX}$   | 62.7 |      |     |      |  |  |  |

|       |                             |                                   | $T_C = T_{C,MIN}$   | 63.5 |      |     |      |  |  |  |

|       |                             |                                   | $T_C = 25^{\circ}C$ | 63.6 | 65   |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 210 MHz         | $T_C = T_{C,MAX}$   | 62.4 |      |     |      |  |  |  |

| SNR   | Signal-to-noise ratio       |                                   | $T_C = T_{C,MIN}$   | 63.2 |      |     | dBFS |  |  |  |

|       |                             |                                   | $T_C = 25^{\circ}C$ | 62.7 | 64.9 |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 300 MHz         | $T_C = T_{C,MAX}$   | 61.3 |      |     |      |  |  |  |

|       |                             |                                   | $T_C = T_{C,MIN}$   | 61.9 |      |     |      |  |  |  |

|       |                             | $f_{\text{IN}} = 450 \text{ MHz}$ |                     |      | 64.5 |     |      |  |  |  |

|       |                             | $f_{IN} = 650 \text{ MHz}$        |                     |      | 63.7 |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 900 MHz         |                     |      | 62.8 |     |      |  |  |  |

|       |                             | $f_{IN} = 1.0 \text{ GHz}$        |                     |      | 62.2 |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 10 MHz          |                     |      | 63.5 |     |      |  |  |  |

|       |                             | $f_{\text{IN}} = 70 \text{ MHz}$  |                     |      | 64.2 |     |      |  |  |  |

|       |                             |                                   | $T_C = 25^{\circ}C$ | 57.9 | 65   |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 100 MHz         | $T_C = T_{C,MAX}$   | 58.8 |      |     |      |  |  |  |

|       |                             |                                   | $T_C = T_{C,MIN}$   | 58.6 |      |     |      |  |  |  |

|       |                             |                                   | $T_C = 25^{\circ}C$ | 55.2 | 64.0 |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 210 MHz         | $T_C = T_{C,MAX}$   | 56.6 |      |     |      |  |  |  |

| SFDR  | Spurious free dynamic range |                                   | $T_C = T_{C,MIN}$   | 56.9 |      |     | dBc  |  |  |  |

|       |                             |                                   | $T_C = 25^{\circ}C$ | 54.1 | 64   |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 300 MHz         | $T_C = T_{C,MAX}$   | 51.3 |      |     |      |  |  |  |

|       |                             |                                   | $T_C = T_{C,MIN}$   | 56.2 |      |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 450 MHz         |                     |      | 64   |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 650 MHz         |                     |      | 61.6 |     |      |  |  |  |

|       |                             | f <sub>IN</sub> = 900 MHz         |                     |      | 54.5 |     | ]    |  |  |  |

|       |                             | f <sub>IN</sub> = 1.0 GHz         |                     |      | 51.6 |     |      |  |  |  |

Submit Documentation Feedback

Copyright © 2008–2017, Texas Instruments Incorporated

# Electrical Characteristics: ADS5463-SP (continued)

Typical values at  $T_C = 25^{\circ}$ C, full temperature range is  $T_{C,MIN} = -55^{\circ}$ C to  $T_{C,MAX} = 125^{\circ}$ C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clockover operating free-air temperature range (unless otherwise noted)

|     | PARAMETER       | TES                        | ST CONDITIONS         | MIN  | TYP  | MAX | UNIT |

|-----|-----------------|----------------------------|-----------------------|------|------|-----|------|

|     |                 | f <sub>IN</sub> = 10 MHz   |                       |      | 63.5 |     |      |

|     |                 | $f_{IN} = 70 \text{ MHz}$  |                       |      | 64.2 |     |      |

|     |                 |                            | $T_C = 25^{\circ}C$   | 57.9 | 65.4 |     |      |

|     |                 | $f_{IN} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 58.8 |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$     | 58.6 |      |     |      |

|     |                 |                            | $T_C = 25^{\circ}C$   | 55.2 | 64.4 |     |      |

|     |                 | $f_{IN} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 56.6 |      |     |      |

| HD2 | Second harmonic |                            | $T_C = T_{C,MIN}$     | 56.9 |      |     | dBc  |

|     |                 |                            | T <sub>C</sub> = 25°C | 54.1 | 64.3 |     |      |

|     |                 | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 51.3 |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$     | 56.2 |      |     |      |

|     |                 | $f_{IN} = 450 \text{ MHz}$ | <u>.</u>              |      | 64.4 |     |      |

|     |                 | $f_{IN} = 650 \text{ MHz}$ |                       |      | 67.1 |     |      |

|     |                 | f <sub>IN</sub> = 900 MHz  |                       |      | 62.9 |     |      |

|     |                 | f <sub>IN</sub> = 1.0 GHz  |                       |      | 58.6 |     |      |

|     |                 | f <sub>IN</sub> = 10 MHz   |                       |      | 104  |     |      |

|     |                 | $f_{IN} = 70 \text{ MHz}$  |                       |      | 104  |     |      |

|     |                 |                            | $T_C = 25^{\circ}C$   | 69   | 87   |     |      |

|     |                 | $f_{IN} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 68.5 |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$     | 65.6 |      |     |      |

|     |                 |                            | T <sub>C</sub> = 25°C | 66.7 | 85   |     |      |

|     |                 | $f_{IN} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 65.3 |      |     |      |

| HD3 | Third harmonic  |                            | $T_C = T_{C,MIN}$     | 64.1 |      |     | dBc  |

|     |                 |                            | $T_C = 25^{\circ}C$   | 70.1 | 76   |     |      |

|     |                 | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 61.9 |      |     |      |

|     |                 |                            | $T_C = T_{C,MIN}$     | 64.8 |      |     |      |

|     |                 | $f_{IN} = 450 \text{ MHz}$ |                       |      | 73.3 |     |      |

|     |                 | $f_{IN} = 650 \text{ MHz}$ |                       |      | 61.6 |     |      |

|     |                 | f <sub>IN</sub> = 900 MHz  |                       |      | 54.5 |     |      |

|     |                 | f <sub>IN</sub> = 1.0 GHz  |                       |      | 51.6 |     |      |

Copyright © 2008–2017, Texas Instruments Incorporated

## 6.10 Electrical Characteristics: ADS5463-SP

Typical values at  $T_C = 25^{\circ}$ C, full temperature range is  $T_{C,MIN} = -55^{\circ}$ C to  $T_{C,MAX} = 125^{\circ}$ C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clockover operating free-air temperature range (unless otherwise noted)

|        | PARAMETER                                    | TES                               | ST CONDITIONS         | MIN  | TYP  | MAX | UNIT |  |  |

|--------|----------------------------------------------|-----------------------------------|-----------------------|------|------|-----|------|--|--|

| DYNAMI | C AC CHARACTERISTICS (CON                    | T.)                               |                       |      |      |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 10 MHz          |                       |      | 61.9 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 70 MHz          |                       |      | 62.2 |     |      |  |  |

|        |                                              |                                   | $T_C = 25^{\circ}C$   | 58   | 62   |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 100 MHz         | $T_C = T_{C,MAX}$     | 58   |      |     |      |  |  |

|        |                                              |                                   | $T_C = T_{C,MIN}$     | 58.4 |      |     |      |  |  |

|        |                                              |                                   | T <sub>C</sub> = 25°C | 55.8 | 62   |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 210 MHz         | $T_C = T_{C,MAX}$     | 56.2 |      |     |      |  |  |

| SINAD  | Signal-to-noise and distortion               |                                   | $T_C = T_{C,MIN}$     | 56.7 |      |     | dBc  |  |  |

|        |                                              |                                   | $T_C = 25^{\circ}C$   | 54.9 | 61.9 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 300 MHz         | $T_C = T_{C,MAX}$     | 52.2 |      |     |      |  |  |

|        |                                              |                                   | $T_C = T_{C,MIN}$     | 56.1 |      |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 450 MHz         |                       |      | 61.6 |     |      |  |  |

|        |                                              | $f_{IN} = 650 \text{ MHz}$        |                       |      | 59.4 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 900 MHz         |                       |      | 54.3 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 1.0 GHz         |                       |      | 51.4 |     |      |  |  |

|        |                                              | $f_{IN} = 10 \text{ MHz}$         |                       |      | 83.1 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 70 MHz          |                       |      | 80.2 |     |      |  |  |

|        |                                              |                                   | $T_C = 25^{\circ}C$   | 72.2 | 81.8 |     |      |  |  |

|        |                                              | $f_{\text{IN}} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 70.6 |      |     |      |  |  |

|        |                                              |                                   | $T_C = T_{C,MIN}$     | 72.6 |      |     |      |  |  |

|        |                                              |                                   | T <sub>C</sub> = 25°C | 70.6 | 77.5 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 210 MHz         | $T_C = T_{C,MAX}$     | 67.1 |      |     |      |  |  |

|        | Worst harmonic/spur (other than HD2 and HD3) |                                   | $T_C = T_{C,MIN}$     | 66.5 |      |     | dBc  |  |  |

|        |                                              |                                   | T <sub>C</sub> = 25°C | 69.3 | 78.2 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 300 MHz         | $T_C = T_{C,MAX}$     | 66.3 |      |     |      |  |  |

|        |                                              |                                   | $T_C = T_{C,MIN}$     | 66.3 |      |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 450 MHz         |                       |      | 80.6 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 650 MHz         |                       |      | 80   |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 900 MHz         |                       |      | 79.4 |     |      |  |  |

|        |                                              | f <sub>IN</sub> = 1.0 GHz         |                       |      | 77.6 |     |      |  |  |

# **Electrical Characteristics: ADS5463-SP (continued)**

Typical values at  $T_C$  = 25°C, full temperature range is  $T_{C,MIN}$  = -55°C to  $T_{C,MAX}$  = 125°C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1 dBFS differential input, and 3-V<sub>PP</sub> differential clockover operating free-air temperature range (unless otherwise noted)

| PARAMETER |                             | TES                        | TEST CONDITIONS       |       |      | MAX   | UNIT |

|-----------|-----------------------------|----------------------------|-----------------------|-------|------|-------|------|

|           |                             | f <sub>IN</sub> = 10 MHz   |                       |       | 63.5 |       |      |

|           |                             | f <sub>IN</sub> = 70 MHz   |                       |       | 64   |       |      |

|           |                             |                            | T <sub>C</sub> = 25°C | 57.8  | 65.2 |       |      |

|           |                             | $f_{IN} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 58.3  |      |       |      |

|           |                             |                            | $T_C = T_{C,MIN}$     | 58.1  |      |       |      |

|           |                             |                            | T <sub>C</sub> = 25°C | 55    | 64.1 |       |      |

|           |                             | $f_{IN} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 55.9  |      |       |      |

| THD       | Total harmonic distortion   |                            | $T_C = T_{C,MIN}$     | 56.2  |      |       | dBc  |

|           |                             |                            | T <sub>C</sub> = 25°C | 53.9  | 63.8 |       |      |

|           |                             | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 51    |      |       |      |

|           |                             |                            | $T_C = T_{C,MIN}$     | 55.6  |      |       |      |

|           |                             | f <sub>IN</sub> = 450 MHz  |                       |       | 63.7 |       |      |

|           |                             | f <sub>IN</sub> = 650 MHz  |                       |       | 60.5 |       |      |

|           |                             | f <sub>IN</sub> = 900 MHz  |                       |       | 53.9 |       |      |

|           |                             | f <sub>IN</sub> = 1.0 GHz  |                       |       | 50.8 |       |      |

|           |                             |                            | T <sub>C</sub> = 25°C | 9.3   | 10.1 |       |      |

|           |                             | $f_{IN} = 100 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 9.3   |      |       |      |

|           |                             |                            | $T_C = T_{C,MIN}$     | 9.4   |      |       |      |

|           |                             |                            | T <sub>C</sub> = 25°C | 8.9   | 10   |       |      |

| ENOB      | Effective number of bits    | $f_{IN} = 210 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 9     |      |       | Bits |

|           |                             |                            | $T_C = T_{C,MIN}$     | 9.1   |      |       |      |

|           |                             |                            | T <sub>C</sub> = 25°C | 8.8   | 9.9  |       |      |

|           |                             | $f_{IN} = 300 \text{ MHz}$ | $T_C = T_{C,MAX}$     | 8.3   |      |       |      |

|           |                             |                            | $T_C = T_{C,MIN}$     | 9     |      |       |      |

|           | RMS idle-channel noise      | Inputs tied to co          | mmon-mode             |       | 0.7  |       | LSB  |

| LVDS DI   | GITAL OUTPUTS               |                            |                       |       |      | -     |      |

| VOD       | Differential output voltage |                            |                       | 247   | 350  | 454   | mV   |

| VOC       | Common mode output voltage  | je                         |                       | 1.125 |      | 1.375 | V    |

Product Folder Links: ADS5463-SP

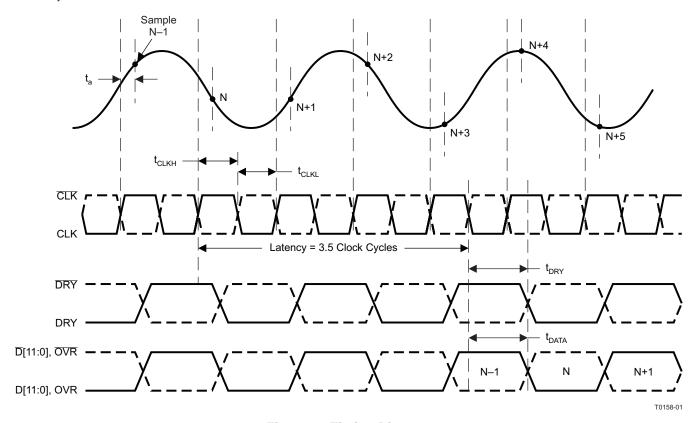

### 6.11 Timing Requirements

Typical values at  $T_C = 25^{\circ}\text{C}$ , full temperature range is  $T_{C,MIN} = -55^{\circ}\text{C}$  to  $T_{C,MAX} = 125^{\circ}\text{C}$ , sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 3  $V_{PP}$  differential clock (unless otherwise noted)<sup>(1)</sup>.

|                   |                                      |                                     | 1 | MIN | NOM  | MAX  | UNIT   |

|-------------------|--------------------------------------|-------------------------------------|---|-----|------|------|--------|

| ta                | Aperture delay                       |                                     |   |     | 200  |      | ps     |

|                   | Aperture jitter, rms                 |                                     |   |     | 160  |      | fs     |

|                   | Latency                              |                                     |   |     | 3.5  |      | cycles |

| t <sub>CLK</sub>  | Clock period                         |                                     |   | 2   |      | 50   | ns     |

| t <sub>CLKH</sub> | Clock pulse duration, high           |                                     |   | 1   |      |      | ns     |

| t <sub>CLKL</sub> | Clock pulse duration, low            |                                     |   | 1   |      |      | ns     |

| t <sub>DRY</sub>  | CLK to DRY delay <sup>(2)</sup>      | Zero crossing                       |   | 750 | 1500 | 2500 | ps     |

| t <sub>DATA</sub> | CLK to DATA/OVR delay <sup>(2)</sup> | Zero crossing                       |   | 650 | 1500 | 3100 | ps     |

| t <sub>SKEW</sub> | DATA to DRY skew                     | t <sub>DATA</sub> -t <sub>DRY</sub> | _ | 700 | 0    | 700  | ps     |

| t <sub>RISE</sub> | DRY/DATA/OVR rise time               |                                     |   |     | 500  |      | ps     |

| t <sub>FALL</sub> | DRY/DATA/OVR fall time               |                                     |   |     | 500  |      | ps     |

- Timing parameters are assured by design or characterization, but not production tested. < 10-pF load on each output pin. DRY, DATA and OVR are updated on the falling edge of CLK. The latency must be added to  $t_{DATA}$  to determine the overall propagation delay.

Figure 1. Timing Diagram

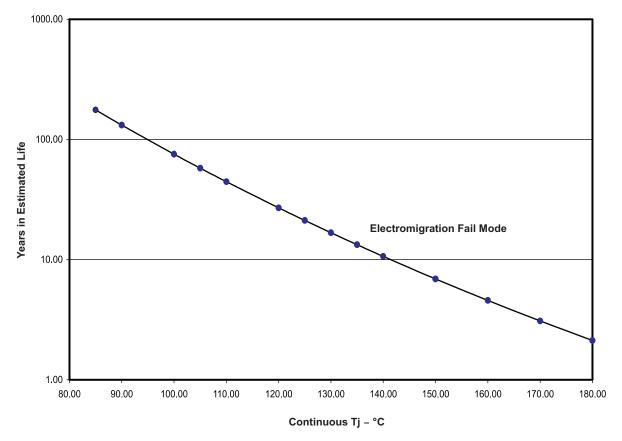

Figure 2. ADS5463 Estimated Life at Elevated Temperature Electromigration Fail Mode

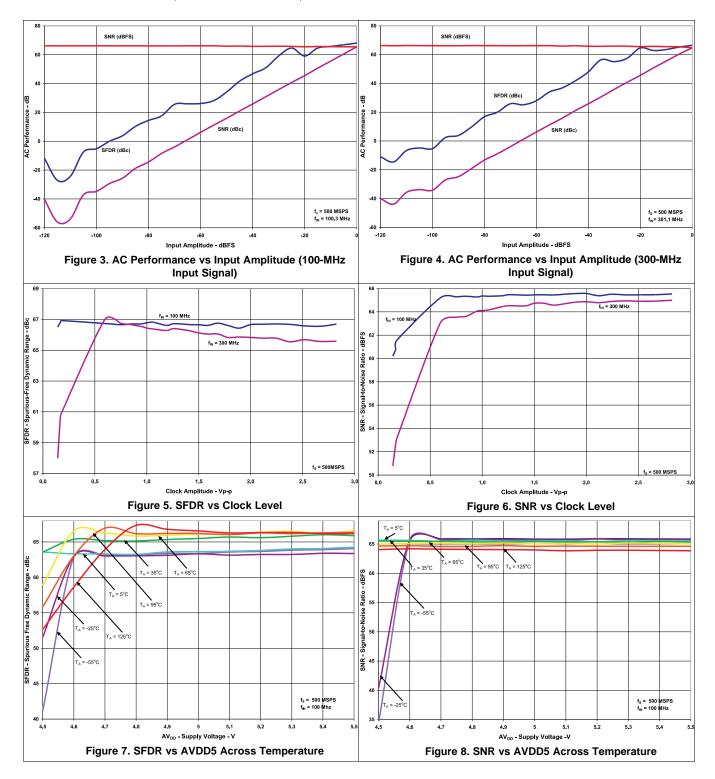

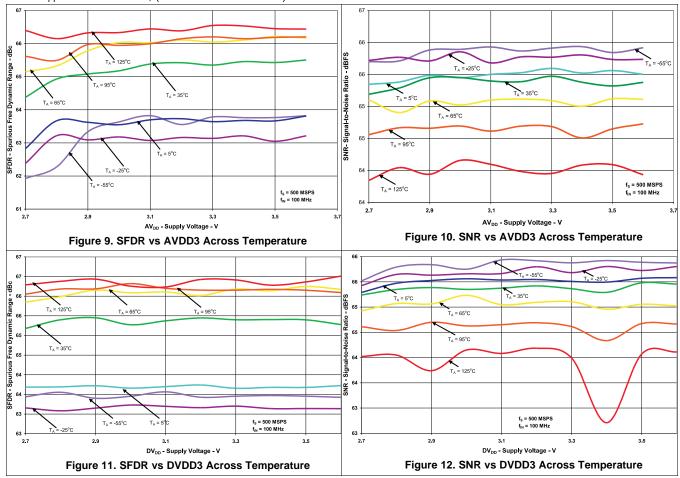

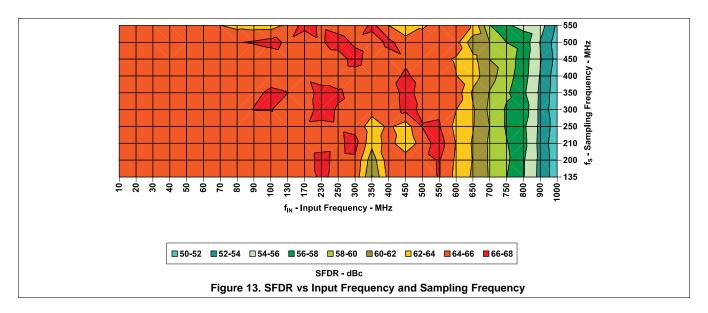

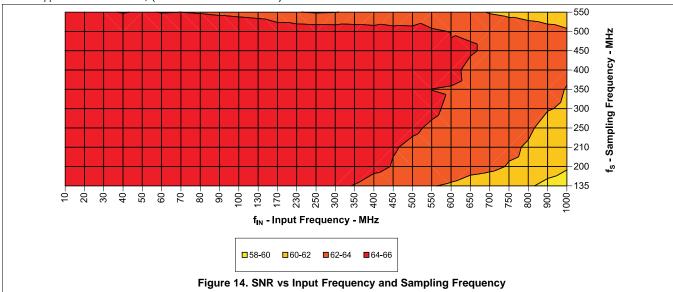

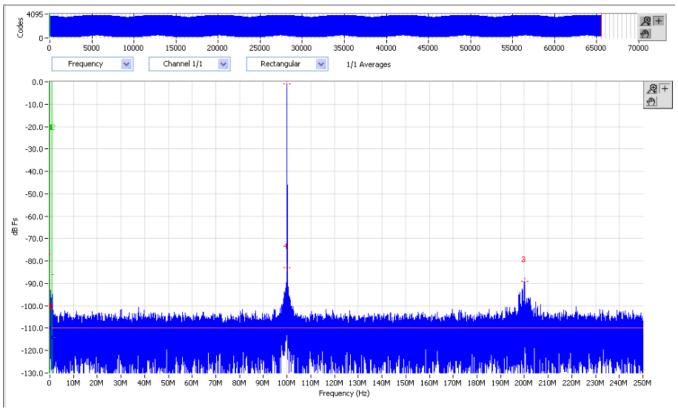

### 6.12 Typical Characteristics

Typical plots at  $T_A = 25$ °C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 3  $V_{PP}$  differential clock, (unless otherwise noted)

#### **Typical Characteristics (continued)**

Typical plots at  $T_A = 25$ °C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 3  $V_{PP}$  differential clock, (unless otherwise noted)

Copyright © 2008–2017, Texas Instruments Incorporated

### **Typical Characteristics (continued)**

Typical plots at  $T_A = 25$ °C, sampling rate = 500 MSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 3  $V_{PP}$  differential clock, (unless otherwise noted)

#### 7 Detailed Description

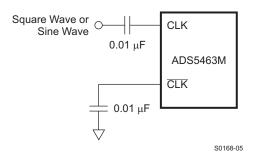

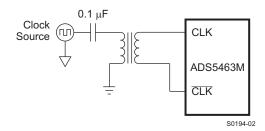

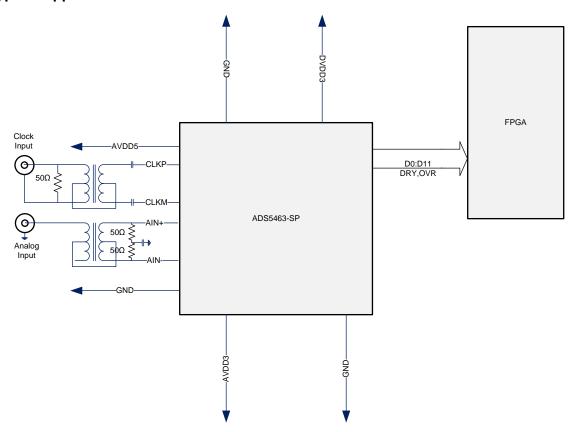

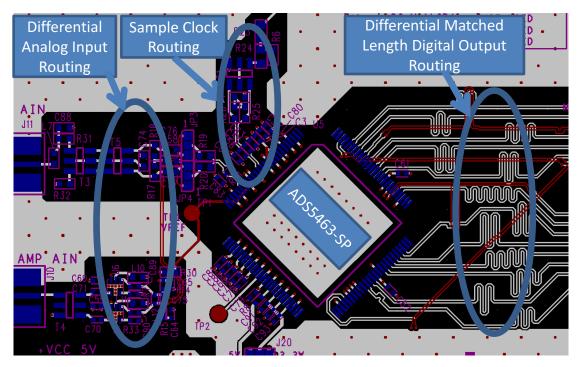

#### 7.1 Overview