**DAC8881**

ZHCSHA4B -JULY 2007-REVISED JANUARY 2018

## DAC8881 16 位单通道低噪声电压输出 数模转换器

### 特性

- 相对精度: ±0.5LSB

- 全温度范围内的 16 位单调性

- 低噪声: 24nV/√Hz

- 快速稳定: 5µs

- 支持轨至轨运行的片上输出缓冲放大器

- 单个宽电源电压范围: +2.7V 至 +5.5V

- DAC 负载控制

- 可选择的上电复位至零电平或中间电平

- 掉电模式

- 单极直接二进制或 二进制补码输入模式

- 具有施密特触发输入的快速 SPI™接口: 高达 50MHz, 1.8V/3V/5V 逻辑电平

- 小型封装: QFN-24, 4x4mm

### 应用

- 工业过程控制

- 数据采集系统

- 自动测试设备

- 通信

- 光纤网络

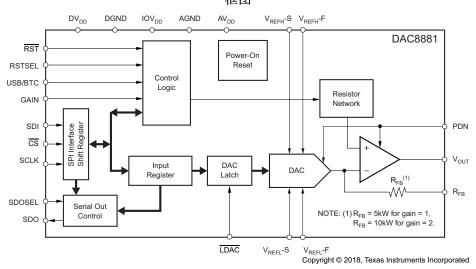

#### 3 说明

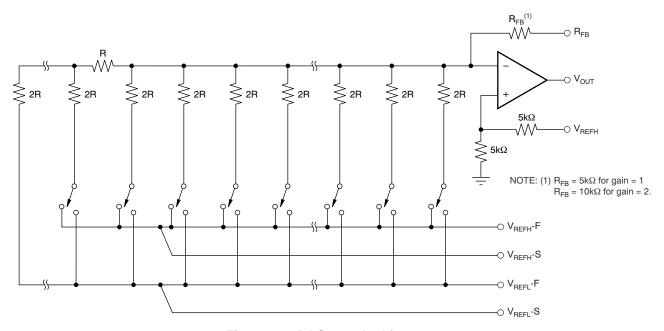

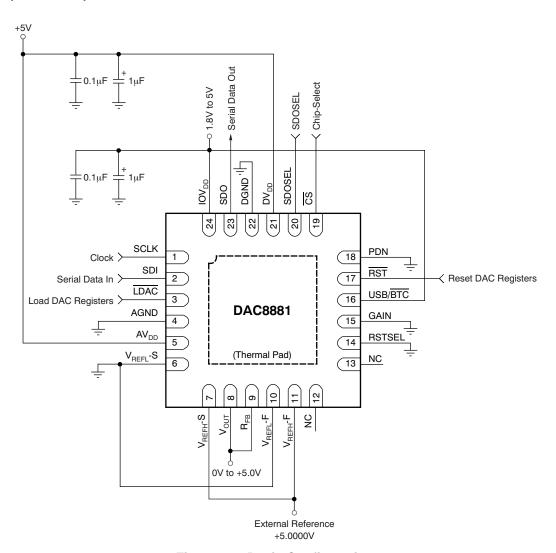

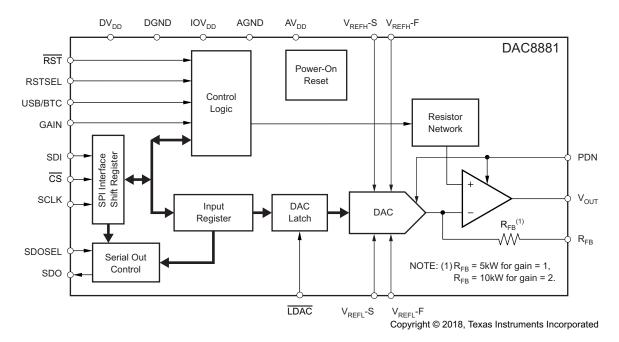

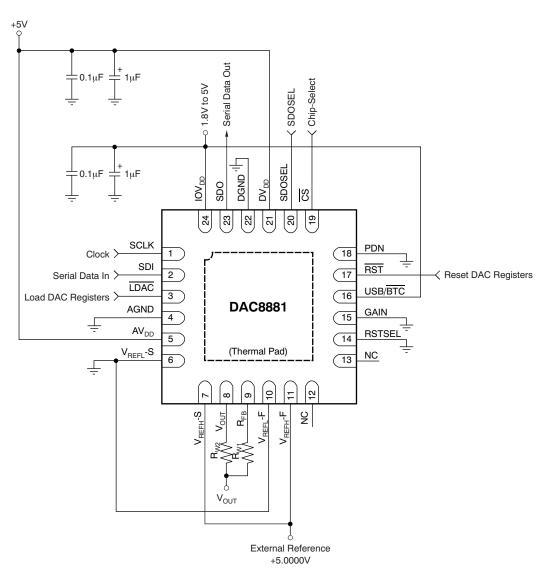

DAC8881 是一款 16 位单通道电压输出数模转换器 (DAC),可提供低功耗运行和灵活的 SPI 串行接口。该 器件还 具有 16 位单调性、卓越的线性度以及快速稳 定性能。片上精密输出放大器可在 2.7V 至 5.5V 的完 整电压范围内实现轨至轨输出摆幅。

该器件支持标准 SPI 串行接口,这种接口可在高达 50MHz 的输入数据时钟频率下工作。DAC8881 需要 外部基准电压来设置 DAC 通道的输出范围。该器件还 采用了可编程上电复位电路,确保 DAC 输出可以零电 平或中间电平加电并保持,直到写入一个有效代码。

而且, 该器件能够在单极直接二进制或二进制补码模式 下运行。DAC8881 可提供通过 PDN 引脚实现的断电 功能,从而在 5V 时将电流消耗减少到 25µA。5V 时的 功耗为 6mW, 断电模式下降低至 125μW。

DAC8881 采用 4 x 4 mm QFN-24 封装, 指定工作温 度为 -40°C 至 +105°C。

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |  |  |

|-------------|---------|-----------------|--|--|

| DAC8881     | VOFN    | 4.00mm x 4.00mm |  |  |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

### 框图

|   | 目录                                                     | :  |                                                  |                |

|---|--------------------------------------------------------|----|--------------------------------------------------|----------------|

| 1 | 特性 1                                                   |    | 7.2 Functional Block Diagram                     | 2!             |

| 2 | 应用 1                                                   |    | 7.3 Feature Description                          | 2!             |

| 3 | 说明 1                                                   |    | 7.4 Device Functional Modes                      | 30             |

| 4 | 修订历史记录 2                                               | 8  | Application and Implementation                   | 3              |

| 5 | Pin Configuration and Functions                        |    | 8.1 Application Information                      | 3 <sup>-</sup> |

| 6 | Specifications4                                        |    | 8.2 Typical Application                          | 3              |

| U | 6.1 Absolute Maximum Ratings                           |    | 8.3 System Example                               | 3              |

|   | 6.2 ESD Ratings                                        | 9  | Power Supply Recommendations                     | 34             |

|   | 6.3 Recommended Operating Conditions                   | 10 | Layout                                           | 34             |

|   | 6.4 Thermal Information                                |    | 10.1 Layout Guidelines                           |                |

|   | 6.5 Electrical Characteristics                         |    | 10.2 Layout Example                              | 34             |

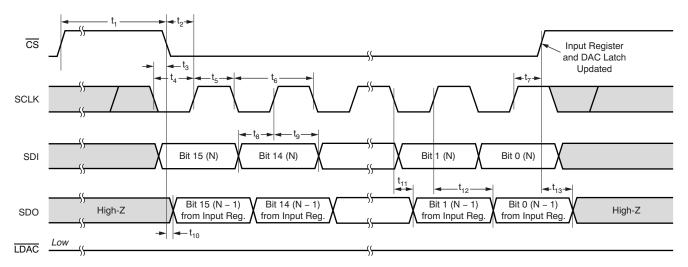

|   | 6.6 Timing Characteristics for Figure 1                | 11 | 器件和文档支持                                          | 3              |

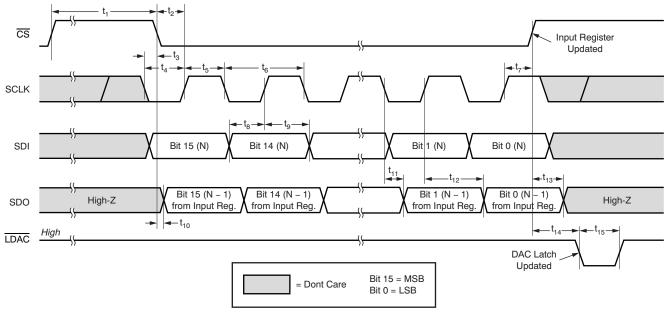

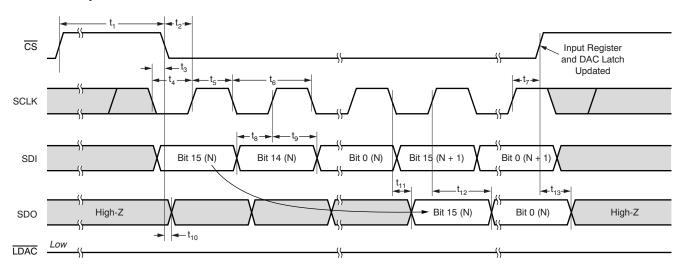

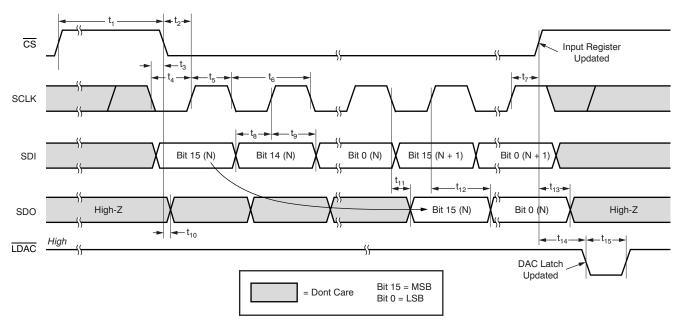

|   | 6.7 Timing Characteristics for Figure 2 and Figure 3 8 |    | 11.1 Documentation Support                       | 3              |

|   | 6.8 Typical Characteristics: V <sub>DD</sub> = +5 V    |    | 11.2 Receiving Notification of Documentation Upo | dates 3        |

|   | 6.9 Typical Characteristics: V <sub>DD</sub> = +2.7 V  |    | 11.3 社区资源                                        | 3              |

| 7 | Detailed Description23                                 |    | 11.4 商标                                          | 3              |

|   | 7.1 Overview                                           |    | 11.5 静电放电警告                                      | 3              |

|   |                                                        |    | 11.6 Glossary                                    | 3              |

### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| CI | hanges from Revision A (September 2007) to Revision B                                       | Page |

|----|---------------------------------------------------------------------------------------------|------|

| •  | 增加了器件信息表、ESD 额定值表、建议运行条件表、特性 说明部分、器件功能模式、应用和实施部分、电源相关<br>议部分、布局部分、器件和文档支持部分以及机械、封装和可订购信息部分。 |      |

| •  | Changed the text in the Input Data Format section                                           | 28   |

| •  | Changed Table 3                                                                             | 29   |

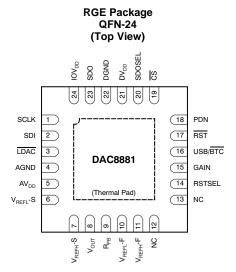

### 5 Pin Configuration and Functions

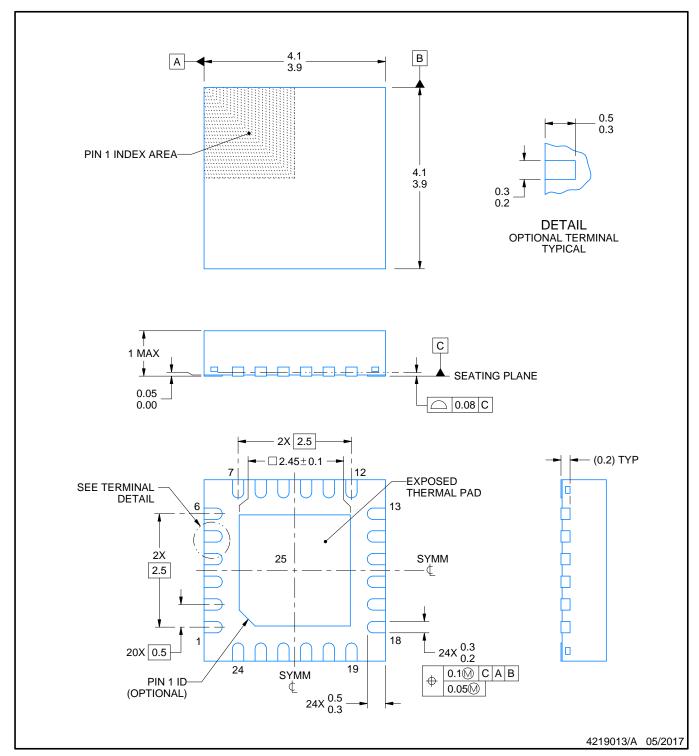

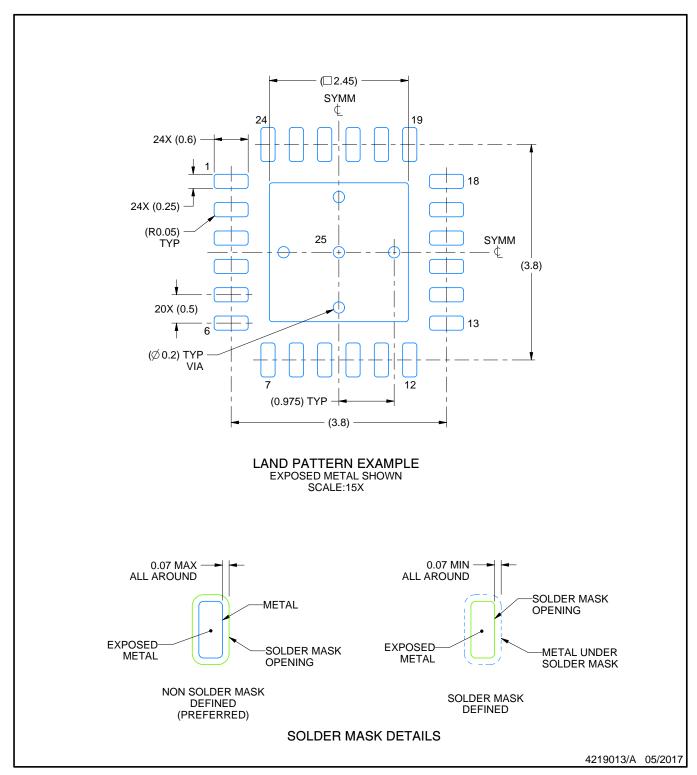

(1) The thermal pad is internally connected to the substrate. This pad can be connected to the analog ground or left floating. Keep the thermal pad separate from the digital ground, if possible.

#### **Pin Functions**

|             | PIN                  |     |                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.         | NAME                 | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |

| 1           | SCLK                 | ı   | SPI bus serial clock input                                                                                                                                                                                                                                                                                                                                  |

| 2           | SDI                  | I   | SPI bus serial data input                                                                                                                                                                                                                                                                                                                                   |

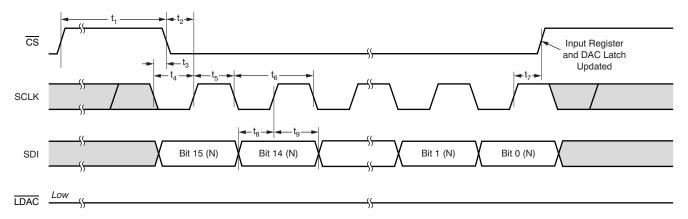

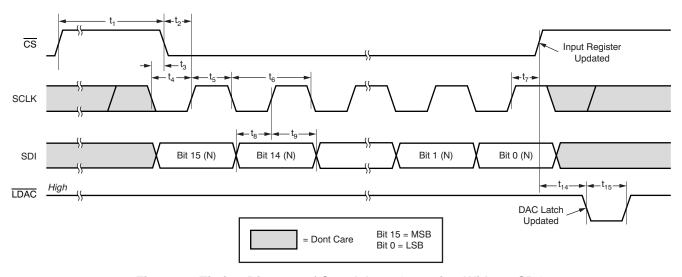

| 3 LDAC I re |                      | I   | Load DAC latch control input (active low). When \overline{LDAC} is low, the DAC latch is transparent, and the contents of the input register are transferred to the DAC latch. The DAC output changes to the corresponding level simultaneously when the DAC latch is updated.                                                                              |

| 4           | AGND                 | ı   | Analog ground                                                                                                                                                                                                                                                                                                                                               |

| 5           | $AV_{DD}$            | I   | Analog power supply                                                                                                                                                                                                                                                                                                                                         |

| 6           | V <sub>REFL</sub> -S | ı   | Reference low input sense                                                                                                                                                                                                                                                                                                                                   |

| 7           | V <sub>REFH</sub> -S | ı   | Reference high input sense                                                                                                                                                                                                                                                                                                                                  |

| 8           | V <sub>OUT</sub>     | 0   | Output of output buffer                                                                                                                                                                                                                                                                                                                                     |

| 9           | R <sub>FB</sub>      | ı   | Feedback resistor connected to the inverting input of the output buffer.                                                                                                                                                                                                                                                                                    |

| 10          | V <sub>REFL</sub> -F | ı   | Reference low input force                                                                                                                                                                                                                                                                                                                                   |

| 11          | V <sub>REFH</sub> -F | I   | Reference high input force                                                                                                                                                                                                                                                                                                                                  |

| 12          | NC                   | _   | Do not connect.                                                                                                                                                                                                                                                                                                                                             |

| 13          | NC                   | _   | Do not connect.                                                                                                                                                                                                                                                                                                                                             |

| 14          | RSTSEL               | I   | Selects the value of the output from the $V_{OUT}$ pin after power-on or hardware reset. If RSTSEL = $IOV_{DD}$ , then register data = 8000h. If RSTSEL = DGND, then register data = 0000h.                                                                                                                                                                 |

| 15          | GAIN                 | I   | Buffer gain setting. Gain = 1 when the pin is connected to DGND; Gain = 2 when the pin is connected to IOV <sub>DD</sub> .                                                                                                                                                                                                                                  |

| 16          | USB/BTC              | I   | Input data format selection. Input data are straight binary format when the pin is connected to IOV <sub>DD</sub> , and in two's complement format when the pin is connected to DGND.                                                                                                                                                                       |

| 17          | RST                  | ı   | Reset input (active low). Logic low on this pin causes the device to perform a reset.                                                                                                                                                                                                                                                                       |

| 18          | PDN                  | 1   | Power-down input (active high). Logic high on this pin forces the device into power-down status. In power-down, the $V_{OUT}$ pin connects to AGND through 10k $\Omega$ resistor.                                                                                                                                                                           |

| 19          | CS                   | 1   | SPI bus chip select input (active low). Data bits are not clocked into the serial shift register unless $\overline{CS}$ is low. When $\overline{CS}$ is high, SDO is in high-impedance status.                                                                                                                                                              |

| 20          | SDOSEL               | I   | SPI serial data output selection. When SDOSEL is tied to IOV <sub>DD</sub> , the contents of the existing input register are shifted out from the SDO pin; this is Stand-Alone mode. When SDOSEL is tied to DGND, the contents in the SPI input shift register are shifted out from the SDO pin; this is Daisy-Chain mode for daisy chaining communication. |

| 21          | DV <sub>DD</sub>     | 1   | Digital power supply (connect to AV <sub>DD</sub> , pin 5)                                                                                                                                                                                                                                                                                                  |

| 22          | DGND                 | I   | Digital ground                                                                                                                                                                                                                                                                                                                                              |

| 23          | SDO                  | 0   | SPI bus serial data output. Refer to the <i>Timing Diagrams</i> for further detail.                                                                                                                                                                                                                                                                         |

| 24          | $IOV_{DD}$           | 1   | Interface power. Connect to +1.8V for 1.8V logic, +3V for 3V logic, and to +5V for 5V logic.                                                                                                                                                                                                                                                                |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       | MIN  | MAX                     | UNIT |

|---------------------------------------|------|-------------------------|------|

| AV <sub>DD</sub> to AGND              | -0.3 | 6                       | V    |

| DV <sub>DD</sub> to DGND              | -0.3 | 6                       | V    |

| IOV <sub>DD</sub> to DGND             | -0.3 | 6                       | V    |

| Digital input voltage to DGND         | -0.3 | IOV <sub>DD</sub> + 0.3 | V    |

| V <sub>OUT</sub> to AGND              | -0.3 | $AV_{DD} + 0.3$         | V    |

| Operating temperature range           | -40  | 105                     | °C   |

| Storage temperature range             | -65  | 150                     | °C   |

| Storage temperature, T <sub>stg</sub> |      | 150                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±3000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                              |                          | MIN  | NOM | MAX       | UNIT |

|-------------------|------------------------------|--------------------------|------|-----|-----------|------|

| $AV_{DD}$         | Analog power supply          |                          | 2.7  |     | 5.5       | V    |

| $IOV_{DD}$        | Interface power supply       |                          | 1.7  |     | $AV_DD$   | V    |

| V                 | Reference high input voltage | AV <sub>DD</sub> = 5.5 V | 1.25 | 5   | $AV_{DD}$ | V    |

| V <sub>REFH</sub> | Reference high input voltage | $AV_{DD} = 3 V$          | 1.25 | 2.5 | $AV_DD$   | V    |

| V <sub>REFL</sub> | Reference low input voltage  |                          | -0.2 | 0   | 0.2       | V    |

|                   | Specified performance        |                          | -40  |     | 105       | °C   |

#### 6.4 Thermal Information

|                      |                                              | DAC8881    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN) | UNIT |

|                      |                                              | 24 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 33.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 37.1       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 11.3       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.5        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 11.4       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. .

#### 6.5 Electrical Characteristics

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = DV_{DD} = +2.7$  V to +5.5 V,  $IOV_{DD} = +1.8$  V to +5.5 V, gain = 1X mode, unless otherwise noted.

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     | CONDITIONS                                 |      | DAC8881  |           | UNIT               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------|------|----------|-----------|--------------------|

| TANAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     | CONDITIONS                                 | MIN  | TYP      | MAX       | ONIT               |

| ACCURACY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |                                            |      |          |           |                    |

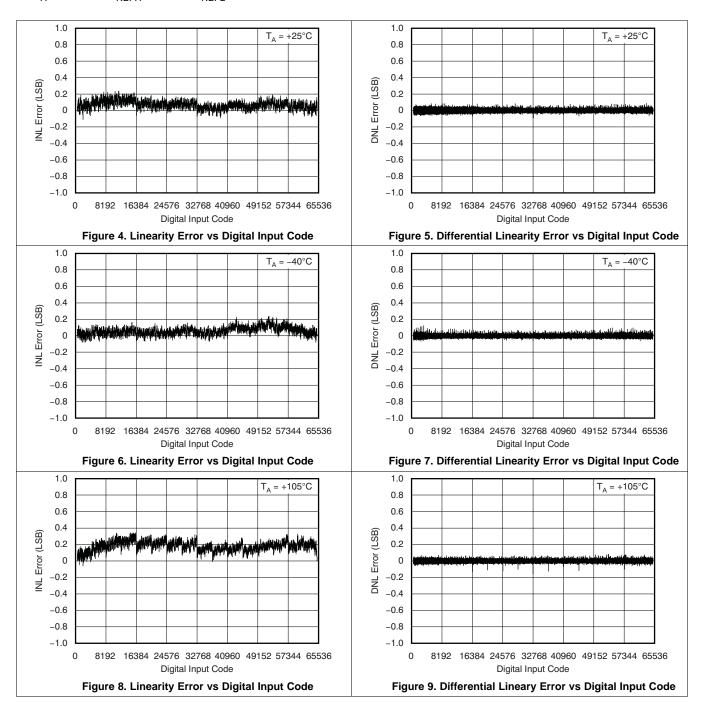

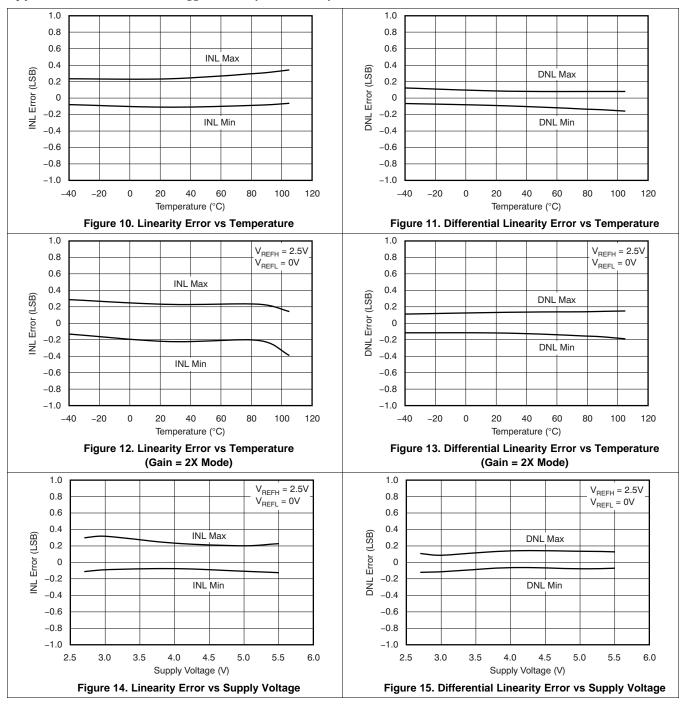

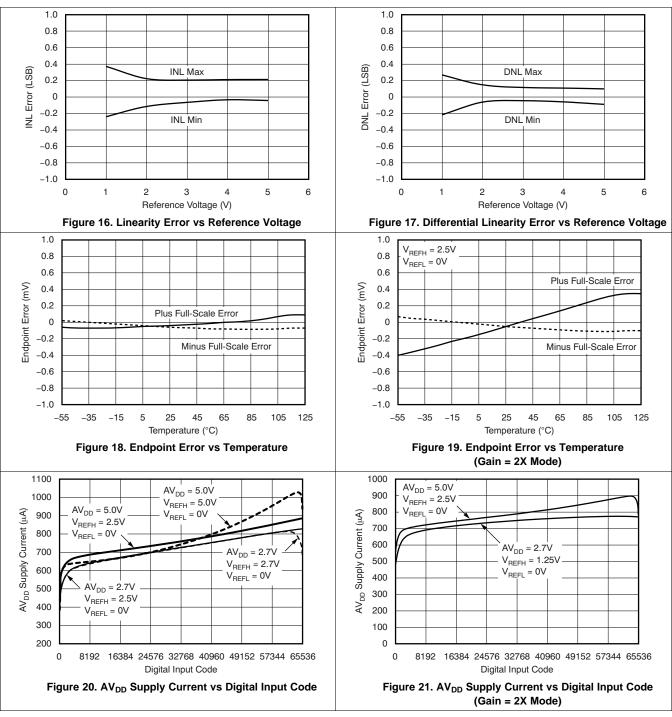

| Linearity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Measured by line pass                               | sing through codes 0200h and FE00h         |      | ±0.5     | ±1        | LSB                |

| Differential linearity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Measured by line pass                               | sing through codes 0200h and FE00h         |      | ±0.25    | ±1        | LSB                |

| Monotonicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                            | 16   |          |           | Bits               |

| Zara acala arrar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $T_A = +25^{\circ}C$ , code = 02                    | 200h                                       |      |          | ±4        | LSB                |

| Zero-scale error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $T_{MIN}$ to $T_{MAX}$ , code = 0                   | 200h                                       |      |          | ±8        | LSB                |

| Zero-scale drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Code = 0200h                                        |                                            |      | ±0.5     | ±1        | ppm/°C of FSR      |

| Gain error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | T <sub>A</sub> = +25°C, Measured<br>0200h and FE00h | I by line passing through codes            |      | ±4       | ±8        | LSB                |

| Gain temperature drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Measured by line pass                               | sing through codes 0200h and FE00h         |      | ±0.5     | ±1        | ppm/°C             |

| PSRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OUT</sub> = full-scale, AV <sub>DI</sub>     | <sub>0</sub> = +5 V ±10%                   |      |          | 2         | LSB/V              |

| ANALOG OUTPUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     | •                                          |      |          |           |                    |

| Voltage output <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                                            | 0    |          | $AV_DD$   | V                  |

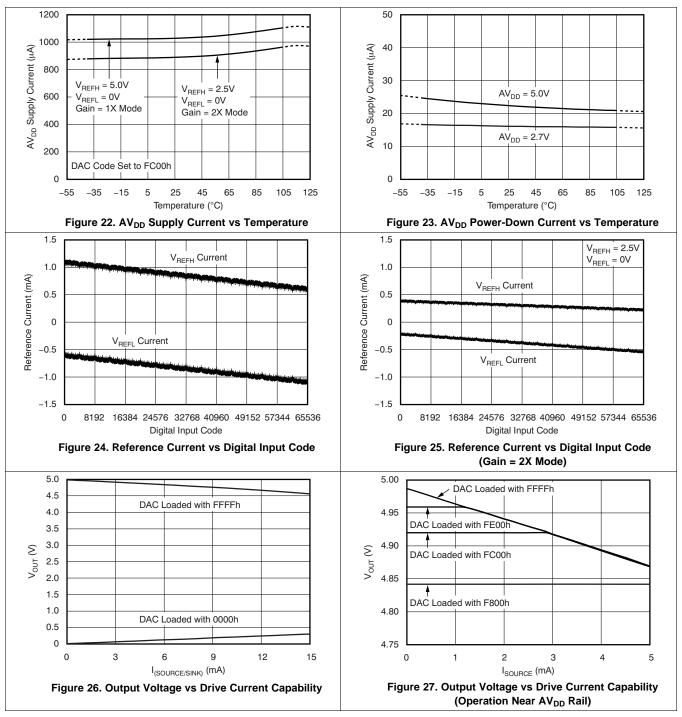

| 0 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Device operating for 5                              | 00 hours                                   |      | 5        |           | ppm of FSR         |

| Output voltage drift vs time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Device operating for 1                              | 000 hours                                  |      | 8        |           | ppm of FSR         |

| Output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |                                            |      | 2.5      |           | mA                 |

| Maximum load capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |                                            |      | 200      |           | pF                 |

| Short-circuit current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                                            |      | +31, -50 |           | mA                 |

| REFERENCE INPUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     | •                                          |      |          |           |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $AV_{DD} = +5.5 \text{ V}$                          |                                            | 1.25 | 5.0      | $AV_{DD}$ | ٧                  |

| V <sub>REFH</sub> input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $AV_{DD} = +3 V$                                    |                                            | 1.25 | 2.5      | $AV_{DD}$ | ٧                  |

| V <sub>REFH</sub> input capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |                                            |      | 5        |           | pF                 |

| V <sub>REFH</sub> input impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                                            |      | 4.5      |           | kΩ                 |

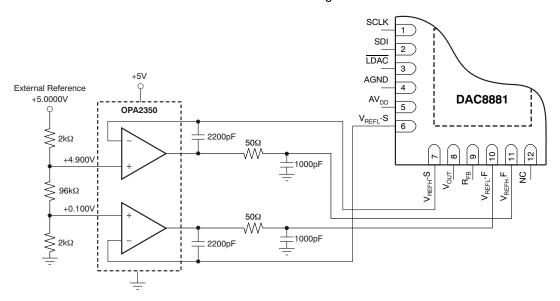

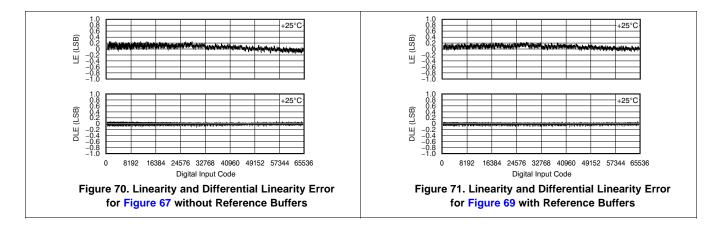

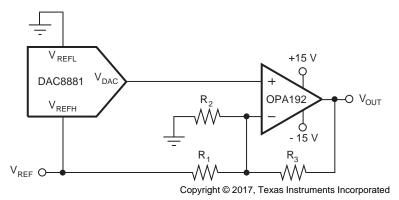

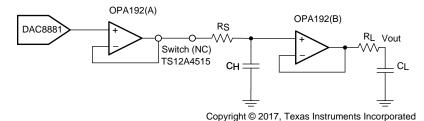

| V <sub>REFL</sub> input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                                            | -0.2 | 0        | +0.2      | V                  |