Now

**TPS4H000-Q1**

ZHCSET1B-DECEMBER 2015-REVISED MARCH 2018

# **TPS4H000-Q1 40V、1000m**Ω 四通道智能高侧开关

•

#### 特性 1

- 符合汽车应用 标准

- 具有符合 AEC-Q100 标准的下列特性:

- 器件温度 1级: -40°C 至 125°C 的环境工作温 度范围

- 器件人体放电模型 (HBM) 静电防护 (ESD) 分类 等级 H2

- 器件 CDM ESD 分类等级 C4B

- 具有丰富诊断功能的四通道 1000mΩ 智能高侧开关 ٠

- 版本 A: 开漏状态输出

- 版本 B: 电流检测模拟输出

- 宽工作电压范围: 3.4V 至 40V

- 超低待机电流: < 500nA

- 高精度电流检测:

- > 5mA 负载下为 ±15%

- 可使用外部电阻调节电流限值,>100mA的负载条 件下为 ±20%

- 保护:

- 通过(内部或外部)电流限制实现接地短路保护

- 具有锁闭选项的热关断以及热调节

- 感性负载负电压钳位,已优化转换率

- 失地保护和失电保护

- 诊断:

- 过流和接地短路检测 \_

- 负载开路和电池短路检测

- 用于实现快速中断的全局故障

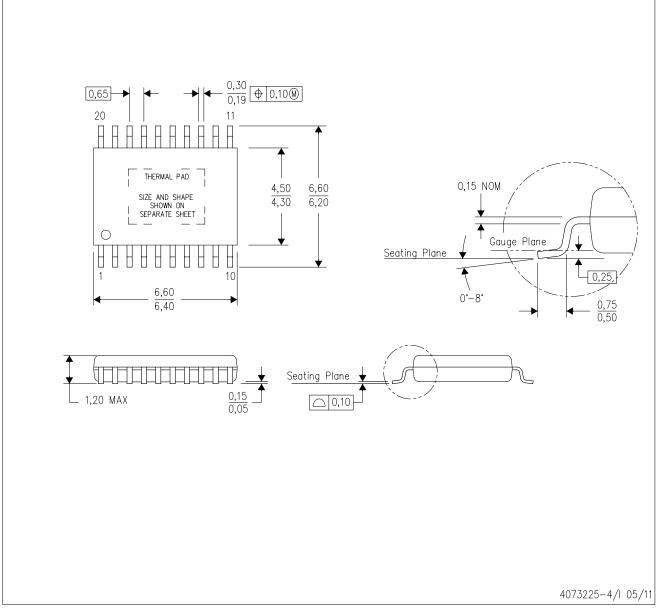

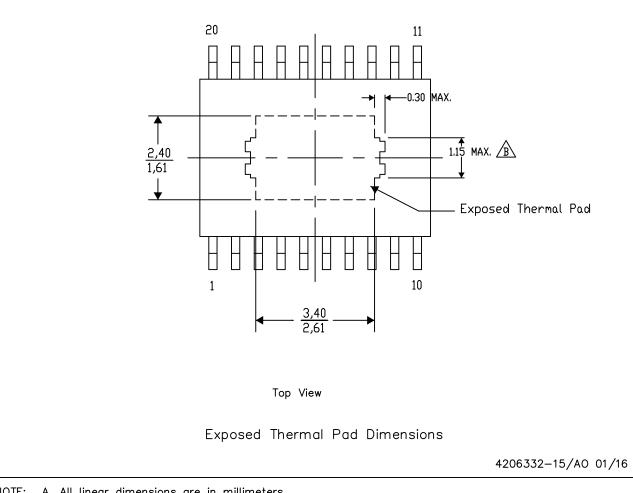

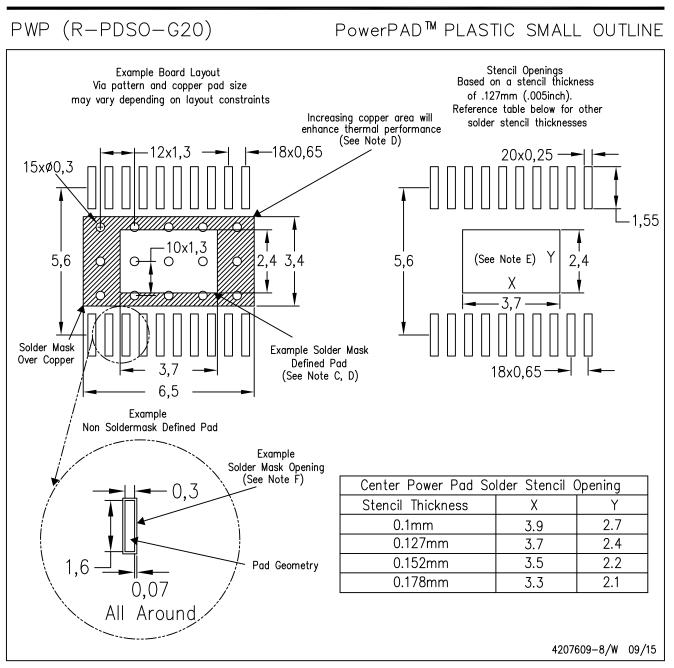

- 20 引脚耐热增强型 PWP 封装

## 2 应用

- 四通道 LED 驱动器 •

- 适用于子模块的四通道高侧开关 ٠

- 四通道高侧继电器驱动器 •

#### 3 说明

TPS4H000-Q1 系列是受到全面保护的四通道智能高侧 开关,具有集成式 1000m $\Omega$  NMOS 功率 FET。

该器件具有丰富的诊断功能和高精度电流检测 功能, 可对负载进行智能控制。

该器件可从外部调节电流限值以限制浪涌或过载电流, 从而提升整个系统的可靠性。

器件信息<sup>(1)</sup>

| 器件型号            | 封装          | 通道 |

|-----------------|-------------|----|

| TPS4H000-Q1 版本A |             | 4  |

| TPS4H000-Q1 版本B | HTSSOP (20) | 4  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

### 驱动具有可调节电流限制的电容性负载

# 目录

| 1 | 特性   |                                    |

|---|------|------------------------------------|

| 2 | 应用   |                                    |

| 3 | 说明   | 1                                  |

| 4 | 修订   | 历史记录                               |

| 5 | Dev  | ice Comparison Table 3             |

| 6 | Pin  | Configuration and Functions        |

| 7 | Spe  | cifications5                       |

|   | 7.1  | Absolute Maximum Ratings 5         |

|   | 7.2  | ESD Ratings5                       |

|   | 7.3  | Recommended Operating Conditions 5 |

|   | 7.4  | Thermal Information6               |

|   | 7.5  | Electrical Characteristics         |

|   | 7.6  | Switching Characteristics 8        |

|   | 7.7  | Typical Characteristics 10         |

| 8 | Deta | ailed Description 13               |

|   | 8.1  | Overview 13                        |

|   | 8.2  | Functional Block Diagram 14        |

|    | 8.3  | Feature Description         | 14 |

|----|------|-----------------------------|----|

|    | 8.4  | Device Functional Modes     | 24 |

| 9  | Appl | lication and Implementation | 26 |

|    | 9.1  | Application Information     | 26 |

|    |      | Typical Application         |    |

| 10 | Pow  | er Supply Recommendations   | 29 |

| 11 | Layo | out                         | 29 |

|    | 11.1 | Layout Guidelines           | 29 |

|    | 11.2 | Layout Examples             | 29 |

| 12 | 器件   | 和文档支持                       | 31 |

|    | 12.1 | 接收文档更新通知                    | 31 |

|    | 12.2 | 社区资源                        | 31 |

|    | 12.3 | 商标                          | 31 |

|    | 12.4 | 静电放电警告                      | 31 |

|    | 12.5 | Glossary                    | 31 |

| 13 | 机械   | 、封装和可订购信息                   | 31 |

|    |      |                             |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| Changes from Revision A (October 2016) to Revision B                                          | Page |

|-----------------------------------------------------------------------------------------------|------|

| Added footnote 2 to the <i>Electrical Characteristics</i> table                               |      |

| Added reverse current protection information to the <i>Reverse-Current Protection</i> section |      |

| Changes from Original (December 2015) to Revision A                                           | Page |

|                                                                                               | 1    |

www.ti.com.cn

### 5 Device Comparison Table

| PART NUMBER           | FAULT REPORTING MODE        |

|-----------------------|-----------------------------|

| TPS4H000-Q1 Version A | Open-drain digital output   |

| TPS4H000-Q1 Version B | Current-sense analog output |

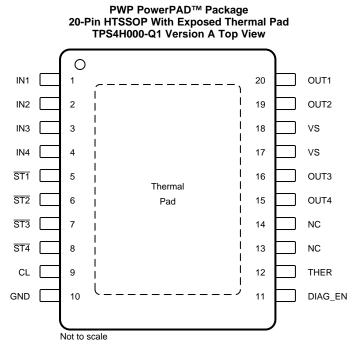

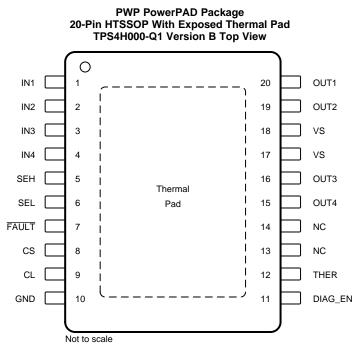

# 6 Pin Configuration and Functions

NC - No internal connection

NC – No internal connection

#### **Pin Functions**

| PIN     |           |           |     |                                                                                             |  |

|---------|-----------|-----------|-----|---------------------------------------------------------------------------------------------|--|

|         | N         | 0.        | I/O | DESCRIPTION                                                                                 |  |

| NAME    | VERSION A | VERSION B |     |                                                                                             |  |

| CL      | 9         | 9         | 0   | Adjustable current limit. Connect to device GND if external current limit is not used.      |  |

| CS      | —         | 8         | 0   | Current-sense output                                                                        |  |

| DIAG_EN | 11        | 11        | I   | Enable-disable pin for diagnostics; internal pulldown                                       |  |

| FAULT   | _         | 7         | 0   | Global fault report with open-drain structure, ORed logic for quad-channel fault conditions |  |

| GND     | 10        | 10        |     | Ground pin                                                                                  |  |

| IN1     | 1         | 1         | I   | Input control for channel 1 activation; internal pulldown                                   |  |

| IN2     | 2         | 2         | I   | Input control for channel 2 activation; internal pulldown                                   |  |

| IN3     | 3         | 3         | I   | Input control for channel 3 activation; internal pulldown                                   |  |

| IN4     | 4         | 4         | I   | Input control for channel 4 activation; internal pulldown                                   |  |

| NC      | 13, 14    | 13, 14    | _   | No internal connection                                                                      |  |

| ST1     | 5         | —         | 0   | Open-drain diagnostic status output for channel 1                                           |  |

| ST2     | 6         | —         | 0   | Open-drain diagnostic status output for channel 2                                           |  |

| ST3     | 7         | —         | 0   | Open-drain diagnostic status output for channel 3                                           |  |

| ST4     | 8         | _         | 0   | Open-drain diagnostic status output for channel 4                                           |  |

| SEH     | _         | 5         | Ι   | CS channel-selection bit; internal pulldown                                                 |  |

| SEL     | _         | 6         | I   | CS channel-selection bit; internal pulldown                                                 |  |

| THER    | 12        | 12        | I   | Thermal shutdown behavior control, latch off or auto-retry; internal pulldown               |  |

| OUT1    | 20        | 20        | 0   | Output of the channel 1 high side-switch, connected to the load                             |  |

| OUT2    | 19        | 19        | 0   | Output of the channel 2 high side-switch, connected to the load                             |  |

| OUT3    | 16        | 16        | 0   | Output of the channel 3 high side-switch, connected to the load                             |  |

| OUT4    | 15        | 15        | 0   | Output of the channel 4 high side-switch, connected to the load                             |  |

| VS      | 17, 18    | 17, 18    | Ι   | Power supply                                                                                |  |

#### 4

### **Pin Functions (continued)**

| PIN NAME NO. |           |           |             |                                         |

|--------------|-----------|-----------|-------------|-----------------------------------------|

|              |           | I/O       | DESCRIPTION |                                         |

| NAME         | VERSION A | VERSION B |             |                                         |

| Thermal pad  | _         | _         |             | Connect to device GND or leave floating |

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted) (1)(2)

|                                                                                           |                                                | M  | IN  | MAX | UNIT |

|-------------------------------------------------------------------------------------------|------------------------------------------------|----|-----|-----|------|

| Supply voltage                                                                            | t < 400 ms                                     |    |     | 45  | V    |

| Reverse polarity voltage <sup>(3)</sup>                                                   | bitage       t < 400 ms                        |    | V   |     |      |

| Current on GND pin                                                                        | t < 2 minutes                                  | -1 | 00  | 250 | mA   |

| Voltage on INx, DIAG_EN, SE                                                               | L, and THER pins                               | _( | 0.3 | 7   | V    |

| Current on INx, DIAG_EN, SE                                                               | L, and THER pins                               | -  | 10  | _   | mA   |

| Voltage on STx or FAULT pins                                                              |                                                | -( | 0.3 | 7   | V    |

| Current on STx or FAULT pins                                                              |                                                | -  | 30  | 10  | mA   |

| Voltage on CS pin                                                                         | Voltage on CS pin                              |    | 2.7 | 7   | V    |

| Current on CS pin                                                                         |                                                | -  | _   | 30  | mA   |

| Voltage on CL pin                                                                         |                                                | _( | 0.3 | 7   | V    |

| Current on CL pin                                                                         |                                                | -  | _   | 6   | mA   |

| Inductive load switch-off energy dissipation, single pulse, single channel <sup>(4)</sup> |                                                | -  |     | 40  | mJ   |

| Operating junction temperatur                                                             | Dperating junction temperature, T <sub>J</sub> |    | 40  | 150 | °C   |

| Storage temperature, T <sub>stg</sub>                                                     |                                                | -  | 65  | 150 | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All unitaries values are with respect to the ground place.

(2) All voltage values are with respect to the ground plane.

(3) Reverse polarity condition: t < 60 s, reverse current < I<sub>R(2)</sub>, V<sub>INx</sub> = 0 V, all channels reverse, GND pin 1-kΩ resistor in parallel with diode.

(4) Test condition: V<sub>VS</sub> = 13.5 V, L = 300 mH, T<sub>J</sub> = 150°C. FR4 2s2p board, 2 × 70-µm Cu, 2 × 35-µm Cu. 600 mm<sup>2</sup> thermal pad copper area.

### 7.2 ESD Ratings

|                    |                         |                                                         |                               | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins                      | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC                     | All pins                      | ±750  | V    |

|                    |                         | Q100-011                                                | Corner pins (1, 8, 9, and 16) | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                |                                             | MIN | MAX  | UNIT |

|----------------|---------------------------------------------|-----|------|------|

| $V_{VS}$       | Supply operating voltage                    | 4   | 40   | V    |

|                | Voltage on INx, DIAG EN, SEL, and THER pins | 0   | 5    | V    |

|                | Voltage on STx and FAULT pins               | 0   | 5    | V    |

|                | Nominal dc load current                     | 0   | 0.75 | А    |

| T <sub>A</sub> | Operating ambient temperature               | -40 | 125  | °C   |

### TPS4H000-Q1

ZHCSET1B-DECEMBER 2015-REVISED MARCH 2018

ÈXAS

www.ti.com.cn

### 7.4 Thermal Information

|                       |                                              | TPS4H000-Q1  |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 20 PINS      |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 38.5         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.5         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20.7         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.7          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 20.5         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.7          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

5 V < V\_{VS} < 40 V; -40°C <  $T_{\rm J}$  < 150°C, unless otherwise specified)

|                         | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                                                       | MIN | TYP  | MAX  | UNIT  |

|-------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| OPERATIN                | G VOLTAGE                                                      |                                                                                                                                                                                       |     |      |      |       |

| V <sub>VS(nom)</sub>    | Nominal operating voltage                                      |                                                                                                                                                                                       | 4   |      | 40   | V     |

| V <sub>VS(uvr)</sub>    | Undervoltage turnon                                            | V <sub>VS</sub> rises up                                                                                                                                                              | 3.5 | 3.7  | 4    | V     |

| V <sub>VS(uvf)</sub>    | Undervoltage shutdown                                          | V <sub>VS</sub> falls down                                                                                                                                                            | 3   | 3.2  | 3.4  | V     |

| V <sub>(uv,hys)</sub>   | Undervoltage shutdown, hysteresis                              |                                                                                                                                                                                       |     | 0.5  |      | V     |

| ,                       | G CURRENT                                                      |                                                                                                                                                                                       |     |      |      |       |

| I <sub>(op)</sub>       | Nominal operating current <sup>(1)</sup>                       | $\label{eq:VVS} \begin{array}{l} V_{VS} = 13.5 \ V, \ V_{INx} = 5 \ V, \ V_{DIAG\_EN} = 0 \ V, \ I_{OUTx} = 0.1 \ A, \\ current \ limit = 0.5 \ A, \ all \ channels \ on \end{array}$ |     |      | 7    | mA    |

| h                       | Standby current                                                | $V_{VS}$ = 13.5 V, $V_{INx}$ = $V_{DIAG\_EN}$ = $V_{CS}$ = $V_{CL}$ = $V_{OUTx}$ = THER = 0 V, $T_{\rm J}$ = 25°C                                                                     |     |      | 0.5  | μA    |

| I <sub>(off)</sub>      |                                                                | $\label{eq:VVS} \begin{array}{l} V_{VS}=13.5 \mbox{ V},  V_{INx}=V_{DIAG\_EN}=V_{CS}=V_{CL}=V_{OUTx}=THER=0  V, \\ T_J=125^{\circ}C \end{array}$                                      |     |      | 3    | p, r  |

| I <sub>(off,diag)</sub> | Standby current with diagnostic<br>enabled                     | $V_{VS}$ = 13.5 V, $V_{INx}$ = 0 V, $V_{DIAG\_EN}$ = 5 V, $V_{VS}-V_{OUTx}$ > $V_{(ol,off)}$ not in open-load mode                                                                    |     |      | 3    | mA    |

| t <sub>(off,diag)</sub> | Standby mode deglitch time <sup>(1)</sup>                      | IN from high to low, if deglitch time > $t_{\rm (off,deg)},$ the device enters into standby mode.                                                                                     | 10  | 12.5 | 15   | ms    |

| I <sub>lkg(out)</sub>   | Output leakage current in off-state                            | $V_{VS} = 13.5 \text{ V},  V_{INx} = V_{OUTx} = 0,  V_{DIAG\_EN} = 5 \text{ V}$                                                                                                       |     |      | 2    | μA    |

| POWER ST                | AGE                                                            |                                                                                                                                                                                       |     |      |      |       |

| -                       | On state resistance $^{(1)}$                                   | $V_{VS} \ge 3.5 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$                                                                                                                        |     | 1000 |      | mΩ    |

| r <sub>DS(on)</sub>     | On-state resistance <sup>(1)</sup>                             | $V_{VS} \ge 3.5 \text{ V}, \text{ T}_{J} = 150^{\circ}\text{C}$                                                                                                                       |     |      | 2000 | 11122 |

| I <sub>CL(int)</sub>    | Internal current limit                                         | Internal current limit value, CL pin connected to GND                                                                                                                                 | 1   |      | 1.6  | А     |

|                         | Current limit during thermal                                   | Internal current limit value under thermal shutdown                                                                                                                                   |     | 0.8  |      | А     |

| I <sub>CL(TSD)</sub>    | Current limit during thermal shutdown <sup>(1)</sup>           | External current limit value under thermal shutdown. The percentage of the external current limit setting value                                                                       |     | 60%  |      |       |

| V <sub>DS(clamp)</sub>  | Drain-to-source internal clamp voltage                         |                                                                                                                                                                                       | 46  |      | 65   | V     |

| OUTPUT D                | ODE CHARACTERISTICS                                            |                                                                                                                                                                                       |     |      |      |       |

| V <sub>F</sub>          | Drain-source diode voltage                                     | $IN = 0, I_{OUTx} = -0.15 A.$                                                                                                                                                         | 0.3 | 0.8  | 1    | V     |

|                         |                                                                | $t < 60 \text{ s}, \text{ V}_{\text{INx}} = 0 \text{ V},  \text{T}_{\text{J}} = 25^{\circ}\text{C}, \text{ single channel reversed, short-to-battery condition}$                      |     | 1    |      |       |

| $I_{R(1),} I_{R(2)}$    | Continuous reverse current from source to drain <sup>(1)</sup> | $t<60~s,~V_{INx}$ = 0 V, GND pin 1-k $\Omega$ resistor in parallel with diode. $T_J$ = 25°C. Reverse-polarity condition, all channels reversed                                        |     | 1    |      | A     |

| LOGIC INP               | UT (INx, DIAG_EN, SEL, THER)                                   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                 |     |      |      |       |

| V <sub>IH</sub>         | Logic high-level voltage                                       |                                                                                                                                                                                       | 2   |      |      | V     |

| V <sub>IL</sub>         | Logic low-level voltage                                        |                                                                                                                                                                                       |     |      | 0.8  | V     |

| R <sub>(logic,pd)</sub> | Logic-pin pulldown resistor                                    | INx, SEL, THER, $V_{INx} = V_{SEL} = V_{THER} = 5 V$                                                                                                                                  | 100 | 175  | 250  | kΩ    |

|                         |                                                                | DIAG_EN. $V_{VS} = V_{DIAG_EN} = 5 V$                                                                                                                                                 | 150 | 275  | 400  |       |

(1) Value specified by design, not subject to production test

# **Electrical Characteristics (continued)**

### 5 V < $V_{VS}$ < 40 V; -40°C < $T_J$ < 150°C, unless otherwise specified)

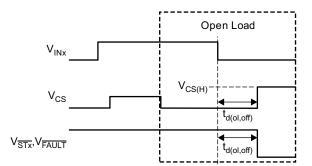

|                                           | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                   | MIN                                                                      | TYP | MAX                      | UNIT |

|-------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|--------------------------|------|

| DIAGNOSTIC                                | :s                                                                                |                                                                                                                                   |                                                                          |     |                          |      |

| I <sub>lkg(GND_loss)</sub>                | Output leakage current under GND loss condition                                   |                                                                                                                                   |                                                                          |     | 100                      | μA   |

| V <sub>(ol,off)</sub>                     | Open-load detection threshold                                                     | $IN$ = 0 V, when $V_{VS}-V_{OUTx}$ < $V_{(ol,off)}$ , duration longer than $t_{(ol,off)}$ , then open load is detected, off state | 1.6                                                                      |     | 2.6                      | V    |

| t <sub>d(ol,off)</sub>                    | Open-load detection threshold deglitch time (see Figure 3)                        | $IN$ = 0 V, when $V_{VS}-V_{OUTx}$ < $V_{(ol,off)}$ , duration longer than $t_{(ol,off)}$ , then open load is detected, off state | 300                                                                      | 600 | 800                      | μs   |

| I <sub>(ol,off)</sub>                     | Off-state output sink current                                                     | $V_{INx}$ = 0 V, $V_{DIAG\_EN}$ = 5 V, $V_{VS}$ = $V_{OUTx}$ = 13.5 V, $T_J$ = 125°C, open load                                   | -75                                                                      |     |                          | μA   |

| V <sub>OL(STx)</sub>                      | Status low-output voltage                                                         | I <sub>STx</sub> = 2 mA, version A only                                                                                           |                                                                          |     | 0.2                      | V    |

| V <sub>OL(FAULT)</sub>                    | Fault low-output voltage                                                          | $I_{FAULT} = 2 \text{ mA}$ , version B only                                                                                       |                                                                          |     | 0.2                      | V    |

| t <sub>CL(deg)</sub>                      | Deglitch time when current limit occurs <sup>(1)</sup>                            | $V_{INx} = V_{DIAG EN} = 5 V$ , the deglitch time from current limit toggling to FAULT, STx, CS report.                           | 80                                                                       |     | 180                      | μs   |

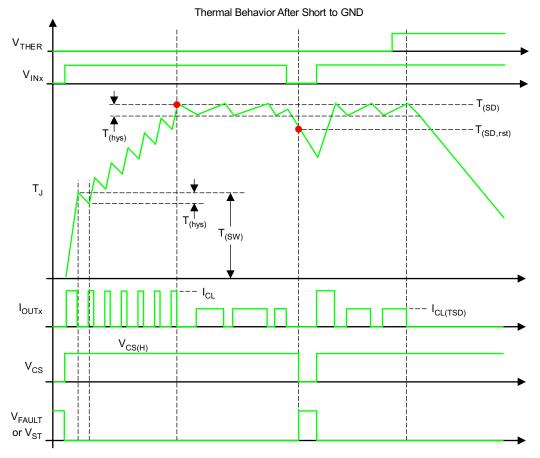

| T <sub>(SD)</sub>                         | Thermal shutdown threshold <sup>(1)</sup>                                         |                                                                                                                                   | 160                                                                      | 175 |                          | °C   |

| T <sub>(SD,rst)</sub>                     | Thermal shutdown status reset threshold <sup>(1)</sup>                            |                                                                                                                                   |                                                                          | 155 |                          | °C   |

| T <sub>(SW)</sub>                         | Thermal swing shutdown threshold <sup>(1)</sup>                                   |                                                                                                                                   |                                                                          | 60  |                          | °C   |

| T <sub>(hys)</sub>                        | Hysteresis for resetting the thermal shutdown or thermal swing <sup>(1)</sup>     |                                                                                                                                   |                                                                          | 10  |                          | °C   |

| CURRENT S                                 | ENSE (Version B) AND CURRENT LIMI                                                 | т                                                                                                                                 |                                                                          |     |                          |      |

| K <sub>(CS)</sub>                         | Current-sense ratio                                                               |                                                                                                                                   |                                                                          | 80  |                          |      |

| K <sub>(CL)</sub>                         | Current-limit ratio                                                               |                                                                                                                                   |                                                                          | 300 |                          |      |

| V <sub>CL(th)</sub>                       | Current limit internal threshold <sup>(1)</sup>                                   |                                                                                                                                   |                                                                          | 0.8 |                          | V    |

|                                           |                                                                                   | $V_{VS}$ = 13.5 V, $I_{OUTx} \ge 1 \text{ mA}$                                                                                    | -70%                                                                     |     | 70%                      |      |

|                                           |                                                                                   | $V_{VS}$ = 13.5 V, $I_{OUTx} \ge 2 \text{ mA}$                                                                                    | -45%                                                                     |     | 45%                      |      |

| dK <sub>(CS)</sub> /<br>K <sub>(CS)</sub> | Current-sense accuracy, $(I_{CS} \times K_{(CS)} - I_{OUTx})/I_{OUTx} \times 100$ | $V_{VS}$ = 13.5 V, $I_{OUTx} \ge 5 \text{ mA}$                                                                                    | -15%                                                                     |     | 15%                      |      |

| (03)                                      |                                                                                   | V <sub>VS</sub> = 13.5 V, I <sub>OUTx</sub> ≥ 25 mA                                                                               | -5%                                                                      |     | 5%                       |      |

|                                           |                                                                                   | $V_{VS}$ = 13.5 V, $I_{OUTx} \ge 100 \text{ mA}$                                                                                  | -3%                                                                      |     | 3%                       |      |

|                                           |                                                                                   | $V_{VS}$ = 13.5 V, $I_{(limit)} \ge 50 \text{ mA}$                                                                                | -25%                                                                     |     | 25%                      |      |

| dK /K                                     | External current limit accuracy <sup>(2)</sup>                                    | I <sub>(limit)</sub> ≥ 100 mA                                                                                                     | -20%                                                                     |     | 20%                      |      |

| dK <sub>(CL)</sub> / K <sub>(CL)</sub>    | $(I_{OUTx} - I_{CL} \times K_{(CL)}) \times 100 / (I_{CL} \times K_{(CL)})$       | I <sub>(limit)</sub> ≥ 200 mA                                                                                                     | -15%                                                                     |     | 15%                      |      |

|                                           |                                                                                   | $V_{VS}$ = 13.5 V, 0.5 A ≤ I <sub>(limit)</sub> ≤ 0.9 A                                                                           | -10%                                                                     |     | 10%                      |      |

|                                           |                                                                                   | V <sub>VS</sub> ≥ 6.5 V                                                                                                           | 0                                                                        |     | 4                        |      |

| V <sub>CS(lin)</sub>                      | Current-sense voltage linear range <sup>(1)</sup>                                 | $5 \text{ V} \leq \text{V}_{\text{VS}} < 6.5 \text{ V}$                                                                           | 0                                                                        |     | V <sub>VS</sub> –<br>2.5 | V    |

|                                           | Output-current linear range <sup>(1)</sup>                                        | $V_{VS}$ = 13.5 V, $V_{CS(lin)} \le 4$ V                                                                                          | 0                                                                        |     | 0.75                     | А    |

| I <sub>OUTx(lin)</sub>                    |                                                                                   | 5 V $\leq$ V <sub>VS</sub> $< 6.5$ V, V <sub>CS(lin)</sub> $\leq$ V <sub>VS</sub> $-$ 2.5 V                                       | 0                                                                        |     | 0.5                      | ~    |

|                                           |                                                                                   | $V_{VS} \ge 7 V$ , fault mode                                                                                                     | 4.5                                                                      |     | 6.5                      | V    |

| V <sub>CS(H)</sub>                        | Current sense pin output voltage <sup>(1)</sup>                                   | 5 V $\leq$ V <sub>VS</sub> $<$ 7 V, fault mode                                                                                    | $\begin{array}{c} \text{Min}(\text{V}_{\text{VS}}-2,\\ 4.5) \end{array}$ |     | 6.5                      | V    |

| I <sub>CS(H)</sub>                        | Current-sense pin output current                                                  | $V_{CS} = 4.5 \text{ V}, V_{VS} = 13.5 \text{ V}$                                                                                 | 15                                                                       |     |                          | mA   |

| I <sub>lkg(CS)</sub>                      | Current-sense leakage current in<br>disabled mode                                 | $V_{DIAG_EN} = 0 \text{ V}, \text{ T}_J = 125^{\circ}\text{C}$                                                                    |                                                                          |     | 0.5                      | μA   |

(2) External current limit accuracy is only applicable to overload conditions greater than 1.5 x the current limit setting

### TPS4H000-Q1

ZHCSET1B-DECEMBER 2015-REVISED MARCH 2018

www.ti.com.cn

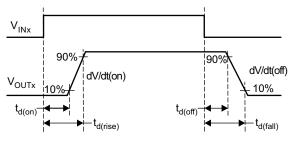

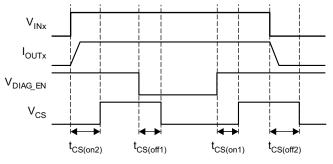

## 7.6 Switching Characteristics

|                       | PARAMETER                                                                     | TEST CONDITIONS                                                                                                                                                                                                                 | MIN | TYP  | MAX | UNIT |

|-----------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>d(on)</sub>    | Delay time, V <sub>OUTx</sub> 10% after V <sub>INx</sub> ↑ (See<br>Figure 1.) | $V_{VS}$ = 13.5 V, $V_{DIAG\_EN}$ = 5 V, $I_{OUTx}$ = 0.1 A, IN rising edge to 10% of $V_{OUTx}$                                                                                                                                | 10  | 30   | 60  | μs   |

| t <sub>d(off)</sub>   | Delay time, V <sub>OUTx</sub> 90% after V <sub>INx</sub> ↓ (See<br>Figure 1.) | $V_{VS}$ = 13.5 V, $V_{DIAG\_EN}$ = 5 V, $I_{OUTx}$ = 0.1 A, IN falling edge to 90% of $V_{OUTx}$                                                                                                                               | 10  | 30   | 60  | μs   |

| dV/dt(on)             | Turnon slew rate                                                              | $V_{VS}$ = 13.5 V, $V_{DIAG\_EN}$ = 5 V, $I_{OUTx}$ = 0.1 A, $V_{OUTx}$ from 10% to 90%                                                                                                                                         | 0.1 | 0.25 | 0.5 | V/µs |

| dV/dt(off)            | Turnoff slew rate                                                             | $V_{VS}$ = 13.5 V, $V_{DIAG\_EN}$ = 5 V, $I_{OUTx}$ = 0.1 A, $V_{OUTx}$ from 90% to 10%                                                                                                                                         | 0.3 | 0.5  | 0.9 | V/µs |

| t <sub>d(match)</sub> | $t_{d(rise)} - t_{d(fall)} \text{ (See Figure 1.)}$                           | $ \begin{array}{l} V_{VS}=13.5 \; V, \; I_L=0.1 \; A. \; t_{d, \; rise} \; is \; the \; IN \; rising \; edge \; to \\ V_{OUTx}=90\%. \\ t_{d(fall)} \; is \; the \; IN \; falling \; edge \; to \; V_{OUTx}=10\%. \end{array} $ | -60 |      | 60  | μs   |

| CURRENT-              | SENSE CHARACTERISTICS (See Figure 2.)                                         |                                                                                                                                                                                                                                 |     |      |     |      |

| t <sub>CS(off1)</sub> | CS settling time from DIAG_EN disabled $^{\left( 1\right) }$                  | $V_{VS}$ = 13.5 V, $V_{INx}$ = 5 V, $I_{OUTx}$ = 0.1 A. current limit = 0.5 A. DIAG_EN falling edge to 10% of $V_{CS}.$                                                                                                         |     |      | 20  | μs   |

| t <sub>CS(on1)</sub>  | CS settling time from DIAG_EN enabled <sup>(1)</sup>                          | $V_{VS}$ = 13.5 V, $V_{INx}$ = 5 V, $I_{OUTx}$ = 0.1 A. current limit is 0.5 A. DIAG_EN rising edge to 90% of $V_{CS}.$                                                                                                         |     |      | 20  | μs   |

| t <sub>CS(off2)</sub> | CS settling time from IN falling edge                                         | $V_{VS}$ = 13.5 V, $V_{DIAG\_EN}$ = 5 V, $I_{OUTx}$ = 0.1 A. current limit = 0.5 A. IN falling edge to 10% of $V_{CS}$                                                                                                          |     |      | 70  | μs   |

| t <sub>CS(on2)</sub>  | CS settling time from IN rising edge                                          | $V_{VS}$ = 13.5 V, $V_{DIAG\_EN}$ = 5 V, $I_{OUTx}$ = 0.1 A. current limit = 0.5 A. IN rising edge to 90% of $V_{CS}$                                                                                                           | 40  |      | 120 | μs   |

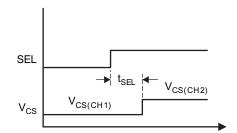

| t <sub>SEL</sub>      | Multi-sense transition delay from channel to channel                          | $V_{\text{DIAG\_EN}}$ = 5 V, current sense output delay when multi-sense pin SEL transitions from channel to channel                                                                                                            |     |      | 50  | μs   |

(1) Value specified by design, not subject to production test

### Figure 1. Output Delay Characteristics

Figure 2. CS Delay Characteristics

Figure 3. Open-Load Blanking-Time Characteristics

Figure 4. Multi-Sense Transition Delay

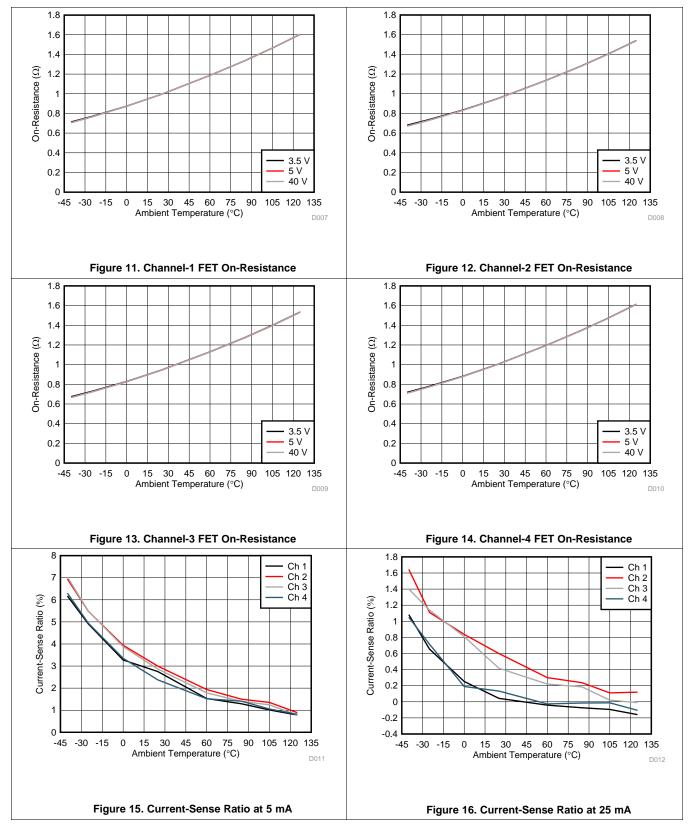

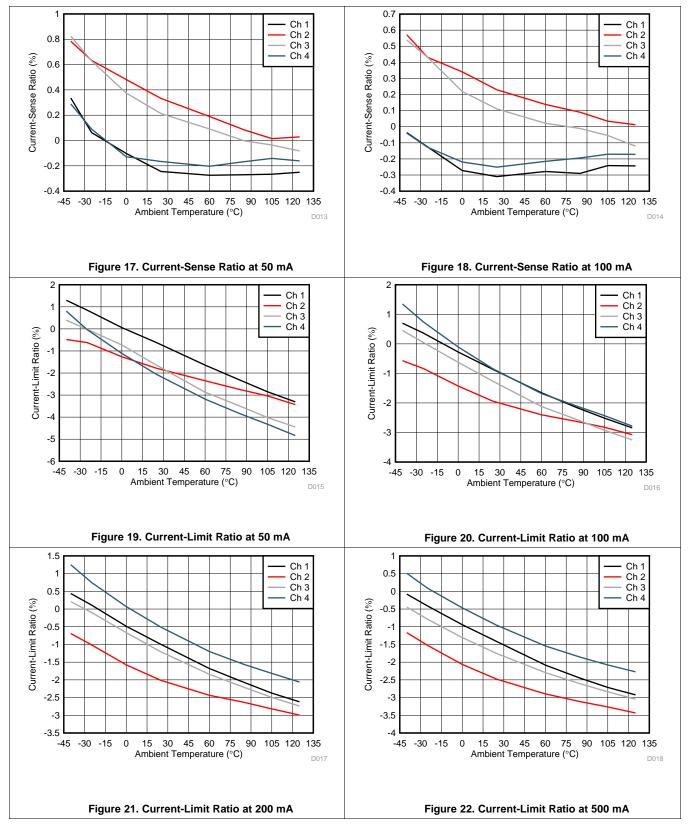

### 7.7 Typical Characteristics

### **Typical Characteristics (continued)**

ZHCSET1B-DECEMBER 2015-REVISED MARCH 2018

www.ti.com.cn

### **Typical Characteristics (continued)**

### 8 Detailed Description

### 8.1 Overview

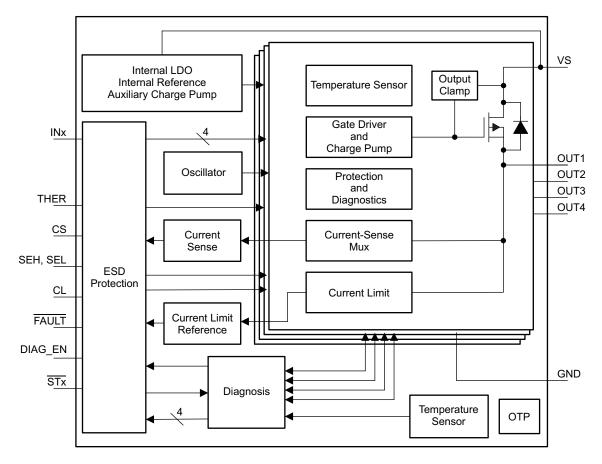

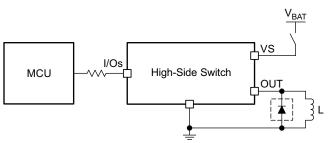

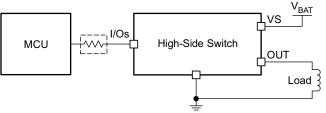

The TPS4H000-Q1 device is a smart high-side switch, with internal charge pump and quad-channel integrated NMOS power FETs. Full diagnostics and high-accuracy current-sense features enable intelligent control of the load. The adjustable current-limit function greatly improves the reliability of whole system. The device has two versions with different diagnostic reporting, the open-drain digital output (version A) and the current-sense analog output (version B).

For version A, the device implements the digital fault report with an open-drain structure. When a fault occurs, the device pulls STx down to GND. A 3.3- or 5-V external pullup is required to match the microcontroller supply level. The digital status of each channel can report individually, or globally by connecting the STx pins together.

For version B, high-accuracy current sense makes the diagnostics more accurate without further calibration. One integrated current mirror can source 1 /  $K_{(CS)}$  of the load current. The mirrored current flows into the CS-pin resistor to become a voltage signal.  $K_{(CS)}$  is a constant value across temperature and supply voltage. A wide linear region from 0 V to 4 V allows a better real-time load-current monitoring. The CS pin can also report a fault with pullup voltage of  $V_{CS(H)}$ .

The external high-accuracy current limit allows setting the current-limit value by applications. When overcurrent occurs, the device improves system reliability by clamping the inrush current effectively. The device can also save system cost by reducing the size of PCB traces and connectors, and the capacity of the preceding power stage. Besides, the device also implements an internal current limit with a fixed value.

For inductive loads (relays, solenoids, valves), the device implements an active clamp between drain and source to protect itself. During the inductive switching-off cycle, both the energy of the power supply and the load are dissipated on the high-side switch. The device also optimizes the switching-off slew rate when the clamp is active, which helps the system design by keeping the effects of transient power and EMI to a minimum.

The TPS4H000-Q1 device is a smart high-side switch for a wide variety of resistive, inductive, and capacitive loads, including LEDs, relays, and sub-modules.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Pin Current and Voltage Conventions

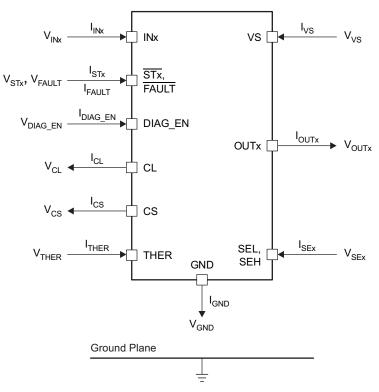

For reference purposes throughout the data sheet, current directions on their respective pins are as shown by the arrows in Figure 23. All voltages are measured relative to the ground plane.

### Feature Description (continued)

Figure 23. Voltage and Current Conventions

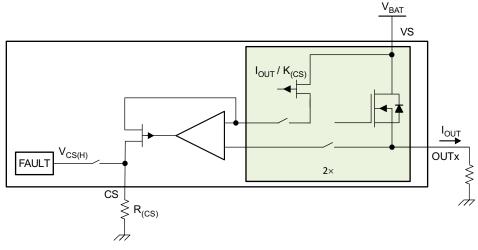

### 8.3.2 Accurate Current Sense

High-accuracy current sense is implemented in the version-B device. It allows a better real-time monitoring effect and more-accurate diagnostics without further calibration.

One integrated current mirror can source 1 /  $K_{(CS)}$  of the load current, and the mirrored current flows into the external current sense resistor to become a voltage signal. The current mirror is shared by the quad channels.  $K_{(CS)}$  is the ratio of the output current and the sense current. It is a constant value across the temperature and supply voltage. Each device is calibrated accurately during production, so post-calibration is not required. See Figure 24 for more details.

Figure 24. Current-Sense Block Diagram

(1)

### Feature Description (continued)

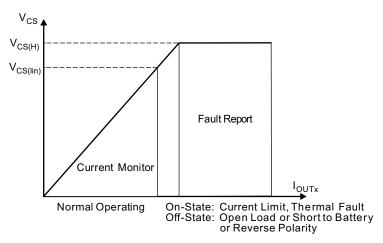

When a fault occurs, the CS pin also works as a fault report with a pullup voltage,  $V_{CS(H)}$ . See Figure 25 for more details.

Figure 25. Current-Sense Output-Voltage Curve

Use Equation 1 to calculate  $R_{(CS)}$ .

$$\mathsf{R}_{(\mathsf{CS})} = \frac{\mathsf{V}_{\mathsf{CS}}}{\mathsf{I}_{\mathsf{CS}}} = \frac{\mathsf{V}_{\mathsf{CS}} \times \mathsf{K}_{(\mathsf{CS})}}{\mathsf{I}_{\mathsf{OUTx}}}$$

Take the following points into consideration when calculating  $R_{(CS)}$ .

Ensure  $V_{CS}$  is within the current-sense linear region ( $V_{CS}$ ,  $I_{OUTx(lin)}$ ) across the full range of the load current. Check  $R_{(CS)}$  with Equation 2.

$$\mathsf{R}_{(\mathsf{CS})} = \frac{\mathsf{V}_{\mathsf{CS}}}{\mathsf{I}_{\mathsf{CS}}} \le \frac{\mathsf{V}_{\mathsf{CS}(\mathsf{lin})}}{\mathsf{I}_{\mathsf{CS}}} \tag{2}$$

• In fault mode, ensure  $I_{CS}$  is within the source capacity of the CS pin ( $I_{CS(H)}$ ). Check  $R_{(CS)}$  with Equation 3.

$$\mathsf{R}_{(\mathsf{CS})} = \frac{\mathsf{V}_{\mathsf{CS}}}{\mathsf{I}_{\mathsf{CS}}} \ge \frac{\mathsf{V}_{\mathsf{CS}(\mathsf{H},\mathsf{min})}}{\mathsf{I}_{\mathsf{CS}(\mathsf{H},\mathsf{min})}} \tag{3}$$

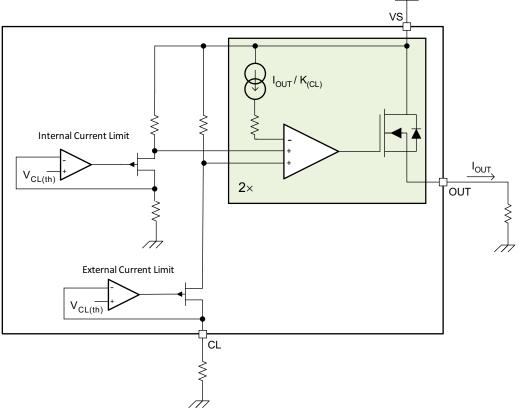

### 8.3.3 Adjustable Current Limit

A high-accuracy current limit allows high reliability of the design. It protects the load and the power supply from overstressing during short-circuit-to-GND or power-up conditions. The current limit can also save system cost by reducing the size of PCB traces and connectors, and the capacity of the preceding power stage.

When a current-limit threshold is hit, a closed loop activates immediately. The output current is clamped at the set value, and a fault is reported out. The device heats up due to the high power dissipation on the power FET. If thermal shutdown occurs, the current limit is set to  $I_{CL(TSD)}$  to reduce the power dissipation on the power FET. See Figure 26 for more details.

The device has two current-limit thresholds.

- Internal current limit The internal current limit is fixed at I<sub>CL(int)</sub>. Tie the CL pin directly to the device GND for large-transient-current applications.

- External adjustable current limit An external resistor is used to set the current-limit threshold. Use the

Equation 4 to calculate the R<sub>(CL)</sub>. V<sub>CL(th)</sub> is the internal band-gap voltage. K<sub>(CL)</sub> is the ratio of the output current

and the current-limit set value. It is constant across the temperature and supply voltage. The external

adjustable current limit allows the flexibility to set the current limit value by applications.

(4)

### **Feature Description (continued)**

$$\begin{split} I_{CL} &= \frac{V_{CL(th)}}{R_{(CL)}} = \frac{I_{OUT}}{K_{(CL)}} \\ R_{(CL)} &= \frac{V_{CL(th)} \times K_{(CL)}}{I_{OUT}} \\ \end{split}$$

Figure 26. Current-Limit Block Diargam

Note that if using a GND network which causes a level shift between the device GND and board GND, the CL pin must be connected with device GND.

For better protection from a hard short-to-GND condition (when the INx pins are enabled, a short to GND occurs suddenly), the device implements a fast-trip protection to turn off the related channel before the current-limit closed loop is set up. The fast-trip response time is less than 1  $\mu$ s, typically. With this fast response, the device can achieve better inrush current-suppression performance.

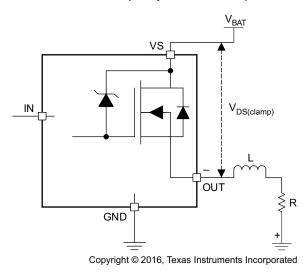

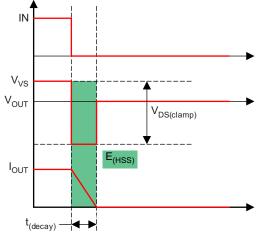

### 8.3.4 Inductive-Load Switching-Off Clamp

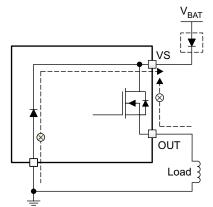

When switching an inductive load off, the inductive reactance tends to pull the output voltage negative. Excessive negative voltage could cause the power FET to break down. To protect the power FET, an internal clamp between drain and source is implemented, namely  $V_{DS(clamp)}$ .

$$V_{DS(clamp)} = V_{VS} - V_{OUT}$$

During the period of demagnetization ( $t_{decay}$ ), the power FET is turned on for inductance-energy dissipation. The total energy is dissipated in the high-side switch. Total energy includes the energy of the power supply ( $E_{(VS)}$ ) and the energy of the load ( $E_{(load)}$ ). If resistance is in series with inductance, some of the load energy is dissipated on the resistance.

(5)

(6)

### Feature Description (continued)

18

$$\mathsf{E}_{(\mathsf{HSS})} = \mathsf{E}_{(\mathsf{VS})} + \mathsf{E}_{(\mathsf{load})} = \mathsf{E}_{(\mathsf{VS})} + \mathsf{E}_{(\mathsf{L})} - \mathsf{E}_{(\mathsf{R})}$$

When an inductive load switches off,  $E_{(HSS)}$  causes high thermal stressing on the device.. The upper limit of the power dissipation depends on the device intrinsic capacity, ambient temperature, and board dissipation condition.

Figure 27. Drain-to-Source Clamping Structure

Figure 28. Inductive Load Switching-Off Diagram

From the perspective of the high-side switch, E(HSS) equals the integration value during the demagnetization period.

$$\begin{split} E_{(HSS)} &= \int_{0}^{t_{(decay)}} V_{DS(clamp)} \times I_{OUT}(t) dt \\ t_{(decay)} &= \frac{L}{R} \times ln \left( \frac{R \times I_{OUT(max)} + |V_{OUT}|}{|V_{OUT}|} \right) \\ E_{(HSS)} &= L \times \frac{V_{VS} + |V_{OUT}|}{R^2} \times \left[ R \times I_{OUT(max)} - |V_{OUT}| \ln \left( \frac{R \times I_{OUT(max)} + |V_{OUT}|}{|V_{OUT}|} \right) \right] \end{split}$$

(7)

### Feature Description (continued)

When R approximately equals 0, E<sub>(HSD)</sub> can be given simply as:

$$\mathsf{E}_{(\mathsf{HSS})} = \frac{1}{2} \times \mathsf{L} \times \mathsf{I}_{\mathsf{OUT}(\mathsf{max})}^2 \frac{\mathsf{V}_{\mathsf{VS}} + \left|\mathsf{V}_{\mathsf{OUT}}\right|}{\left|\mathsf{V}_{\mathsf{OUT}}\right|} \tag{8}$$

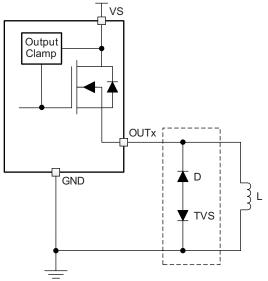

Note that for PWM-controlled inductive loads, it is recommended to add the external free-wheeling circuitry shown in Figure 29 to protect the device from repetitive power stressing. TVS is used to achieve the fast decay. See Figure 29 for more details.

Copyright © 2016, Texas Instruments Incorporated

Figure 29. Protection With External Circuitry

#### 8.3.5 Fault Detection and Reporting

#### 8.3.5.1 Diagnostic Enable Function

The DIAG\_EN pin enables or disables the diagnostic functions. If multiple devices are used, but the ADC resource is limited in the microcontroller, the MCU can use GPIOs to set DIAG\_EN high to enable the diagnostics of one device while disabling the diagnostics of the other devices by setting DIAG\_EN low. In addition, the device can keep the power consumption to a minimum by setting DIAG\_EN and INx low.

#### 8.3.5.2 Multiplexing of Current Sense

For version B, SEL is used to multiplex the shared current-sense function between the two channels. See Table 1 for more details.

| DIAG_EN | INx | SEH | SEL | CS ACTIVATED<br>CHANNEL | CS, FAULT, STx    | PROTECTIONS AND DIAGNOSTICS           |  |  |  |  |

|---------|-----|-----|-----|-------------------------|-------------------|---------------------------------------|--|--|--|--|

|         | Н   |     |     |                         | Llich impodonce   | Diagnostics disabled, full protection |  |  |  |  |

| L       | L   | _   | _   |                         | High impedance    | Diagnostics disabled, no protection   |  |  |  |  |

|         |     | 0   | 0   | Channel 1               | nel 2 See Table 2 |                                       |  |  |  |  |

| н       |     | 0   | 1   | Channel 2               |                   | See Table 2                           |  |  |  |  |

| п       |     | 1   | 0   | Channel 3               |                   | See Table 2                           |  |  |  |  |

|         |     | 1   | 1   | Channel 4               |                   |                                       |  |  |  |  |

Table 1. Diagnosis Configuration Table

### 8.3.5.3 Fault Table

Table 2 applies when the DIAG\_EN pin is enabled.

| CONDITIONS                                                       | INx          | OUTx | THER                       | CRITERION                          | STx<br>(VER. A)    | CS<br>(VER. B)      | FAULT<br>(VER. B) | FAULT RECOVERY                                                                                           |  |  |  |

|------------------------------------------------------------------|--------------|------|----------------------------|------------------------------------|--------------------|---------------------|-------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                  | L            | L    |                            | —                                  | Н                  | 0                   | Н                 | —                                                                                                        |  |  |  |

| Normal                                                           | Н            | Н    | _                          | _                                  | н                  | In linear<br>region | Н                 | _                                                                                                        |  |  |  |

| Overlaod, short to ground                                        | ground H L — |      | Current limit<br>triggered | L                                  | V <sub>CS(H)</sub> | L                   | Auto              |                                                                                                          |  |  |  |

| Open load <sup>(1)</sup> , short to battery,<br>reverse polarity | L            | н    | _                          | $V_{VS} - V_{OUTx} < V_{(ol,off)}$ | L                  | V <sub>CS(H)</sub>  | L                 | Auto                                                                                                     |  |  |  |

| Thermal shutdown                                                 | Н            |      | L                          | T <sub>SD</sub> triggered          | L                  | V <sub>CS(H)</sub>  | L                 | Output auto-retry. Fault<br>recovers when T <sub>J</sub> < T <sub>(SD,rst)</sub> or<br>when INx toggles. |  |  |  |

|                                                                  |              |      | н                          |                                    |                    | 00(1)               |                   | Output latch off. Fault recovers when INx toggles.                                                       |  |  |  |

| Thermal swing                                                    | Н            | _    | _                          | T <sub>SW</sub> triggered          | L                  | V <sub>CS(H)</sub>  | L                 | Auto                                                                                                     |  |  |  |

Table 2. Fault Table

(1) An external pullup is required for open-load detection.

### 8.3.5.4 STx and FAULT Reporting

For version A, two individual  $\overline{STx}$  pins report the fault conditions, each pin for its respective channel. When a fault condition occurs, it pulls  $\overline{STx}$  down to GND. A 3.3- or 5-V external pullup is required to match the supply level of the microcontroller. The digital status of each channel can be reported individually, or globally by connecting all the  $\overline{STx}$  pins together.

For version B, a global FAULT pin is used to monitor the global fault condition among all the channels. When a fault condition occurs on any channel, the FAULT pin is pulled down to GND. A 3.3-V or 5-V external pullup is required to match the supply level of the microcontroller.

After the FAULT report, the microcontroller can check and identify the channel in fault status by multiplexed current sensing. The CS pin also works as a fault report with an internal pullup voltage, V<sub>CS(H)</sub>.

### 8.3.6 Full Diagnostics

### 8.3.6.1 Short-to-GND and Overload Detection

When a channel is on, a short to GND or overload condition causes overcurrent. If the overcurrent triggers either the internal or external current-limit threshold, the fault condition is reported out. The microcontroller can handle the overcurrent by turning off the switch. The device heats up if no actions are taken. If a thermal shutdown occurs, the current limit is  $I_{CL(TSD)}$  to keep the power stressing on the power FET to a minimum. The device automatically recovers when the fault condition is removed.

### 8.3.6.2 Open-Load Detection

### 8.3.6.2.1 Channel On

When a channel on, benefiting from the high-accuracy current sense in a small current range, if an open-load event occurs, it can be detected as an ultralow  $V_{CS}$  and handled by the microcontroller. Note that the detection is not reported on the STx or FAULT pins. The microcontroller must set the SEL pin to detect the channel-on open-load fault proactively.

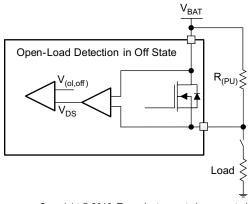

### 8.3.6.2.2 Channel Off

When a channel is off, if a load is connected, the output is pulled down to GND. But if an open load occurs, the output voltage is close to the supply voltage ( $V_{VS} - V_{OUTx} < V_{(ol,off)}$ ), and the fault is reported out.

There is always a leakage current  $I_{(ol,off)}$  present on the output due to internal logic control path or external humidity, corrosion, and so forth. Thus, TI recommends an external pullup resistor to offset the leakage current when an open load is detected. The recommended pullup resistance is 20 k $\Omega$ .

Copyright © 2016, Texas Instruments Incorporated

Figure 30. Open-Load Detection in Off-State

#### 8.3.6.3 Short-to-Battery Detection

Short-to-battery has the same detection mechanism and behavior as open-load detection, in both the on-state and off-state. See Table 2 for more details.

In the on-state, reverse current flows through the FET instead of the body diode, leading to less power dissipation. Thus, the worst case occurs in the off-state.

- If  $V_{OUTx} V_{VS} < V_{(F)}$  (body diode forward voltage), no reverse current occurs.

- If V<sub>OUTx</sub> V<sub>VS</sub> > V<sub>(F)</sub>, reverse current occurs. The current must be limited to less than I<sub>R(1)</sub>. Setting an INx pin high can minimize the power stress on its channel. Also, for external reverse protection, see *Reverse-Current Protection* for more details.

#### 8.3.6.4 Reverse Polarity Detection

Reverse polarity detection has the same detection mechanism and behavior as open-load detection both in the on-state and off-state. See Table 2 for more details.

In the on-state, the reverse current flows through the FET instead of the body diode, leading to less power dissipation. Thus, the worst case occurs in the off-state. The reverse current must be limited to less than  $I_{R(2)}$ . Set the related INx pin high to keep the power dissipation to a minimum. For external reverse-blocking circuitry, see *Reverse-Current Protection* for more details.

#### 8.3.6.5 Thermal Fault Detection

To protect the device in severe power stressing cases, the device implements two types of thermal fault detection, absolute temperature protection (thermal shutdown) and dynamic temperature protection (thermal swing). Respective temperature sensors are integrated close to each power FET, so the thermal fault is reported by each channel. This arrangement can help the device keep the cross-channel effect to a minimum when some channels are in a thermal fault condition.

#### 8.3.6.5.1 Thermal Shutdown

Thermal shutdown is active when the absolute temperature  $T_J > T_{(SD)}$ . When thermal shutdown occurs, the respective output turns off. The THER pin is used to configure the behavior after the thermal shutdown occurs.

- When the THER pin is low, thermal shutdown operates in the auto-retry mode. The output automatically recovers when  $T_J < T_{(SD)} T_{(hys)}$ , but the current is limited to  $I_{CL(TSD)}$  to avoid repetitive thermal shutdown. The thermal shutdown fault signal is cleared when  $T_J < T_{(SD,rst)}$  or after toggling the related INx pin.

- When the THER pin is high, thermal shutdown operates in the latch mode. The output latches off when thermal shutdown occurs. When the THER pin goes from high to low, thermal shutdown changes to auto-retry mode. The thermal shutdown fault signal is cleared after toggling the related INx pin.

Thermal swing activates when the power FET temperature is increasing sharply, that is, when  $\Delta T = T_{(FET)} - T_{(Logic)} > T_{(sw)}$ , then the output turns off. The output automatically recovers and the fault signal clears when  $\Delta T = T_{(FET)} - T_{(Logic)} < T_{(sw)} - T_{(hys)}$ . Thermal swing function improves the device reliability when subjected to repetitive fast thermal variation. As shown in Figure 31, multiple thermal swings are triggered before thermal shutdown occurs.

Figure 31. Thermal Behavior Diagram

### 8.3.7 Full Protections

### 8.3.7.1 UVLO Protection

The device monitors the supply voltage  $V_{VS}$ , to prevent unpredicted behaviors when  $V_{VS}$  is too low. When  $V_{VS}$  falls down to  $V_{VS(uvf)}$ , the device shuts down. When  $V_{VS}$  rises up to  $V_{VS(uvr)}$ , the device turns on.

### 8.3.7.2 Loss-of-GND Protection

When loss of GND occurs, output is shut down regardless of whether the INx pin is high or low. The device can protect against two ground-loss conditions, loss of device GND and loss of module GND.

### 8.3.7.3 Protection for Loss of Power Supply

When loss of supply occurs, the output is shut down regardless of whether the INx pin is high or low. For a resistive or a capacitive load, loss of supply has no risk. But for a charged inductive load, the current is driven from all the I/O pins to maintain the inductance current. To protect the system in this condition, TI recommends the external free-wheeling diode as shown in *Figure 32*.

Copyright © 2016, Texas Instruments Incorporated

Figure 32. Protection for Loss of Power Supply

### 8.3.7.4 Reverse-Current Protection

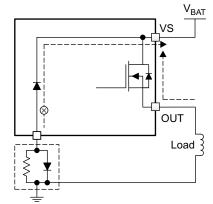

Reverse current occurs in two conditions: short to battery and reverse polarity.

- When a short to the battery occurs, there is only reverse current through the body diode. I<sub>R(1)</sub> specifies the limit of the reverse current.

- In a reverse-polarity condition, there are reverse currents through the body diode and the device GND pin. I<sub>R(2)</sub> specifies the limit of the reverse current. The GND pin maximum current is specified in the *Absolute Maximum Ratings*.

To protect the device, TI recommends two types of external circuitry.

• Adding a blocking diode. Both the IC and load are protected when in reverse polarity.

Copyright © 2016, Texas Instruments Incorporated

### Figure 33. Reverse-Current External Protection, Method 1

Adding a GND network. The reverse current through the device GND is blocked. The reverse current through the FET is limited by the load itself. TI recommends a resistor in parallel with the diode as a GND network. The recommended selection are 1-kΩ resistor in parallel with an >100-mA diode. If multiple high-side switches are used, the resistor and diode can be shared among devices. The reverse current protection diode in the GND network forward voltage should be less than 0.6 V in any circumstances. In addition a minimum resistance of 4.7 K is recommended on the I/O pins.

Copyright © 2016, Texas Instruments Incorporated

#### Figure 34. Reverse-Current External Protection, Method 2

### 8.3.7.5 MCU I/O Protection

In some severe conditions, such as the ISO7637-2 test or the loss of battery with inductive loads, a negative pulse occurs on the GND pin This pulse can cause damage on the connected microcontroller. TI recommends serial resistors to protect the microcontroller, for example, 4.7-k $\Omega$  when using a 3.3-V microcontroller and 10-k $\Omega$  for a 5-V microcontroller.

Copyright © 2016, Texas Instruments Incorporated

Figure 35. MCU I/O External Protection

### 8.4 Device Functional Modes

#### 8.4.1 Working Modes

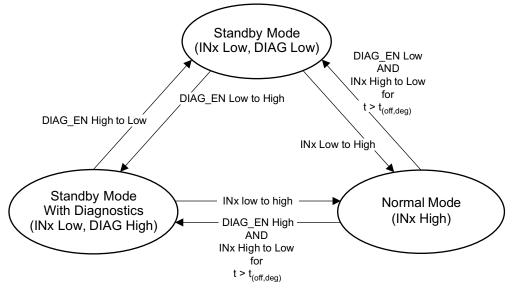

The device has three working modes, the normal mode, the standby mode, and the standby mode with diagnostics.

Note that IN must be low for t >  $t_{(off,deg)}$  to enter the standby mode, where  $t_{(off,deg)}$  is the standby mode deglitch time used to avoid false triggering. Figure 36 shows a working-mode diagram.

## **Device Functional Modes (continued)**

Figure 36. Working Modes

### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The TPS4H000-Q1 device is capable of driving a wide variety of resistive, inductive, and capacitive loads, including LEDs, relays, and sub-modules. Full diagnostics and high-accuracy current-sense features enable intelligent control of the load. An external adjustable current limit improves the reliability of the whole system by clamping the inrush or overload current.

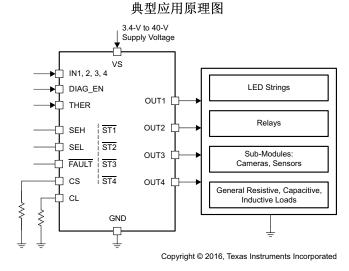

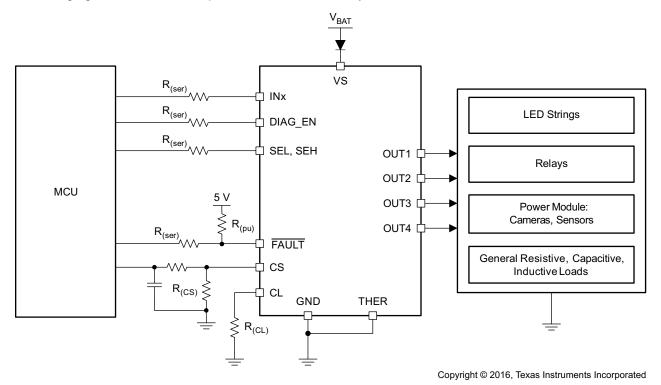

### 9.2 Typical Application

The following figure shows an example of the external circuitry connections based on the version-B device.

Figure 37. Typical Application Diagram

### 9.2.1 Design Requirements

- V<sub>VS</sub> range from 9 V to 16 V

- Load range is from 0.1 A to 0.25 A for each channel

- Current sense for fault monitoring

- Expected current-limit value of 0.5 A

- · Automatic recovery mode when thermal shutdown occurs

- Full diagnostics with 5-V MCU

- · Reverse-voltage protection with a blocking diode in the power-supply line

### **Typical Application (continued)**

### 9.2.2 Detailed Design Procedure

To keep the 0.25-A nominal current in the 0 to 4-V current-sense range, calculate the  $R_{(CS)}$  resistor using Equation 9. To achieve better current-sense accuracy, a 1% tolerance or better resistor is preferred.

$$\mathsf{R}_{(CS)} = \frac{\mathsf{V}_{CS}}{\mathsf{I}_{CS}} = \frac{\mathsf{V}_{CS} \times \mathsf{K}_{(CS)}}{\mathsf{I}_{OUT}} = \frac{4 \times 80}{0.25} = 1280 \ \Omega \tag{9}$$

To set the adjustable current limit value at 2.5-A, calculate  $R_{(CL)}$  using Equation 10.

$$\mathsf{R}_{(\mathsf{CL})} = \frac{\mathsf{V}_{\mathsf{CL}(\mathsf{th})} \times \mathsf{K}_{(\mathsf{CL})}}{\mathsf{I}_{\mathsf{OUT}}} = \frac{0.8 \times 300}{0.5} = 480 \ \Omega \tag{10}$$

TI recommends  $R_{(ser)} = 10 \text{ k}\Omega$  for 5-V MCU, and  $R_{(pu)} = 10 \text{ k}\Omega$  as the pullup resistor.

### 9.2.3 Application Curves

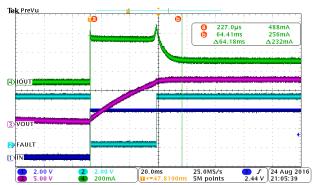

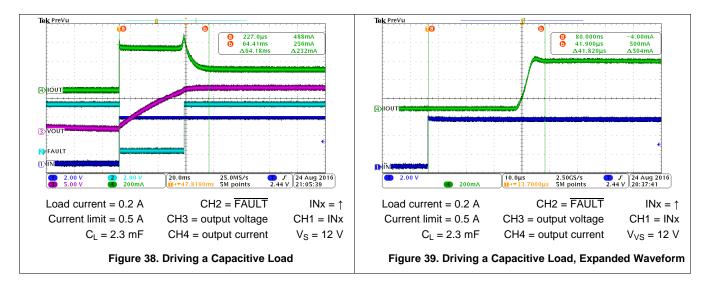

Figure 38 shows a test example of soft-start when driving a big capacitive load. Figure 39 shows an expanded waveform of the output current.

TPS4H000-Q1 ZHCSET1B-DECEMBER 2015-REVISED MARCH 2018

www.ti.com.cn

### **Typical Application (continued)**

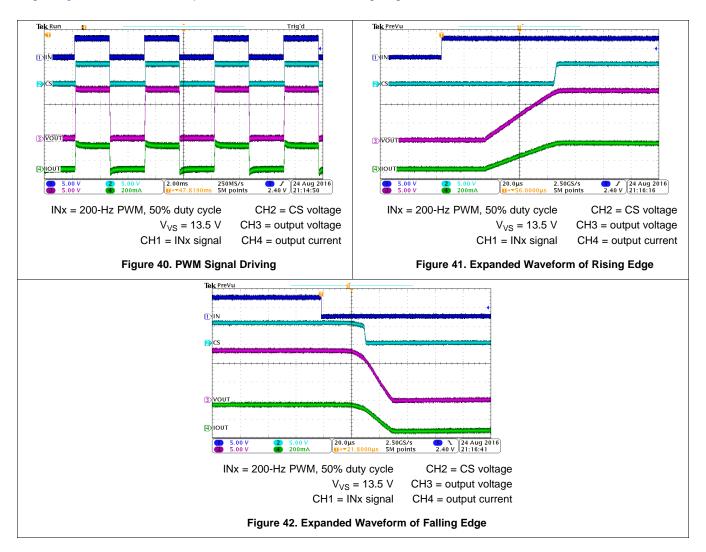

Figure 40 shows a test example of PWM-mode driving. Figure 41 shows the expanded waveform of the rising edge. Figure 42 shows the expanded waveform of the falling edge.

### **10** Power Supply Recommendations

The device is qualified for both automotive and industrial applications. The normal power supply connection is a 12-V automotive system or 24-V industrial system. Detailed supply voltage should be within the range specified in the *Recommended Operating Conditions*.

### 11 Layout

### 11.1 Layout Guidelines

To prevent thermal shutdown,  $T_J$  must be less than 150°C. The HTSSOP package has good thermal impedance. However, the PCB layout is very important. Good PCB design can optimize heat transfer, which is absolutely essential for the long-term reliability of the device.

- Maximize the copper coverage on the PCB to increase the thermal conductivity of the board. The major heat flow path from the package to the ambient is through the copper on the PCB. Maximum copper is extremely important when there are not any heat sinks attached to the PCB on the other side of the package.

- Add as many thermal vias as possible directly under the package ground pad to optimize the thermal conductivity of the board.

- All thermal vias should either be plated shut or plugged and capped on both sides of the board to prevent solder voids. To ensure reliability and performance, the solder coverage should be at least 85%.

### 11.2 Layout Examples

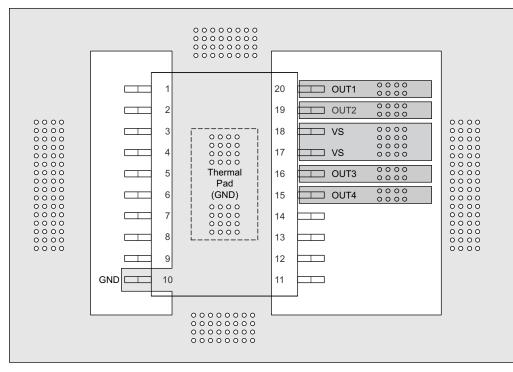

### 11.2.1 Without a GND Network

Without a GND network, tie the thermal pad directly to the board GND copper for better thermal performance.

Figure 43. Layout Example Without a GND Network

ZHCSET1B-DECEMBER 2015-REVISED MARCH 2018

www.ti.com.cn

### Layout Examples (continued)

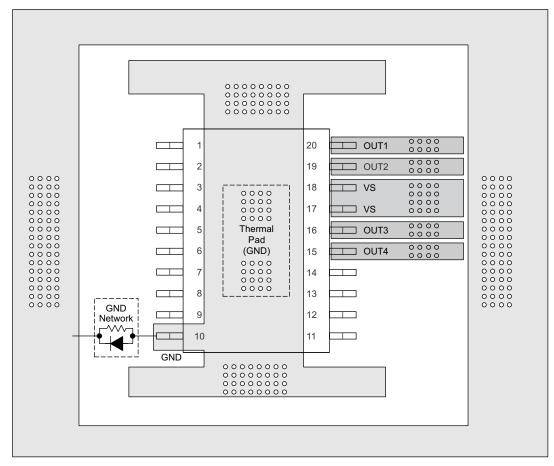

### 11.2.2 With a GND Network

With a GND network, tie the thermal pad as one trace to the board GND copper.

Figure 44. Layout Example With a GND Network

### 12 器件和文档支持

### 12.1 接收文档更新通知

要接收文档更新通知,请导航至 TI.com.cn 上的器件产品文件夹。请单击右上角的提醒我进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

### 12.2 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范, 并且不一定反映 TI 的观点;请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 **71 参考设计支持** 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 12.3 商标

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 12.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知和修 订此文档。如需获取此数据表的浏览器版本,请查看左侧的导航面板。

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TPS4H000AQPWPRQ1 | ACTIVE        | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green    | NIPDAU                               | Level-3-260C-168 HR  | -40 to 125   | 4H000AQ                 | Samples |

| TPS4H000BQPWPRQ1 | ACTIVE        | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green    | NIPDAU                               | Level-3-260C-168 HR  | -40 to 125   | 4H000BQ                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

10-Dec-2020

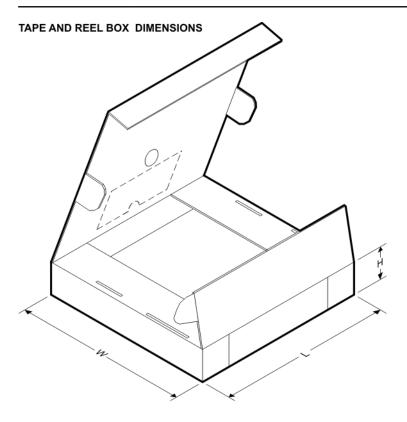

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

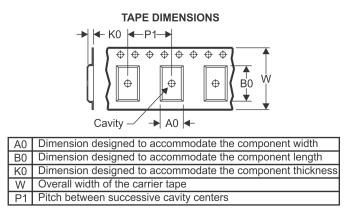

### TAPE AND REEL INFORMATION

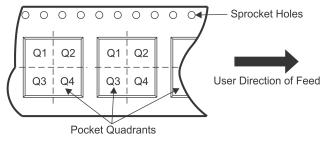

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS4H000AQPWPRQ1            | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS4H000BQPWPRQ1            | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

26-Feb-2019

\*All dimensions are nominal