# TAS2764 Digital Input Mono Class-D Audio Amplifier With Speaker IV Sense

#### 1 Features

- Key Features

- Y-Bridge Power Architecture

- Edge and Spread Spectrum Control

- Full Scale Ultrasonic Output to 40 kHz

- Output Power (1 % THD+N)

- 13 W (4 Ω, 12 V)

- 8 W (8 Ω, 12 V)

- Power Consumption (1 % THD+N, 4 Ω, 12 V)

- 81% Efficient at 1W

- 85% Efficient at 13W

- 3mA in Noise Gate Mode

- <1uA in Hardware Shutdown Mode</li>

- Power Supplies and Management

- PVDD: 2.3 V to 16 V

- VBAT1S: 2.3 V to 5.5 V

- AVDD: 1.8 V

- IOVDD: 1.2 V/ 1.8 V

- Brownout Protection

- PVDD Tracking Peak Voltage Limiter

- Interfaces and Control

- SDOUT and I<sup>2</sup>S Feedback for Echo Cancellation

- I<sup>2</sup>S/TDM: 8 Channels of 32-bit up to 96 kHz

- I<sup>2</sup>C: 8 addresses with Fast Mode Plus Support

- 44.1 kHz to 96 kHz Sample Rates

- Inter Chip Communication Bus

- Integrated Speaker Management and Protection

- Speaker Voltage and Current Sense

- Short and Open Detection

- Thermal and Over Current Protection

- Over Power Protection

### 2 Applications

- Laptop Computers

- Tablets

- Bluetooth Speakers

- Soundbars

- Consumer Audio Devices

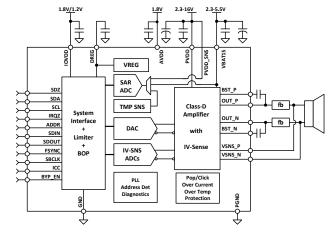

## 3 Description

The TAS2764 is a mono digital input Class-D audio amplifier optimized for efficiently driving high peak power into small loudspeakers. The Class-D amplifier is capable of delivering 13 W of continuous power into a 4  $\Omega$  load with less than 1 % THD+N at a supply voltage of 12 V.

Y-Brige architecture improves overall efficiency at low level of output power and in idle mode.

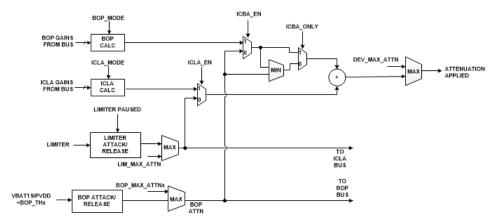

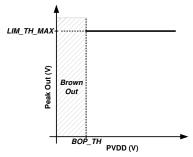

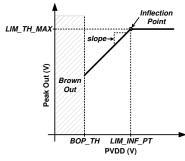

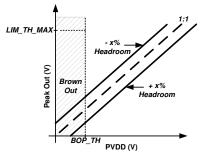

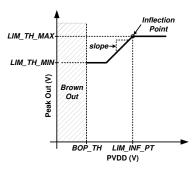

Integrated speaker voltage and current sense provides for real time monitoring of loudspeaker behavior. A supply tracking peak voltage limiter optimizes amplifier headroom. Brownout prevention scheme with multiple thresholds allows reducing the gain in signal path when the supply drops.

Up to eight TAS2764 devices can share a common bus via I<sup>2</sup>S/TDM and I<sup>2</sup>C interfaces.

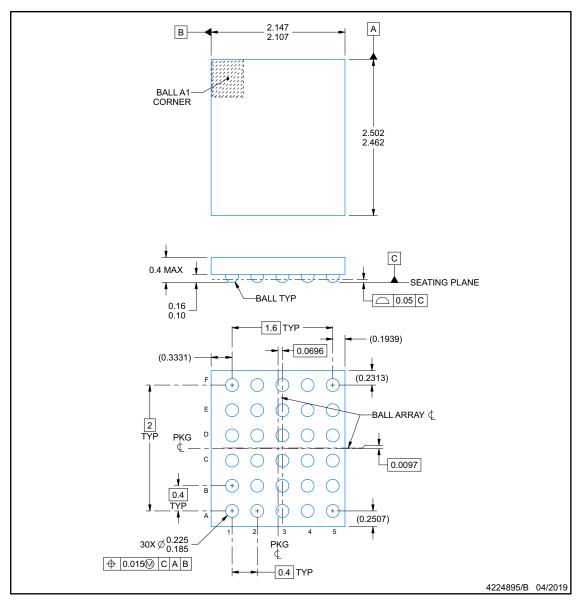

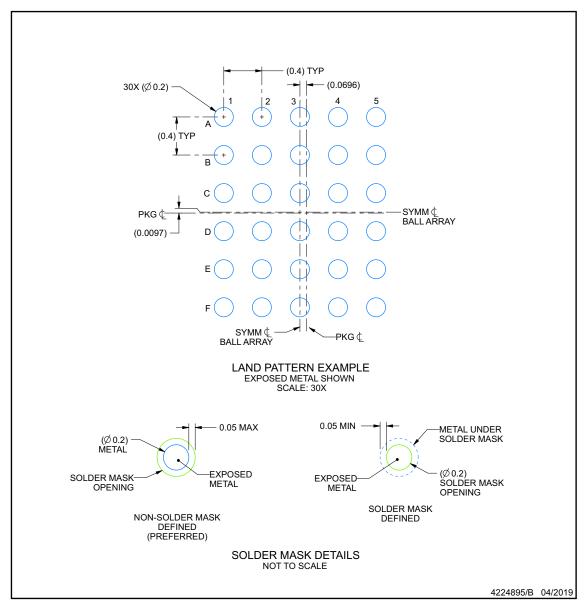

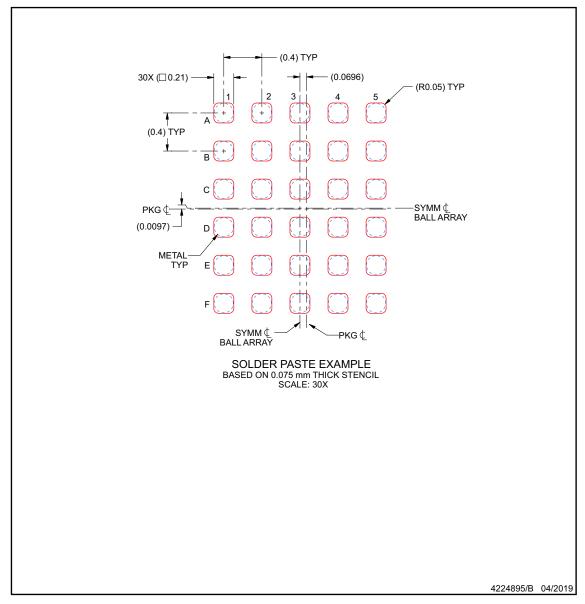

The device is available in a 30-ball, 0.4 mm pitch CSP for a compact PCB footprint.

### **Device Information** (1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| TAS2764     | DSBGA   | 2.15 mm x 2.56 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

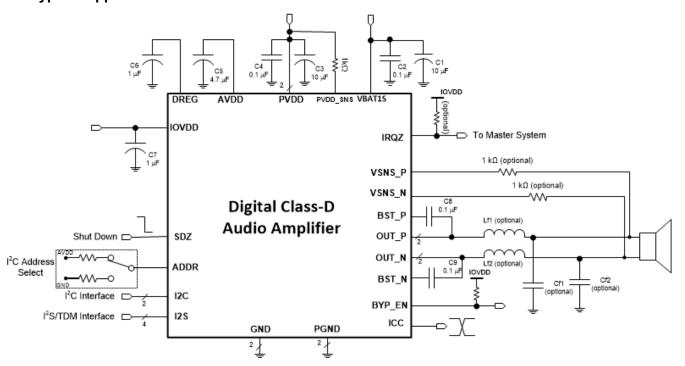

**Schematic**

# **Table of Contents**

| 1 Features                               | 1              | 9.5 Application Curves                              | 90  |

|------------------------------------------|----------------|-----------------------------------------------------|-----|

| 2 Applications                           | 1              | 10 Initialization Set Up                            | 91  |

| 3 Description                            | 1              | 10.1 Initial Device Configuration - 4 Channel Power |     |

| 4 Revision History                       | <mark>2</mark> | Up (Default Mode - PWR_MODE1)                       | 91  |

| 5 Pin Configuration and Functions        | 3              | 10.2 Initial Device Configuration - 44.1 kHz        | 91  |

| 6 Specifications                         |                | 10.3 Sample Rate Change - 48 kHz to 44.1kHz         |     |

| 6.1 Absolute Maximum Ratings             | <u>5</u>       | 10.4 Sample Rate Change - 44.1 kHz to 48 kHz        | 92  |

| 6.2 ESD Ratings                          |                | 10.5 Device Mute                                    |     |

| 6.3 Recommended Operating Conditions     | <mark>5</mark> | 10.6 Device Un-Mute                                 | 92  |

| 6.4 Thermal Information                  | 6              | 10.7 Device Sleep                                   | 92  |

| 6.5 Electrical Characteristics           | 6              | 10.8 Device Wake                                    | 92  |

| 6.6 I <sup>2</sup> C Timing Requirements | 11             | 11 I <sup>2</sup> C Byte Transfers                  | 94  |

| 6.7 TDM Port Timing Requirements         | 11             | 11.1 Single-Byte and Multiple-Byte Transfers        |     |

| 6.8                                      |                | 11.2 Single-Byte Write                              |     |

| 6.9 Typical Characteristics              | 13             | 11.3 Multiple-Byte Write and Incremental Multiple-  |     |

| 7 Parameter Measurement Information      |                | Byte Write                                          | 94  |

| 8 Detailed Description                   | 16             | 11.4 Single-Byte Read                               | 94  |

| 8.1 Overview                             | 16             | 11.5 Multiple-Byte Read                             |     |

| 8.2 Functional Block Diagram             | 16             | 12 Power Supply Recommendations                     |     |

| 8.3 Feature Description                  | 16             | 12.1 Power Supply Modes                             |     |

| 8.4 Device Functional Modes              | 18             | 13 Layout                                           | 98  |

| 8.5 Operational Modes                    | 29             | 13.1 Layout Guidelines                              |     |

| 8.6 Faults and Status                    | 29             | 13.2 Layout Example                                 | 98  |

| 8.7 Power Sequencing Requirements        | 32             | 14 Device and Documentation Support                 |     |

| 8.8 Digital Input Pull Downs             |                | 14.1 Receiving Notification of Documentation Update |     |

| 8.9 Register Map                         | 32             | 14.2 Support Resources                              | 100 |

| 9 Application and Implementation         | 89             | 14.3 Trademarks                                     | 100 |

| 9.1 Application Information              |                | 14.4 Electrostatic Discharge Caution                | 100 |

| 9.2 Typical Application                  |                | 14.5 Glossary                                       |     |

| 9.3 Design Requirements                  | 90             | 15 Mechanical, Packaging, and Orderable             |     |

| 9.4 Detailed Design Procedure            |                | Information                                         | 101 |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2020 | *        | Initial Release |

Submit Document Feedback

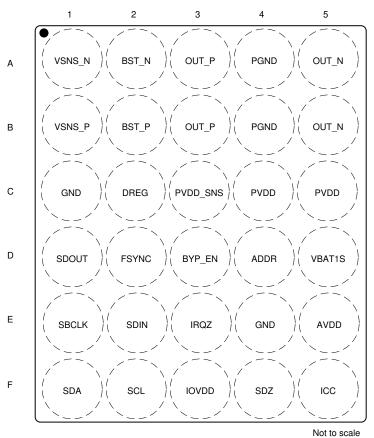

# **5 Pin Configuration and Functions**

Figure 5-1. YBH Package 30-Ball DSBGA Top View

Table 5-1. Pin Functions

| Р                          | IN  |                 | PEGGPIPTION                                                                                                                                                                                              |  |  |

|----------------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                       | NO. | I/O             | DESCRIPTION                                                                                                                                                                                              |  |  |

| ADDR                       | D4  | I               | Address detect pin. Resistor value at this pin selects the I <sup>2</sup> C address. See Device Address Selection section. Minimize capacitive loading on this pin and do not connect to any other load. |  |  |

| AVDD                       | E5  | Р               | Analog power input. Connect to 1.8V supply and decouple to GND with cap.                                                                                                                                 |  |  |

| BST_N                      | A2  | Р               | Class-D negative bootstrap. Connect a capacitor between BST_N and OUT_N.                                                                                                                                 |  |  |

| BST_P                      | B2  | Р               | Class-D positive bootstrap. Connect a capacitor between BST_P and OUT_P.                                                                                                                                 |  |  |

| DREG                       | C2  | Р               | Digital core voltage regulator output. Bypass to GND with a capacitor. Do not connect to external load.                                                                                                  |  |  |

| FSYNC D2 I TDM Frame Sync. |     | TDM Frame Sync. |                                                                                                                                                                                                          |  |  |

| CNID                       | E4  | _               | Analog ground Composite DCD ground plans                                                                                                                                                                 |  |  |

| GND                        | C1  | Р               | Analog ground. Connect to PCB ground plane.                                                                                                                                                              |  |  |

| ICC                        | F5  | Ю               | Interchip communication pin used to transmit gain alignment.                                                                                                                                             |  |  |

| IOVDD                      | F3  | Р               | Digital IO Supply. Connect to 1.2V or 1.8 V IO supply and decouple with a capacitor to GND.                                                                                                              |  |  |

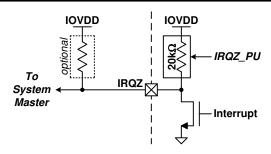

| IRQZ                       | E3  | 0               | Open drain, active low interrupt pin. Pull up to IOVDD with resistor if optional internal pull up is not used.                                                                                           |  |  |

| BYP_EN                     | D3  | 0               | Low voltage signaling pin with open drain output.                                                                                                                                                        |  |  |

| OUT N                      | B5  | 0               | Class Dissertive systems                                                                                                                                                                                 |  |  |

| OUT_N                      | A5  | 0               | Class-D negative output.                                                                                                                                                                                 |  |  |

## Table 5-1. Pin Functions (continued)

| PIN      | PIN |     | DESCRIPTION                                                                                 |  |  |

|----------|-----|-----|---------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                                                 |  |  |

| OUT D    | В3  | 0   | Class D positive output                                                                     |  |  |

| OUT_P    | A3  |     | Class-D positive output.                                                                    |  |  |

| PGND -   | B4  | Р   | Class D ground Connect to DCD ground plans                                                  |  |  |

| PGND     | A4  | 7 P | Class-D ground. Connect to PCB ground plane.                                                |  |  |

| SBCLK    | E1  | I   | TDM Serial Bit Clock.                                                                       |  |  |

| SCL      | F2  | I   | I <sup>2</sup> C Clock Pin. Pull up to IOVDD with a resistor.                               |  |  |

| SDA      | F1  | Ю   | O I <sup>2</sup> C Data Pin. Pull up to IOVDD with a resistor.                              |  |  |

| SDIN     | E2  | I   | TDM Serial Data Input.                                                                      |  |  |

| SDOUT    | D1  | Ю   | TDM Serial Data Output.                                                                     |  |  |

| SDZ      | F4  | I   | Active low hardware shutdown.                                                               |  |  |

| DVDD     | C4  | P   | Class D newer cumply input Descuple with a conscitor                                        |  |  |

| PVDD     | C5  | , P | Class-D power supply input. Decouple with a capacitor.                                      |  |  |

| PVDD_SNS | C3  | I   | PVDD remote sense pin.                                                                      |  |  |

| VBAT1S   | D5  | Р   | Single-cell battery supply input. Decouple with a capacitor.                                |  |  |

| VSNS_N   | A1  | I   | Voltage Sense negative input. Connect to Class-D negative output after ferrite bead filter. |  |  |

| VSNS P   | B1  | ı   | Voltage Sense positive input. Connect to Class-D positive output after ferrite bead filter. |  |  |

Submit Document Feedback

# **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                                                         |                                                                     |                                       | MIN  | MAX   | UNIT |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------|------|-------|------|

| Supply Voltage Internal Supply Voltage Input voltage <sup>(2)</sup> Operating free-air te degraded. Performance free-ai | AVDD                                                                |                                       | -0.3 | 2     | V    |

| degraded.                                                                                                               | IOVDD                                                               |                                       | -0.3 | 2     | V    |

|                                                                                                                         | PVDD                                                                | Continuous                            | -0.3 | 18.5  | V    |

|                                                                                                                         | PVDD                                                                | Transient for 1s life time            |      | 19.75 | V    |

|                                                                                                                         | VBAT1S                                                              |                                       | -0.3 | 6     | V    |

| nternal Supply                                                                                                          | PVDD-VBAT1S Supply                                                  | Continuous                            | -0.3 | 16.5  | V    |

|                                                                                                                         |                                                                     | Transient for 1s life time            |      | 18    |      |

|                                                                                                                         | DREG                                                                |                                       | -0.3 | 1.5   | V    |

| Input voltage(2)                                                                                                        | Digital IOs referenced to IOVDD supply                              |                                       | -0.3 | 2.3   | V    |

|                                                                                                                         | temperature, T <sub>A</sub> ; Device is functional and reliable, so | me performance characteristics may be | -40  | 85    | °C   |

| Performance free-                                                                                                       | air temperature, T <sub>P</sub> ; All performance characteristics a | are met.                              | -20  | 70    | °C   |

| Operating junction                                                                                                      | temperature, T <sub>J</sub>                                         |                                       | -40  | 150   | °C   |

| Storage temperatu                                                                                                       | ure, T <sub>stg</sub>                                               |                                       | -65  | 150   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Section 6.1 can cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Section 6.3. Exposure to absolute maximum rated conditions for extended periods can affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                                            | MIN                | NOM   | MAX                                                    | UNIT |

|------------------|--------------------------------------------|--------------------|-------|--------------------------------------------------------|------|

| AVDD             | Supply voltage                             | 1.65               | 1.8   | 1.95                                                   | V    |

| IOVDD            | Supply voltage                             | 1.1                | 1.2   | 1.3                                                    | V    |

| IOVDD            | Supply voltage                             | 1.65               | 1.8   | 1.95                                                   | V    |

| PVDD             | Supply voltage (functional) <sup>(1)</sup> | 2.3 <sup>(2)</sup> |       | 16                                                     | V    |

|                  | Supply voltage (performance)               | 3.0                |       | 16                                                     | V    |

| VBAT1S           | Supply voltage (functional) <sup>(1)</sup> | 2.3                |       | 5.5                                                    | V    |

| VBALIS           | Supply voltage (performance)               | 3.0                |       | 1.8 1.95<br>1.2 1.3<br>1.8 1.95<br>16 16<br>5.5<br>5.5 | V    |

| V <sub>IH</sub>  | High-level digital input voltage           |                    | IOVDD |                                                        | V    |

| V <sub>IL</sub>  | Low-level digital input voltage            |                    | 0     |                                                        | V    |

| R <sub>SPK</sub> | Speaker impedance                          | 3.2                |       |                                                        | Ω    |

| L <sub>SPK</sub> | Speaker inductance                         | 5                  |       |                                                        | μΗ   |

<sup>(1)</sup> Device will remain functional but performance will degrade.

(2) PVDD>VBAT1S-0.7V.

<sup>(2)</sup> All digital inputs and IOs are failsafe.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.4 Thermal Information**

|                        |                                              | TAS2764     |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | YBH (DSBGA) | UNIT |

|                        |                                              | 30 PINS     |      |

| R <sub>0JA</sub>       | Junction-to-ambient thermal resistance       | 59.9        | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 0.2         | °C/W |

| R <sub>0JB</sub>       | Junction-to-board thermal resistance         | 14.9        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.1         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 14.9        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

$T_A$  = 25 °C, PVDD = 12 V, VBAT1S = 3.8 V, AVDD = 1.8V IOVDD =1.2 V,  $R_L$  = 4 $\Omega$  + 16 $\mu$ H,  $f_{in}$  = 1 kHz,  $f_s$  = 48 kHz, Gain = 21 dBV, SDZ = 1, EDGE\_RATE[1:0]=00, NG\_EN=0, EN\_LLSR=1, PWR\_MODE1, Measured filter free as in Section 7 (unless otherwise noted).

|                       | PARAMETER                                                   | TEST CONDITIONS                                                      | MIN        | TYP  | MAX            | UNIT |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------------|------------|------|----------------|------|

| DIGITAL I             | NPUT and OUTPUT                                             |                                                                      |            |      |                |      |

| V <sub>IH</sub>       | High-level digital input logic voltage threshold            | All digital pins except SDA and SCL                                  | 0.7×IOVDD  |      |                | V    |

| V <sub>IL</sub>       | Low-level digital input logic voltage threshold             | All digital pins except SDA and SCL                                  |            |      | 0.3 ×<br>IOVDD | ٧    |

| V <sub>IH(I2C)</sub>  | High-level digital input logic voltage threshold            | SDA and SCL                                                          | 0.7xIOVDD  |      |                | V    |

| V <sub>IL(I2C)</sub>  | Low-level digital input logic voltage threshold             | SDA and SCL                                                          |            |      | 0.3 x<br>IOVDD | V    |

| V <sub>OH</sub>       | High-level digital output voltage                           | All digital pins except SDA, SCL and IRQZ; I <sub>OH</sub> = 100 μA. | IOVDD-0.2V |      |                | V    |

| V <sub>OL</sub>       | Low-level digital output voltage                            | All digital pins except SDA, SCL and IRQZ; $I_{OL}$ = -100 $\mu$ A.  |            |      | 0.2            | V    |

| V <sub>OL(I2C)</sub>  | Low-level digital output voltage                            | SDA and SCL; I <sub>OL(I2C)</sub> = -1 mA.                           | -          | -    | 0.2 x<br>IOVDD | ٧    |

| V <sub>OL(IRQZ)</sub> | Low-level digital output voltage for IRQZ open drain Output | IRQZ; I <sub>OL(IRQZ)</sub> = -1 mA.                                 |            |      | 0.2            | V    |

| ІН                    | Input logic-high leakage for digital inputs                 | All digital pins; Input = IOVDD.                                     | -1         |      | 1              | μA   |

| lıL                   | Input logic-low leakage for digital inputs                  | All digital pins; Input = GND.                                       | -1         |      | 1              | μA   |

| Ros                   | OUT to VSNS Resistors                                       | Load disconnected                                                    |            | 10   | ,              | kΩ   |

| C <sub>IN</sub>       | Input capacitance for digital inputs                        | All digital pins                                                     |            | 5    |                | pF   |

| R <sub>PD</sub>       | Pull down resistance for IO pins when asserted on           | SDOUT, SDIN, FSYNC, SBCLK                                            |            | 18   |                | kΩ   |

|                       |                                                             | Drive Mode 0 - Measured at (IOVDD-0.4V) and 0.4V                     |            | 8    |                |      |

| 0                     | Output Ourrent Strongth                                     | Drive Mode 1 - Measured at (IOVDD-0.4V) and 0.4V                     |            | 6    |                | A    |

| U                     | Output Current Strength                                     | Drive Mode 2 - Measured at (IOVDD-0.4V) and 0.4V                     |            | 4    |                | mA   |

|                       |                                                             | Drive Mode 3 - Measured at (IOVDD-0.4V) and 0.4V                     |            | 2    |                |      |

| AMPLIFIE              | R PERFORMANCE                                               |                                                                      |            |      |                |      |

|                       |                                                             | THD+N = 1 %                                                          |            | 13   |                |      |

| D                     | Maximum Continuous Output Power                             | R <sub>L</sub> = 8 Ω + 16 μH, THD+N = 1 %                            |            | 8    |                | w    |

| P <sub>OUT</sub>      | Maximum Continuous Output Fower                             | THD+N = 10 %                                                         |            | 15.8 |                | V V  |

|                       |                                                             | $R_L = 8 \Omega + 16 \mu H$ , THD+N = 10 %                           |            | 9.7  |                |      |

|                  | PARAMETER                               | TEST CONDITIONS                                                             | MIN TYP   | MAX   | UNIT |

|------------------|-----------------------------------------|-----------------------------------------------------------------------------|-----------|-------|------|

|                  |                                         | P <sub>OUT</sub> = 1 W                                                      | 81        |       |      |

|                  |                                         | R <sub>L</sub> = 8 Ω + 16 μH, P <sub>OUT</sub> = 1 W                        | 84        |       |      |

|                  |                                         | $R_L = 8 \Omega + 5 \mu H, P_{OUT} = 1 W PWR_MODE2$                         | 76.5      |       |      |

|                  | System Efficiency                       | $R_L = 8 \Omega + 16\mu H, P_{OUT} = 1 W PWR_MODE2$                         | 82.5      |       | %    |

|                  |                                         | P <sub>OUT</sub> = 10 W                                                     | 85        |       |      |

|                  |                                         | R <sub>L</sub> = 8 Ω + 16 μH, P <sub>OUT</sub> = 5 W                        | 90        |       |      |

|                  |                                         | R <sub>L</sub> = 8 Ω + 5 μH, P <sub>OUT</sub> = 8 W, PWR_MODE2              | 90        |       |      |

|                  |                                         | P <sub>OUT</sub> = 1 W, f <sub>in</sub> = 1 kHz                             | -83       |       |      |

| THD+N            | Total Harmonic Distortion and Noise     | P <sub>OUT</sub> = 1 W, f <sub>in</sub> = 6.67 kHz                          | -83       |       | dB   |

|                  | Total Harmonio Bioteritori una Noto     | POUT = 1 W, RL = 8 $\Omega$ + 5 $\mu$ H, fin = 20 Hz - 20 kHz,<br>PWR_MODE2 | -83       |       | QD.  |

| IMD              | Intermodulation Distortion              | ITU-R, 19kHz/20kHz, 1:1, $P_{OUT}$ = 6.5W, $R_L$ = 8 Ω + 16μH               | -90       |       | dB   |

|                  |                                         | A-Weighted, 20 Hz - 20 kHz, DAC in Mute, PWR_MODE1                          | 27        |       |      |

| V <sub>N</sub>   | Idle Channel Noise                      | A-Weghted, 20 Hz - 20k Hz, DAC in Mute, PWR_MODE2                           | 27        |       | μV   |

|                  |                                         | A-Weighted, 20 Hz - 20 kHz, DAC in Mute, PWR_MODE4                          | 32.7      |       | •    |

|                  |                                         | Average frequency in Spread Spectrum Mode, CLASSD_SYNC=0                    | 384       |       |      |

| _                |                                         | Fixed Frequency Mode, CLASSD_SYNC=0                                         | 345.6 384 | 422.4 |      |

| F <sub>PWM</sub> | Class-D PWM Switching Frequency         | Fixed Frequency Mode, CLASSD_SYNC=1, f <sub>s</sub> = 44.1, 88.2 kHz        | 352.8     |       | kHz  |

|                  |                                         | Fixed Frequency Mode, CLASSD_SYNC=1, f <sub>s</sub> = 48, 96 kHz            | 384       |       |      |

| V <sub>os</sub>  | Output Offset Voltage                   | Idle Mode                                                                   | -1        | 1     | mV   |

|                  |                                         | A-Weighted, -60 dBFS                                                        | 110       |       |      |

| DNR              | Dynamic Range                           | A-Weighted, -60 dBFS, PWR MODE2                                             | 110       |       | dB   |

|                  |                                         | A-Weighted, Referenced to 1 % THD+N Output Level                            | 110       |       |      |

| SNR              | Signal to Noise Ratio                   | A-Weighted, Referenced to 1 % THD+N Output Level PWR_MODE2                  | 110       |       | dB   |

| K <sub>CP</sub>  | Click and Pop Performance               | Into and out of Shutdown, A-weighted                                        | 1.1       | 2.7   | mV   |

|                  | Full Scale Output Voltage               | f <sub>s</sub> <= 48kHz                                                     | 21        |       | dBV  |

|                  | Minimum Programmable Gain               | f <sub>s</sub> <= 48kHz                                                     | 11        |       | dBV  |

|                  | Maximum Programmable Gain               | f <sub>s</sub> <= 48kHz                                                     | 21        |       | dBV  |

|                  | Programmable Output Level Step<br>Size  |                                                                             | 0.5       |       | dB   |

|                  | Mute attenuation                        | Device in Software Shutdown or Muted in Normal Operation                    | 110       |       | dB   |

|                  | Chip to Chip Group Delay                | · ·                                                                         | -1        | 1     | μs   |

|                  | EMI Margin to EN55022B                  | 6" cable, Pout = 1W                                                         | -6        |       | dB   |

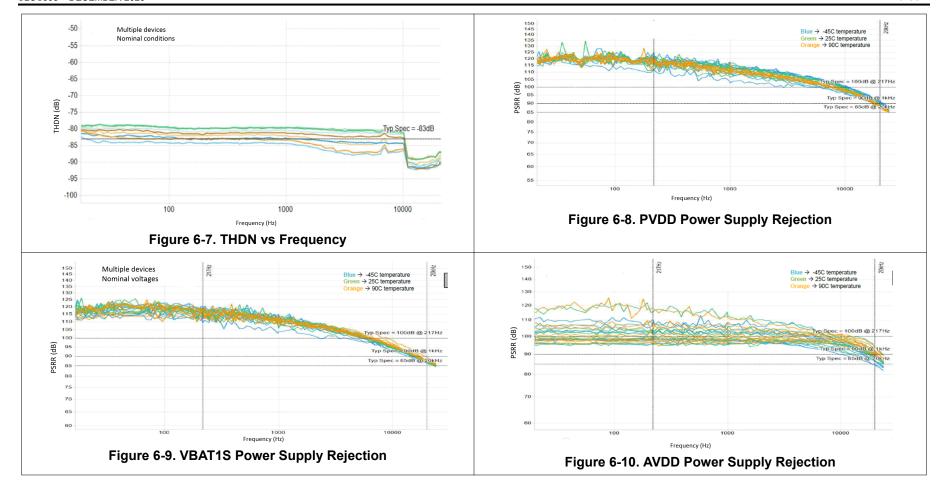

|                  |                                         | PVDD = 12 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz           | 100       |       |      |

|                  | PVDD Power Supply Rejection Ratio       | PVDD = 12 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 1 kHz            | 90        |       | dB   |

|                  | ,                                       | PVDD = 12 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz           | 85        |       |      |

|                  |                                         | VBAT1S = 3.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz        | 100       |       |      |

|                  | VBAT1S Power Supply Rejection           | VBAT1S = 3.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 1 kHz         | 90        |       | dB   |

|                  | Ratio                                   | VBAT1S = 3.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz        | 85        |       |      |

|                  |                                         | AVDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz          | 97        |       |      |

|                  | AVDD Power Supply Rejection Ratio       | AVDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 1 kHz           | 90        |       | dB   |

|                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | AVDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz          | 85        |       |      |

|                  |                                         | PVDD 217 Hz, 100-mVpp, Input f=1kHz @ 400mW                                 | -70       |       |      |

|                  |                                         | VBAT1S 217 Hz, 100-mVpp, Input f=1kHz @ 400mW                               | -70       |       |      |

|                  | Power Supply Intermodulation            | AVDD, 217 Hz, 100-mVpp, Input f=1kHz @ 400mW                                | -70       |       | dB   |

|                  |                                         | IOVDD 217 Hz, 100-mVpp, Input 1–1KHz @ 400mW                                | -70       |       |      |

|                        | PARAMETER                                                | TEST CONDITIONS                                                               | MIN    | TYP   | MAX    | UNIT             |

|------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------|--------|-------|--------|------------------|

|                        | Turn ON Time from Release of SW                          | No Volume Ramping                                                             |        | 1.14  |        |                  |

|                        | Shutdown                                                 | Volume Ramping                                                                |        | 5.35  |        | ms               |

|                        | Turn OFF Time From Assertion of                          | No Volume Ramping                                                             |        | 0.43  |        |                  |

|                        | SW Shutdown to Amp Hi-Z                                  | Volume Ramping                                                                |        | 5.9   |        | ms               |

|                        | Release of SW Shutdown to new assertion of SW Shutdown   |                                                                               | 1.5    |       |        | ms               |

| DIAGNOS                | STIC GENERATOR                                           |                                                                               |        |       |        |                  |

| THD+N                  | Total Harmonic Distortion and Noise                      | Pout=1W, DVC_LVL[7:0]=17h                                                     |        | -80   | -60    | dB               |

| f <sub>err</sub>       | Frequency Error                                          | Using internal oscillator                                                     |        | 5     |        | %                |

|                        | PERATURE                                                 |                                                                               |        |       |        |                  |

| SENSOR                 |                                                          |                                                                               |        |       |        |                  |

|                        | Resolution                                               |                                                                               |        | 8     |        | bits             |

|                        | Minimum Die Temperature<br>Measurement                   |                                                                               |        | -40   |        | °C               |

|                        | Maximum Die Temperature<br>Measurement                   |                                                                               |        | 150   |        | °C               |

|                        | Die Temperature Resolution                               |                                                                               |        | 1     |        | °C               |

|                        | Die Temperature Accuracy                                 |                                                                               | -5     |       | 5      | °C               |

| VOLTAGE<br>MONITOF     |                                                          |                                                                               |        |       |        |                  |

|                        | Resolution                                               |                                                                               |        | 12    |        | bits             |

|                        | Minimum PVDD Measurement                                 |                                                                               |        | 2     |        | V                |

|                        | Maximum PVDD Measurements                                |                                                                               |        | 16    |        | V                |

|                        | PVDD Resolution                                          |                                                                               |        | 20    |        | mV               |

|                        | PVDD Accuracy                                            |                                                                               | -100   |       | 100    | mV               |

|                        | Minimum VBAT1S Measurement                               |                                                                               |        | 2     |        | V                |

|                        | Maximum VBAT1S Measurement                               |                                                                               |        | 6     |        | V                |

|                        | VBAT1S Resolution                                        |                                                                               |        | 20    |        | mV               |

|                        | VBAT1S Accuracy                                          |                                                                               | -100   |       | 100    | mV               |

| TDM SER                | RIAL AUDIO PORT                                          |                                                                               | •      |       | ,      |                  |

|                        | PCM Sample Rates and FSYNC Input Frequency               | Typical values                                                                | 44.1   |       | 96     | kHz              |

|                        | SBCLK Input Frequency                                    | I <sup>2</sup> S/TDM Operation                                                | 0.7056 |       | 24.576 | MHz              |

|                        |                                                          | RMS Jitter below 40 kHz that can be tolerated without performance degradation |        |       | 0.5    |                  |

|                        | SBCLK Maximum Input Jitter                               | RMS Jitter above 40 kHz that can be tolerated without performance degradation |        |       | 1      | ns               |

|                        | SBCLK Cycles per FSYNC in I <sup>2</sup> S and TDM Modes | Other values: 24, 32, 48, 64, 96, 125, 128, 192, 250, 256, 384, 500           | 16     |       | 512    | Cycle            |

| PCM PLA                | AYBACK CHARACTERISTICS f <sub>s</sub> ≤ 48 kH            | -<br>Hz                                                                       | 1      |       |        |                  |

| f <sub>s</sub>         | Sample Rates                                             |                                                                               | 44.1   |       | 48     | kHz              |

|                        | Passband Frequency Meeting Ripple                        |                                                                               |        | 0.454 |        | fs               |

|                        | Passband Ripple                                          | 20Hz to LPF cutoff frequency                                                  | -0.3   |       | +0.3   | dB               |

|                        | Stan Band Attanustics                                    | ≥ 0.55 f <sub>s</sub>                                                         |        | 60    |        | 10               |

|                        | Stop Band Attenuation                                    | ≥ 1 f <sub>s</sub>                                                            |        | 65    |        | dB               |

|                        | Group Delay , Noise Gate enabled                         | DC to 0.454 f <sub>s</sub>                                                    |        |       | 19     | 1/f <sub>s</sub> |

| f <sub>s</sub> > 48 kH | łz                                                       |                                                                               | •      |       | '      |                  |

| fs                     | Sample Rates                                             |                                                                               | 88.2   |       | 96     | kHz              |

|                        | Passband Frequency Meeting Ripple                        | f <sub>s</sub> = 96 kHz                                                       |        | 0.375 |        | fs               |

|                        | Passband 3db Frequency                                   | f <sub>s</sub> = 96 kHz                                                       |        | 0.409 |        | f <sub>s</sub>   |

|                        | Passband Ripple                                          | DC to LPF cutoff frequency                                                    | -0.5   |       | 0.5    | dB               |

Submit Document Feedback

|        | PARAMETER                                     | TEST CONDITIONS                                                                                                                                   | MIN   | TYP  | MAX   | UNIT             |

|--------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

|        | Stop Band Attenuation                         | ≥ 0.55 f <sub>s</sub>                                                                                                                             |       | 60   |       | dB               |

|        | Otop Band Attendation                         | ≥ 1 f <sub>s</sub>                                                                                                                                |       | 65   |       | uБ               |

|        | Group Delay, Noise Gate enabled               | DC to 0.375 f <sub>s</sub> for 96 kHz                                                                                                             |       |      | 39    | 1/f <sub>s</sub> |

| SPEAKE | R CURRENT SENSE                               |                                                                                                                                                   |       |      |       |                  |

|        | Resolution                                    |                                                                                                                                                   |       | 16   |       | bits             |

| DNR    | Dynamic Range                                 | Un-Weighted, Relative to 0 dBFS                                                                                                                   |       | 66   |       | dB               |

| THD+N  | Total Harmonic Distortion and Noise           | f <sub>in</sub> = 1 kHz, Pout = 7. 5W                                                                                                             |       | -58  |       | dB               |

|        | Full Scale Input Current                      | -6dBFS Input Signal Level                                                                                                                         |       | 3.75 |       | Α                |

|        | Differential Mode Gain                        | Pout = 1W, using a 40Hz, -40dBFS pilot tone                                                                                                       | 0.98  |      | 1.02  |                  |

|        | Differential Mode Gain Variability            | Pout = 100mW to 0.1% THD+N, using a 40Hz, -40dBFS pilot tone                                                                                      | -2.5  |      | 1.5   | %                |

|        | Gain error over temperature                   | -20C to 70C, Pout=1W                                                                                                                              | -2.1  |      | +2.1  | %                |

|        | Offset                                        | HPF_FREQ_REC[2:0]=0h                                                                                                                              | -2    |      | 2     | mA               |

|        | Frequency Response                            | 20Hz-20kHz                                                                                                                                        | -0.1  |      | 0.1   | dB               |

|        | Group Delay                                   |                                                                                                                                                   |       | 8    |       | 1/f <sub>s</sub> |

|        | Common Mode Rejection Ratio                   | Signal into 8 Ohms applied 2X the signal level at 4 Ohms. Change seen in I-sense value between the two vs the expected I-sense value in db scale. | 80    |      |       | dB               |

| SPEAKE | R VOLTAGE SENSE                               |                                                                                                                                                   |       |      |       |                  |

|        | Resolution                                    |                                                                                                                                                   |       | 16   |       | bits             |

| DNR    | Dynamic Range                                 | Un-Weighted, Relative 0 dBFS                                                                                                                      |       | -72  |       | dB               |

| THD+N  | Total Harmonic Distortion and Noise           | f <sub>in</sub> = 1 kHz, Pout = 7.5W                                                                                                              |       | -60  |       | dB               |

|        | Full Scale Input Voltage                      |                                                                                                                                                   |       | 14   |       | V <sub>PK</sub>  |

|        | Differential Mode Gain                        | Pout = 1W, using a 40Hz - 40dBFS pilot tone                                                                                                       | 0.99  |      | 1.01  |                  |

|        | Differential Mode Gain Variability            | Pout = 100mW to 0.1% THD+N, using a 40Hz, -40dBFS pilot tone                                                                                      | -0.35 |      | +0.35 | %                |

|        | Gain error over temperature                   | -20C to 70C, Pout=1W                                                                                                                              | -0.7  |      | +0.7  | %                |

|        | Offset                                        | HPF_FREQ_REC[2:0]=0h                                                                                                                              | -4.5  |      | +4.5  | mV               |

|        | Frequency Response                            | 20Hz - 20kHz                                                                                                                                      | -0.1  |      | 0.1   | dB               |

|        | Group Delay                                   |                                                                                                                                                   |       | 8    |       | 1/f <sub>s</sub> |

| SPEAKE | R VOLTAGE/CURRENT SENSE RATIO                 |                                                                                                                                                   |       |      |       |                  |

|        | Differential Mode Gain Variability            | Pout = 50mW to 0.1% THD+N, using a 40Hz, -40dBFS pilot tone                                                                                       | -1.5  |      | 3     | %                |

|        | Gain error over temperature                   | -20C to 70C, Pout=1W                                                                                                                              | -2.1  |      | 2.1   | %                |

|        | Phase Error between V and I                   |                                                                                                                                                   |       | 300  |       | ns               |

| PROTEC | TION CIRCUITRY                                |                                                                                                                                                   |       |      |       |                  |

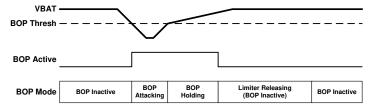

|        | Brownout Prevention Latency to First          | PWR_MODE2. Measured at BOP_TH0 of 8.25V.<br>BOP_SRC=1, CONV_VBAT_PVDD_MODE=1                                                                      |       | 15   |       | 110              |

|        | Attack                                        | PWR_MODE2. Measured at BOP_TH0 of 8.25V.<br>BOP_SRC=1, CONV_VBAT_PVDD_MODE=0                                                                      |       | 15   |       | μs               |

|        | Thermal Shutdown Temperature - Typical values |                                                                                                                                                   | 130   | 140  | 150   | °C               |

|        | Thermal Shutdown Retry                        | OTE_RETRY=1                                                                                                                                       |       | 1.5  |       | s                |

|        | Output Short Current Limit on PVDD            | Output to Output, Output to GND or Output to PVDD Short                                                                                           | 5     | 5.8  |       | Α                |

|        | Output Short Current Limit on VBAT1S          | Output to Output, Output to GND or Output to VBAT1S Short                                                                                         | 1.45  | 2.2  |       | Α                |

|        | VBAT1S Undervoltage Lockout                   | UVLO is asserted                                                                                                                                  | 2     |      |       | V                |

|        | Threshold                                     | UVLO is de-asserted                                                                                                                               |       |      | 2.3   | v                |

|        | AVDD Undervoltage Lockout                     | UVLO is asserted                                                                                                                                  | 1.45  |      |       | V                |

|        | Threshold                                     | UVLO is de-asserted                                                                                                                               |       | -    | 1.6   | v                |

|      | PARAMETER                                          | TEST CONDITIONS                 | MIN | TYP  | MAX  | UNI  |  |

|------|----------------------------------------------------|---------------------------------|-----|------|------|------|--|

|      | IOVDD Undervoltage Lockout                         | UVLO is asserted                | 0.7 |      |      | .,   |  |

|      | Threshold                                          | UVLO is de-asserted             |     |      |      | V    |  |

|      | VBAT1S Internal LDO Undervoltage Lockout Threshold | UVLO is asserted                | 4   |      |      | V    |  |

|      | VBAT1S Internal LDO Overvoltage Lockout Threshold  | OVLO is asserted                |     | '    | 5.55 | V    |  |

|      | DREG                                               | No external load                | 1.3 | 34   |      | V    |  |

|      | VBAT1S                                             | No external load                | 4.  | .8   |      | V    |  |

| PICA | L CURRENT CONSUMPTION                              |                                 | 1   |      | '    |      |  |

|      |                                                    | SDZ = 0, PVDD                   |     | 0.1  |      |      |  |

|      |                                                    | SDZ = 0, VBAT1S                 |     | 0.1  |      | ,    |  |

|      | Hardware Shutdown                                  | SDZ = 0, AVDD                   |     | 1    |      | ⊢ µA |  |

|      |                                                    | SDZ = 0, IOVDD                  |     | 0.1  |      |      |  |

|      |                                                    | All Clocks Stopped, PVDD        |     | 0.1  |      |      |  |

|      | Software Shutdown                                  | All Clocks Stopped, VBAT1S      |     | 1    |      | Π    |  |

|      |                                                    | All Clocks Stopped, AVDD        |     | 10   |      | μΑ   |  |

|      |                                                    | All Clocks Stopped, IOVDD       |     | 1    |      |      |  |

|      |                                                    | f <sub>s</sub> = 48 kHz, PVDD   |     | 0.05 |      |      |  |

|      | N. O. M.                                           | f <sub>s</sub> = 48 kHz, VBAT1S |     | 0.2  |      |      |  |

|      | Noise Gate Mode                                    | f <sub>s</sub> = 48 kHz, AVDD   |     | 2.8  |      | m    |  |

|      |                                                    | f <sub>s</sub> = 48 kHz, IOVDD  |     | 0.1  |      |      |  |

|      |                                                    | f <sub>s</sub> = 48 kHz, PVDD   |     | 0.02 |      |      |  |

|      | Idle Mode - PWR_MODE1,                             | f <sub>s</sub> = 48 kHz, VBAT1S |     | 3    |      |      |  |

|      | PWR_MODE3 and PWR_MODE5 (External VBAT1S)          | f <sub>s</sub> = 48 kHz, AVDD   |     | 8.6  |      | m/   |  |

|      |                                                    | f <sub>s</sub> = 48 kHz, IOVDD  |     | 0.1  |      |      |  |

|      |                                                    | f <sub>s</sub> = 48 kHz, PVDD   |     | 3.2  |      |      |  |

|      | Idle Mode - PWR_MODE2 (Internal VBAT1S)            | f <sub>s</sub> = 48 kHz, AVDD   |     | 9.3  |      | m    |  |

|      | 1219)                                              | f <sub>s</sub> = 48 kHz, IOVDD  |     | 0.1  | 0.1  |      |  |

|      |                                                    | f <sub>s</sub> = 48 kHz, PVDD   |     | 4.1  |      |      |  |

|      | Idle Mode - PWR_MODE4 (Internal VBAT1S)            | f <sub>s</sub> = 48 kHz, AVDD   |     | 9.3  |      |      |  |

|      | 1219)                                              | f <sub>s</sub> = 48 kHz, IOVDD  |     | 0.1  |      | m    |  |

|      | Idle Mode - IV Sense Disabled                      | f <sub>s</sub> = 48 kHz, AVDD   |     | 6.3  |      |      |  |

Submit Document Feedback

# 6.6 I<sup>2</sup>C Timing Requirements

T<sub>A</sub> = 25 °C, AVDD = IOVDD = 1.8 V (unless otherwisenoted)

|                            |                                                                                              | MIN                               | NOM MAX | UNIT |

|----------------------------|----------------------------------------------------------------------------------------------|-----------------------------------|---------|------|

| Standard-Mo                | ode                                                                                          |                                   |         |      |

| f <sub>SCL</sub>           | SCL clock frequency                                                                          | 0                                 | 100     | kHz  |

| t <sub>HD;STA</sub>        | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4                                 |         | μs   |

| t <sub>LOW</sub>           | LOW period of the SCL clock                                                                  | 4.7                               |         | μs   |

| HIGH                       | HIGH period of the SCL clock                                                                 | 4                                 |         | μs   |

| tsu;sta                    | Setup time for a repeated START condition                                                    | 4.7                               |         | μs   |

| HD;DAT                     | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                                 | 3.45    | μs   |

| SU;DAT                     | Data set-up time                                                                             | 250                               |         | ns   |

| r                          | SDA and SCL rise time                                                                        |                                   | 1000    | ns   |

| t <sub>f</sub>             | SDA and SCL fall time                                                                        |                                   | 300     | ns   |

| SU;STO                     | Set-up time for STOP condition                                                               | 4                                 |         | μs   |

| BUF                        | Bus free time between a STOP and START condition                                             | 4.7                               |         | μs   |

| Сь                         | Capacitive load for each bus line                                                            |                                   | 400     | pF   |

| Fast-Mode                  |                                                                                              |                                   |         |      |

| FSCL                       | SCL clock frequency                                                                          | 0                                 | 400     | kHz  |

| HD;STA                     | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6                               |         | μs   |

| t <sub>LOW</sub>           | LOW period of the SCL clock                                                                  | 1.3                               |         | μs   |

| HIGH                       | HIGH period of the SCL clock                                                                 | 0.6                               |         | μs   |

| tsu;sta                    | Setup time for a repeated START condition                                                    | 0.6                               |         | μs   |

| t <sub>HD:DAT</sub>        | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                                 | 0.9     | μs   |

| SU;DAT                     | Data set-up time                                                                             | 100                               |         | ns   |

| t <sub>r</sub>             | SDA and SCL rise time                                                                        | 20 + 0.1 ×<br>C <sub>b</sub> [pF] | 300     | ns   |

| t <sub>f</sub>             | SDA and SCL fall time                                                                        | 20 + 0.1 ×<br>C <sub>b</sub> [pF] | 300     | ns   |

| su;sto                     | Set-up time for STOP condition                                                               | 0.6                               |         | μs   |

| t <sub>BUF</sub>           | Bus free time between a STOP and START condition                                             | 1.3                               |         | μs   |

| C <sub>b</sub>             | Capacitive load for each bus line (10pF to 400pF)                                            |                                   | 400     | pF   |

| Fast-Mode P                | lus                                                                                          |                                   |         |      |

| FSCL                       | SCL clock frequency                                                                          | 0                                 | 1000    | kHz  |

| thd;sta                    | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.26                              |         | μs   |

| tow                        | LOW period of the SCL clock                                                                  | 0.5                               |         | μs   |

| HIGH                       | HIGH period of the SCL clock                                                                 | 0.26                              |         | μs   |

| SU;STA                     | Setup time for a repeated START condition                                                    | 0.26                              |         | μs   |

| t <sub>HD;DAT</sub>        | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                                 |         | μs   |

| SU;DAT                     | Data set-up time                                                                             | 50                                |         | ns   |

| r                          | SDA and SCL Rise Time                                                                        |                                   | 120     | ns   |

| <u>.</u><br>t <sub>f</sub> | SDA and SCL Fall Time                                                                        |                                   | 120     | ns   |

| SU;STO                     | Set-up time for STOP condition                                                               |                                   |         | μs   |

| t <sub>BUF</sub>           | Bus free time between a STOP and START condition                                             | 0.5                               |         | μs   |

| C <sub>b</sub>             | Capacitive load for each bus line                                                            |                                   | 550     | pF   |

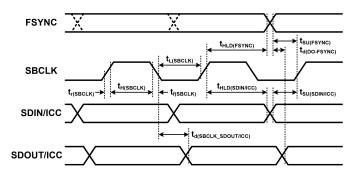

# **6.7 TDM Port Timing Requirements**

T<sub>A</sub> = 25 °C, AVDD = IOVDD = 1.8 V, 20 pF load on all outputs(unless otherwise noted)

|                        |                   | MIN | NOM MAX | UNIT |

|------------------------|-------------------|-----|---------|------|

| t <sub>H</sub> (SBCLK) | SBCLK high period | 20  |         | ns   |

| t <sub>L</sub> (SBCLK) | SBCLK low period  | 20  |         | ns   |

$T_A$  = 25 °C, AVDD = IOVDD = 1.8 V, 20 pF load on all outputs(unless otherwise noted)

|                             |                     |                                              | MIN | NOM | MAX | UNIT |

|-----------------------------|---------------------|----------------------------------------------|-----|-----|-----|------|

| t <sub>SU</sub> (FSYNC)     | FSYNC setup time    |                                              | 8   |     |     | ns   |

| t <sub>HLD</sub> (FSYNC)    | FSYNC hold time     |                                              | 8   |     |     | ns   |

| t <sub>SU</sub> (SDIN/ICC)  | SDIN/ICC setup time | SDIN/ICC setup time                          |     |     |     | ns   |

| t <sub>HLD</sub> (SDIN/ICC) | SDIN/ICC hold time  | SDIN/ICC hold time                           |     |     |     | ns   |

| $t_d(SBCLK\_SDOUT/ICC)$     | SBCLK to SDOUT/ICC  | 50% of SBCLK to 50% of SDOUT/ICC, IOVDD=1.8V |     |     | 13  |      |

|                             | delay               | 50% of SBCLK to 50% of SDOUT/ICC, IOVDD=1.2V |     |     | 17  | ns   |

| t <sub>r</sub> (SBCLK)      | SBCLK rise time     | 10 % - 90 % Rise Time                        |     |     | 8   | ns   |

| t <sub>f</sub> (SBCLK)      | SBCLK fall time     | 90 % - 10 % Fall Time                        |     |     | 8   | ns   |

6.8

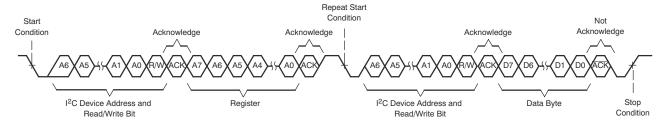

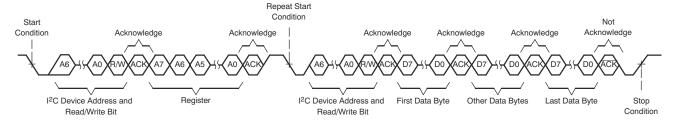

Figure 6-1. I2C Timing Diagram

Figure 6-2. TDM and ICC Timing Diagram

Submit Document Feedback

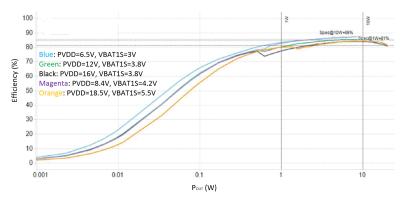

# **6.9 Typical Characteristics**

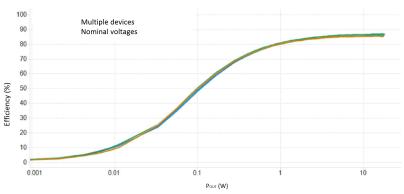

Figure 6-3. Efficiency vs Output Power - PWR\_MODE1

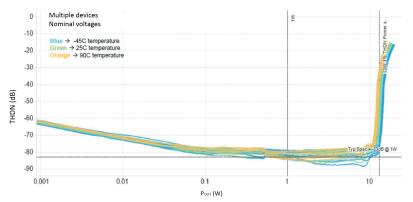

Figure 6-5. THDN vs Output Power Over Temperature

Figure 6-4. Efficiency vs Output Power - PWR\_MODE2

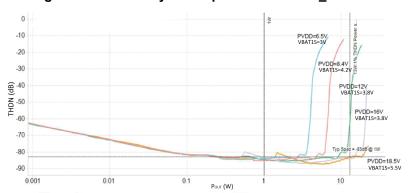

Figure 6-6. THDN vs Output Power Over Voltage

4 Submit Document Feedback

### 7 Parameter Measurement Information

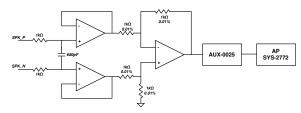

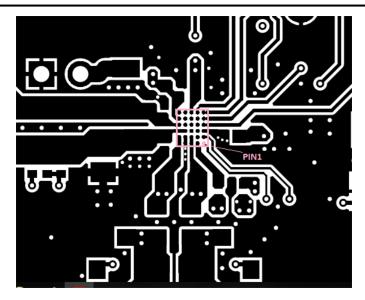

All typical characteristics for the devices are measured using the Bench Evaluation Module (EVM) and an Audio Precision SYS-2722 Audio Analyzer. A PSIA interface is used to allow the I<sup>2</sup>S interface to be driven directly into the SYS-2722. Speaker output terminals are connected to the Audio Precision Analyzer analog inputs through a differential-to-single ended (D2S) filter as shown below. The D2S filter contains a first order passive pole at 120 kHz. The D2S filter ensures the TAS2764 high performance class-D amplifier sees a fully differential matched loading at its outputs and the output signal is single ended.

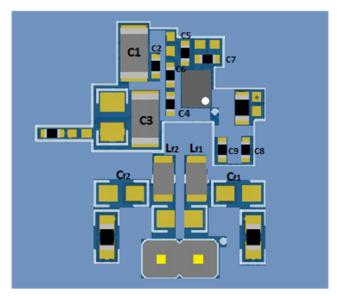

Figure 7-1. Differential To Single Ended (D2S) Filter

Alternatively, the AUX-0025 filter can be connected directly to the class-D outputs.

## **8 Detailed Description**

### 8.1 Overview

The TAS2764 is a mono digital input Class-D amplifier optimized for portable applications where efficient battery operation and small solution size are crucial. It integrates speaker voltage and current sensing and battery tracking limiting with brown out prevention. The device operates using a TDM/I<sup>2</sup>S and I<sup>2</sup>C interfaces.

Table 8-1. Full Scales

| Input/Output Signal | Full Scale Value |

|---------------------|------------------|

| Class-D Output      | 21 dBV           |

| Voltage Monitor     | 16 V             |

| Current Sense       | 3.75 A           |

| Voltage Sense       | 14 Vpk           |

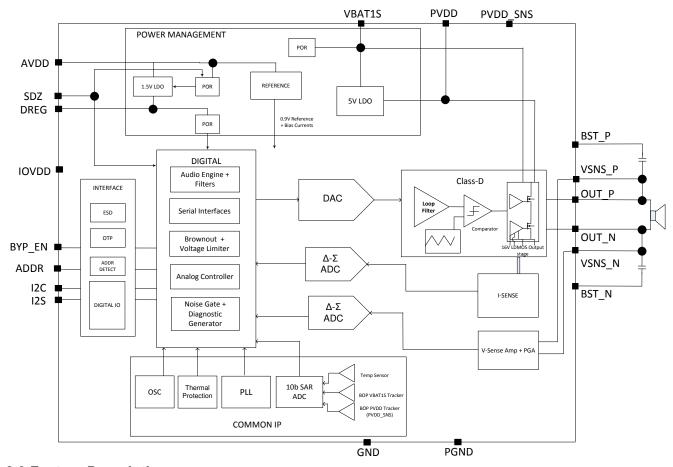

# 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Device Address Selection

The TAS2764 operates using a TDM/I $^2$ S interface. Audio input and output are provided via the FSYNC, SBCLK, SDIN and SDOUT pins using formats including I $^2$ S, Left Justified and TDM. Configuration and status are provided via the SDA and SCL pins using the I $^2$ C protocol.

Table 8-2 below illustrates how to configure the device for  $I^2C$  address. The slave addresses are shown left shifted by one bit with the R/W bit set to 0 (i.e. {ADDR[6:0],1b0}). Resistors with tolerance better than 5% must be used for setting the address configuration.

Submit Document Feedback

Table 8-2, I<sup>2</sup>C Address Selection

| I <sup>2</sup> C SLAVE ADDRESS | ADDR PIN       |

|--------------------------------|----------------|

| 0x70                           | Short to GND   |

| 0x72                           | 470 Ω to GND   |

| 0x74                           | 470 Ω to AVDD  |

| 0x76                           | 2.2k Ω to GND  |

| 0x78                           | 2.2k Ω to AVDD |

| 0x7A                           | 10 kΩ to GND   |

| 0x7C                           | 10 kΩ to AVDD  |

| 0x7E                           | Short to AVDD  |

The TAS2764 has a global 7-bit I<sup>2</sup>C address 0x80. When enabled, the device will additionally respond to I<sup>2</sup>C commands at this address regardless of the ADDR pin settings. This is used to speed up device configuration when using multiple TAS2764 devices and programming similar settings across all devices. The I<sup>2</sup>C ACK / NACK cannot be used during the multi-device writes since multiple devices are responding to the I<sup>2</sup>C command. The I<sup>2</sup>C CRC function should be used to ensure each device properly received the I<sup>2</sup>C commands. At the completion of writing multiple devices using the global address, the CRC at I2C\_CKSUM register should be checked on each device using the local address for a proper value. The global I<sup>2</sup>C address can be disabled using I2C\_GBL\_EN register bit. The I<sup>2</sup>C address is detected by sampling the ADDR pin when SDZ pin is released. Additionally, the address may be re-detected by setting I2C\_AD\_DET register bit high after power up and the ADDR pin will be re-sampled.

### 8.3.2 General I<sup>2</sup>C Operation

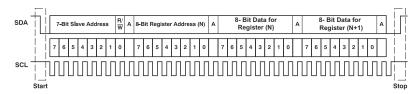

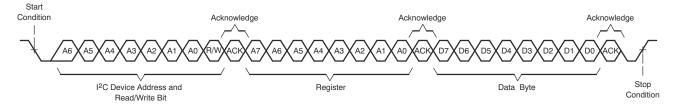

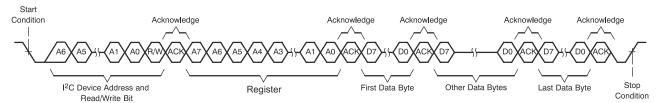

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system using serial data transmission. The address and data 8-bit bytes are transferred most-significant bit (MSB) first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start, and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period.

The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The device holds SDA low during the acknowledge clock period to indicate acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bi-directional bus using a wired-AND connection.

Figure 8-1. Typical I<sup>2</sup>C Sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. Figure 8-1 shows a generic data transfer sequence.

For information about pull-up resistors and single-byte/multiple-byte transfers see Section 11.

### 8.3.3 Register Organization

Device configuration and coefficients are stored using a page and book scheme. Each page contains 128 bytes and each book contains 256 pages. All device configuration registers are stored in book 0, page 0, which is the default setting at power up (and after a software reset). The book and page can be set by the *BOOK* and *PAGE* registers respectively.

#### Note

Programming register bits from Book\_0 and Page\_4 needs to be done in groups of four registers (32 bit format), each byte corresponding to a register and with less significant byte programmed to 00h. For instance, when programing DC level for diagnostic generator, registers 08,09,0A will be programmed to the desired value and register 0B will be programmed to 00h.

#### 8.4 Device Functional Modes

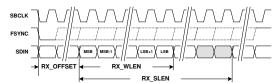

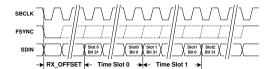

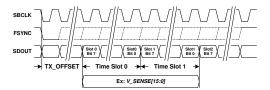

#### **8.4.1 TDM Port**

The TAS2764 provides a flexible TDM serial audio port. The port can be configured to support a variety of formats including stereo I<sup>2</sup>S, Left Justified and TDM. Mono audio playback is available via the SDIN pin. The SDOUT pin is used to transmit sample streams including speaker voltage and current sense, PVDD voltage, die temperature and channel gain.

The TDM serial audio port supports up to 16 of 32-bit time slots at 44.1/48 kHz or 8 of 32-bit time slots at a 88.2/96 kHz sample rate. Valid SBCLK to FSYNC ratios are 16, 24, 32, 48, 64, 96, 128, 192, 256, and 512. The device will automatically detect the number of time slots and it does not need to be programmed.

By default, the TAS2764 will automatically detect the PCM playback sample rate. This can be disabled and manually configured by setting the *AUTO RATE* register bit high.

The SAMP\_RATE[2:0] and SAMP\_RATIO[3:0] register bits are used to configure the PCM audio sample rate when AUTO\_RATE register bit is high (auto detection of TDM sample rate is disabled). The TAS2764 employs a robust clock fault detection engine that will automatically volume ramp down the playback path if FSYNC does not match the configured sample rate (if AUTO\_RATE = 1) or the ratio of SBCLK to FSYNC is not supported (minimizing any audible artifacts). Once the clocks are detected to be valid in both frequency and ratio, the device will automatically volume ramp the playback path back to the configured volume and resume playback.

When using the auto rate detection the sampling rate and SBCLK to FSYNC ration detected on the TDM bus is reported back on the read-only register bits FS\_RATE[2:0] and FS\_RATIO[3:0] respectively.