LP8555

SNVS857-FEBRUARY 2014

# LP8555 High-Efficiency LED Backlight Driver for Tablet PCs

#### **Features**

- Dual High-Efficiency DC/DC Boost Converters

- 2.7-V to 20-V VDD Range

- 12 50-mA High-Precision LED Current Sinks With 12-Bit Brightness Control

- Adaptive LED Current Sink Headroom Controls for Maximum System Efficiency

- LED String Count Auto-Detection

- Phase-Shifted PWM Mode for Reduced Audible

- PWM Input Duty-Cycle and/or I<sup>2</sup>C-Register **Brightness Control**

- Hybrid PWM and Current Dimming for Higher LED **Drive Optical Efficiency**

- Flexible CABC Support

- EPROM, I<sup>2</sup>C-Register, or External Resistors for

- Improved Boost EMI Performance with Slew-Rate Control, Spread Spectrum, and Phase-Shifted Switching

- **Extensive Fault Detection Schemes**

## **Applications**

Tablet LCD Display LED Backlight

## 3 Description

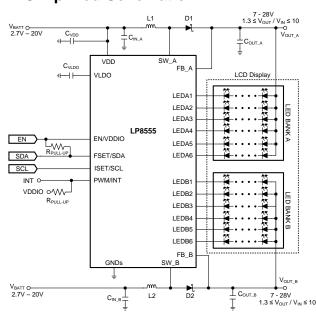

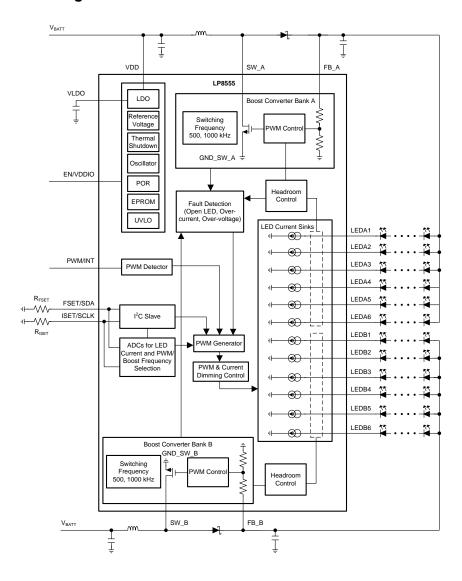

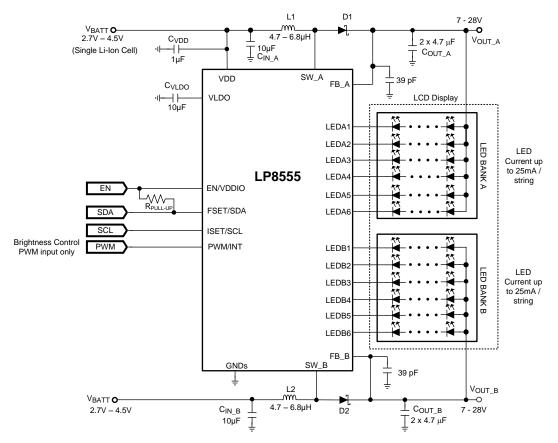

The LP8555 is a high efficiency LED driver with integrated dual DC-DC boost converters. It has 12 high-precision current sinks that can be controlled by a PWM input signal, an I<sup>2</sup>C master, or both.

Dual-boost configuration of LP8555 shares the load to two inductors and allows thinner overall solution size and better efficiency compared to single-boost solutions. 12 LED strings allows driving high number LEDs with optimal efficiency since boost conversion ratio can be kept low.

The boost converter has adaptive output voltage control based on the LED current sink headroom power voltages. This feature minimizes the consumption by adjusting the voltage to lowest sufficient level in all conditions.

The LED string auto-detect function enables use of the same device in systems with 2 to 12 LED strings for the maximum design flexibility. Proprietary Hybrid PWM and Current dimming mode enables additional system power savings. Phase-shift PWM allows reduced audible noise and smaller boost output capacitors. Flexible CABC support combines brightness level selections based on the PWM input and I<sup>2</sup>C commands.

#### **Device Information**

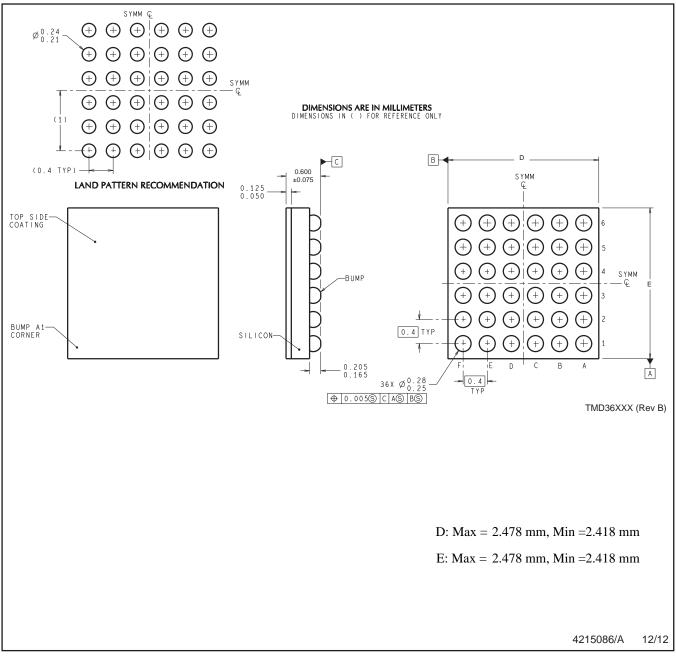

| ORDER NUMBER | PACKAGE    | BODY SIZE         |

|--------------|------------|-------------------|

| LP8555YFQR   | DSBGA (36) | 2,478mm x 2,478mm |

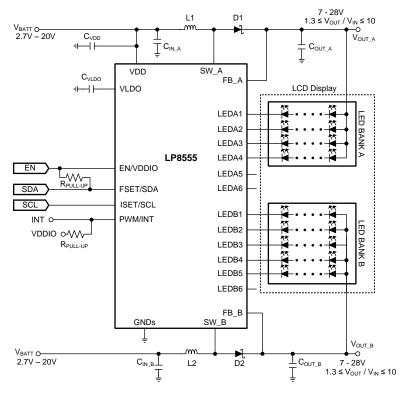

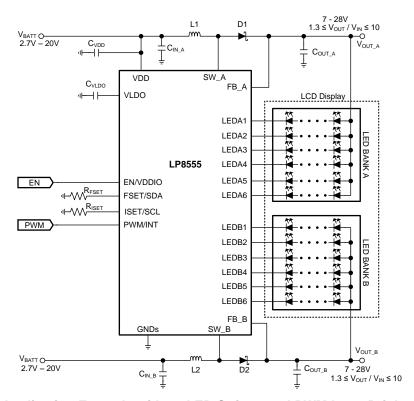

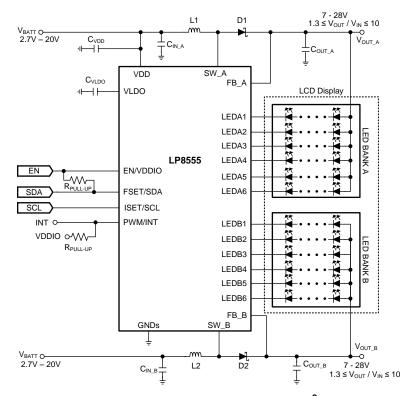

# Simplified Schematic

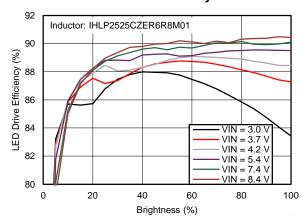

#### **LED Drive Efficiency**

# **Table of Contents**

| 1 | Features 1                                                   | 8.2 Functional Block Diagram 11         |

|---|--------------------------------------------------------------|-----------------------------------------|

| 2 | Applications 1                                               | 8.3 Features Description 12             |

| 3 | Description 1                                                | 8.4 Device Functional Modes29           |

| 4 | Simplified Schematic 1                                       | 8.5 Register Maps30                     |

| 5 | Revision History2                                            | 9 Application and Implementation 46     |

| 6 | Terminal Configuration and Functions                         | 9.1 Application Information             |

| 7 | _                                                            | 9.2 Typical Applications                |

| ′ | Specifications                                               | 10 Power Supply Recommendations 54      |

|   | 3                                                            | 11 Layout 55                            |

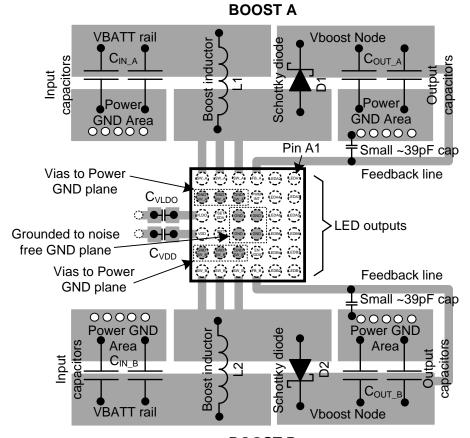

|   | 7.2 Handling Ratings                                         | 11.1 Layout Guidelines 55               |

|   | 7.4 Thermal Information                                      | 11.2 Layout Example 56                  |

|   | 7.5 Electrical Characteristics (3) 5                         | 12 Device and Documentation Support 57  |

|   | 7.6 I <sup>2</sup> C Serial Bus Timing Parameters (FSET/SDA, | 12.1 Trademarks                         |

|   | ISET/SCL)                                                    | 12.2 Electrostatic Discharge Caution 57 |

|   | 7.7 Typical Characteristics 8                                | 12.3 Glossary57                         |

| 8 | Detailed Description 11                                      | 13 Mechanical, Packaging, and Orderable |

|   | 8.1 Overview 11                                              | Information 58                          |

# 5 Revision History

| DATE              | REVISION | NOTES           |

|-------------------|----------|-----------------|

| February 21, 2014 | *        | Initial Release |

Submit Documentation Feedback

# 6 Terminal Configuration and Functions

#### YFQ (DSBGA) 36 Bumps TOP воттом (LEDB1) (LEDB2) (FB\_B) (SW\_B) (SW\_B) (SW\_B) (SW\_B) (SW\_B (FB\_B (LEDB2) (LEDB1 GND SW\_B GND SW\_B EN VDDIO (LEDB3) (LEDB4) (LEDB4) (LEDB3) ISET/ SCL GND (LEDB5) (LEDB6) ( GND ) (GND) ( VDD ) GND (LEDB6 (LEDB5 (LEDA5) (LEDA6) (GND) (GND) (VLDO) (VLDO) (GND GND (LEDA6) (LEDA5 GND SW\_A GND SW\_A (GND SW\_A GND SW\_A PWM/ INT (LEDA3) (LEDA4) (LEDA4) (LEDA3) (LEDA2) (LEDA1) (LEDA2) (SW\_A (LEDA1) (FB\_A) (SW\_A) (SW\_A) (SW\_A) (SW\_A SW\_A FB\_A

#### **Terminal Functions**

| TERM                       | /INAL    | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER                     | NAME     | ITPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

| A1, A2, A3,<br>B1, B2, B3, | LEDAx    | Α     | LED Bank A Current Sink Terminal. If unused, this terminal may be left floating.                                                                                                                                                                                                                                                                                  |

| A4, A5, A6,<br>B4, B5, B6  | LEDBx    | Α     | LED Bank A Current Sink Terminal. If unused, this terminal may be left floating.                                                                                                                                                                                                                                                                                  |

| C1                         | FB_A     | Α     | Feedback terminal for the Bank A Boost Converter.                                                                                                                                                                                                                                                                                                                 |

| C2                         | PWM/INT  | I     | Dual function terminal. When BRTMODE = 00, 10, or 11, this is a PWM input terminal. When BRTMODE = 01, this terminal is a programmable interrupt terminal. In this mode, this is an open drain output that pulls low when a fault condition occurs.                                                                                                               |

| C3, C4, D3, D4             | GND      | G     | Ground for analog and digital blocks. These terminals should be connected to a noise-free GND plane if possible (separate plane than GND_SW_x terminals).                                                                                                                                                                                                         |

| C5                         | EN/VDDIO | I     | Backlight Enable terminal and VDDIO power terminal + reference terminal for I <sup>2</sup> C communication. This terminal should be connected to IO voltage with low impedance route to avoid voltage ripple on this terminal.                                                                                                                                    |

| C6                         | FB_B     | Α     | Feedback terminal for the Bank B Boost Converter.                                                                                                                                                                                                                                                                                                                 |

| D1, E1, F1                 | SW_A     | Α     | Bank A Boost Converter Switch                                                                                                                                                                                                                                                                                                                                     |

| D2, E2, F2                 | GND_SW_A | G     | Bank A Boost Converter Switch Ground. These terminals can be connected to noisy GND due to high current spikes.                                                                                                                                                                                                                                                   |

| D5, E5, F5                 | GND_SW_B | G     | Bank B Boost Converter Switch Ground. These terminals can be connected to noisy GND due to high current spikes.                                                                                                                                                                                                                                                   |

| D6, E6, F6                 | SW_B     | Α     | Bank B Boost Converter Switch                                                                                                                                                                                                                                                                                                                                     |

| E3                         | FSET/SDA | I/O/A | Dual Function terminal. When $I^2C$ is not used (for example, BRTMODE = 00), this terminal can be used to set the boost switching frequency and/or LED PWM frequency by connecting a resistor between the terminal and a ground reference. When $I^2C$ is used (for example, BRTMODE = 01, 10, or 11), this terminal is connected to a SDA line of an $I^2C$ bus. |

| E4                         | ISET/SCL | I/A   | Dual Function terminal. When $I^2C$ is not used (for example, if BRTMODE=00), this terminal can be used to set the full-scale LED current by connecting a resistor between the terminal and a ground reference. When $I^2C$ is used (for example, BRTMODE = 01, 10, or 11), this terminal is connected to a SCL line of an $I^2C$ bus.                            |

| F3                         | VLDO     | Р     | Internal LDO Output terminal. $C_{\text{VLDO}}$ bypass capacitor must be connected between this terminal and ground.                                                                                                                                                                                                                                              |

| F4                         | VDD      | Р     | Device power supply terminal. Provide 2.7-V to 20-V supply to this terminal. This terminal is an input of the internal LDO regulator. The output of the internal LDO powers the device blocks.                                                                                                                                                                    |

|                            |          |       | an input of the internal LDO regulator. The output of the internal LDO powers the device                                                                                                                                                                                                                                                                          |

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

|                                                   |                                            | MIN  | MAX                   | UNIT |

|---------------------------------------------------|--------------------------------------------|------|-----------------------|------|

| VDD                                               | Voltage on VDD                             | -0.3 | 22                    |      |

| VLDO                                              | Voltage on VLDO                            |      |                       | ·    |

| V(PWM/INT,<br>EN/VDDIO/<br>FSET/SDA,<br>ISET/SCL) | Voltage on logic terminals                 | -0.3 | 6                     | V    |

| V(SW_A, SW_B,<br>LEDxy, FB_x)                     | Voltage on analog terminals                | -0.3 | 31                    |      |

| P <sub>D</sub>                                    | Continuous Power Dissipation (2)           |      | Internally<br>limited |      |

| T <sub>A</sub>                                    | Operating ambient temperature range (3)    | -40  | 85                    |      |

| T <sub>J</sub>                                    | Maximum operating junction temperature (3) | -40  | 125                   | °C   |

| T <sub>soldering</sub>                            | Note (4)                                   |      |                       |      |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

- (2) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typ.) and disengages at T<sub>J</sub> = 137°C (typ.).

- (3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be degraded. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

- (4) For detailed soldering specifications and information, please refer to Application Note AN1112.

### 7.2 Handling Ratings

|                      | .99                                           |     |      |      |

|----------------------|-----------------------------------------------|-----|------|------|

|                      |                                               | MIN | MAX  | UNIT |

| T <sub>STORAGE</sub> | Storage temp range                            | -65 | 150  | °C   |

| $V_{HBM}$            | Human body model (HBM) voltage <sup>(1)</sup> |     | 2000 |      |

| V <sub>CDM</sub>     | Charged device model (CDM) (2)                |     | 250  | V    |

- (1) Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Terminals listed as 2 kV may actually have higher performance.

- (2) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Terminals listed as 250 V may actually have higher performance

Submit Documentation Feedback

# 7.3 Recommended Operating Conditions (1)(2)

Over operating free-air temperature range (unless otherwise noted)

|                                                              | MIN | MAX | UNIT |

|--------------------------------------------------------------|-----|-----|------|

| VDD – Voltage on VDD                                         | 2.7 | 20  |      |

| VLDO – Voltage on VLDO                                       | 2.7 | 5.5 |      |

| V (EN/VDDIO) – Supply voltage for digital I/O                | 1.7 | 5.5 | V    |

| V (PWM/INT, FSET/SDA, ISET/SCL) – Voltage on logic terminals | 0   | 5.5 |      |

| V (SW_A, SW_B, LEDxy, FB_x)                                  | 0   | 28  |      |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device a these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.4 Thermal Information

Over operating free-air temperature range (unless otherwise noted)

|               | THERMAL METRIC <sup>(1)</sup>                                            |      | UNIT |

|---------------|--------------------------------------------------------------------------|------|------|

| $\theta_{JA}$ | Junction-to-ambient thermal resistance (θ <sub>JA</sub> ) <sup>(2)</sup> | 76.2 | °C/W |

| $\theta_{JC}$ | Junction-to-case (top) thermal resistance                                | 0.3  | °C/W |

| $\theta_{JB}$ | Junction-to-board thermal resistance                                     | 16.3 | °C/W |

| $\Psi_{JT}$   | Junction-to-top characterization parameter                               | 1.8  | °C/W |

| $\Psi_{JB}$   | Junction-to-board characterization parameter                             | 16.3 | °C/W |

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics (1)(2)

Limits apply over the full ambient temperature range  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$ . Unless otherwise specified: VDD = 3.6 V, EN/VDDIO = 1.8 V, L1 = L2 = 6.8  $\mu$ H,  $C_{IN\ A}$  =  $C_{IN\ B}$  = 10  $\mu$ F,  $C_{OUT\ A}$  =  $C_{OUT\ B}$  = 10  $\mu$ F,  $C_{VLDO}$  = 10  $\mu$ F,  $C_{VDD}$  = 1  $\mu$ F. (3)

|                       | PARAMETER                              | TEST CONDITIONS                                          | MIN | TYP                  | MAX | UNIT |

|-----------------------|----------------------------------------|----------------------------------------------------------|-----|----------------------|-----|------|

| I <sub>IN</sub>       | Shutdown supply current                | EN = L and PWM/INT = L                                   |     |                      | 1   |      |

|                       | Standby supply current                 | EN = H and PWM/INT = L, ON bit = 0                       |     | 19                   | 30  | μA   |

|                       | Normal mode supply current             | EN = H, ON bit = 1, no current going through LED outputs |     | 4.2                  |     | mA   |

| f <sub>OSC</sub>      | Internal oscillator frequency accuracy |                                                          | -7% |                      | 7%  |      |

| T <sub>TSD</sub>      | Thermal shutdown threshold             |                                                          |     | 150                  |     | °C   |

| T <sub>TSD_hyst</sub> | Thermal shutdown hysteresis            |                                                          |     | 13                   |     |      |

| t <sub>START-UP</sub> | Start-up time <sup>(4)</sup>           |                                                          |     | 5                    | 7   | ms   |

| BOOST CON             | VERTER (Applies for both boost of      | converters)                                              |     |                      |     |      |

| V <sub>BST_MIN</sub>  | Minimum output voltage                 |                                                          |     | 7                    |     | V    |

| V <sub>BST_MAX</sub>  | Maximum output voltage                 | VMAX = 00<br>VMAX = 01<br>VMAX = 10<br>VMAX = 11         |     | 18<br>22<br>25<br>28 |     | V    |

| I <sub>MAX</sub>      | SW FET current limit                   |                                                          | 2.7 | 3.1                  | 3.5 | Α    |

| R <sub>NMOS</sub>     | NMOS switch-ON resistance              | I <sub>SW</sub> = 0.5 A                                  |     | 0.16                 |     | Ω    |

| I <sub>LOAD</sub>     | Continuous load current                | VBATT = 3 V, VOUT = 26.6 V.<br>Typical application.      |     | 180                  |     | mA   |

- All voltages are with respect to the potential at the GND terminals.

- Min and Max limits are specified by design, test, or statistical analysis.

- Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics

- Start-up time is measured from the moment the ON bit is set high to the moment when backlight is enabled.

Copyright © 2014, Texas Instruments Incorporated

All voltages are with respect to the potential at the GND terminals.

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

# Electrical Characteristics(1)(2) (continued)

Limits apply over the full ambient temperature range  $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ . Unless otherwise specified: VDD = 3.6 V, EN/VDDIO = 1.8 V, L1 = L2 = 6.8  $\mu$ H,  $C_{\text{IN\_A}} = C_{\text{IN\_B}} = 10~\mu$ F,  $C_{\text{OUT\_B}} = 10~\mu$ F,  $C_{\text{VLDO}} = 10~\mu$ F,  $C_{\text{VDD}} = 1~\mu$ F.

|                                   | PARAMETER                                                   | TEST CONDITIONS                                                                                                                                         | MIN | TYP                              | MAX   | UNIT |

|-----------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-------|------|

| $f_{SW}$                          | Switching frequency                                         | BFREQ = 0<br>BFREQ = 1                                                                                                                                  |     | 500<br>1000                      |       | kHz  |

| $f_{\sf SW\_ACCURACY}$            | Boost oscillator accuracy                                   |                                                                                                                                                         | -7% |                                  | 7%    |      |

| V <sub>OVP_THR</sub>              | Overvoltage protection voltage threshold                    |                                                                                                                                                         | V   | BST_MAX<br>+1.6 V                |       | V    |

| V <sub>OUT</sub> /V <sub>IN</sub> | Conversion ratio                                            | No load, BFREQ = 1                                                                                                                                      | 1.3 |                                  | 10    |      |

| $\Delta V_{SW}/t_{off-on}$        | SW node voltage slew rate during OFF-to-ON transition       | Load current 120 mA. Boost slew rate set to fastest (SRON = 00b).                                                                                       |     | 12.5                             |       | \//  |

| $\Delta V_{SW}/t_{on-off}$        | SW node voltage slew rate during ON-to-OFF transition       |                                                                                                                                                         |     | 19.5                             |       | V/ns |

| $f_{MOD}$                         | Modulation frequency<br>(percentage of the SW<br>frequency) | FMOD_DIV = 00<br>FMOD_DIV = 01<br>FMOD_DIV = 10<br>FMOD_DIV = 11                                                                                        |     | 0.47%<br>0.27%<br>0.17%<br>0.12% |       |      |

| CURRENT SINK                      | (S                                                          |                                                                                                                                                         |     |                                  |       |      |

| I <sub>LEAKAGE</sub>              | Leakage current                                             | Outputs LEDA1LEDB6, V <sub>LEDxx</sub> = 28 V                                                                                                           |     |                                  | 1     | μΑ   |

| I <sub>MAX</sub>                  | Maximum sink current LEDA1B6                                |                                                                                                                                                         |     | 50                               |       | mA   |

| I <sub>OUT</sub>                  | Output current accuracy <sup>(5)</sup>                      | Output current set to 23 mA.                                                                                                                            | -4% |                                  | 4%    |      |

| I <sub>MATCH</sub>                | Matching (5)                                                | Current scale set to 23 mA. PWM = 100%                                                                                                                  |     | 1%                               | 5%    |      |

| $f_{LED\_PWM}$                    | LED switching frequency                                     | PFREQ = 000b<br>PFREQ = 111b                                                                                                                            |     | 4.9<br>39.1                      |       | kHz  |

| V                                 | Saturation voltage (6)                                      | Output current set to 23 mA                                                                                                                             |     | 200                              | 260   | mV   |

| V <sub>SAT</sub>                  | Saturation voltage                                          | Output current set to 30 mA                                                                                                                             |     | 250                              | 340   | IIIV |

| PWM INTERFA                       | CE CHARACTERISTICS                                          | ,                                                                                                                                                       |     |                                  |       |      |

| $f_{PWM}$                         | PWM input frequency                                         |                                                                                                                                                         | 75  |                                  | 50000 | Hz   |

| t <sub>MIN_ON</sub>               | Minimum pulse ON time                                       |                                                                                                                                                         |     | 100                              |       | ns   |

| t <sub>MIN_OFF</sub>              | Minimum pulse OFF time                                      |                                                                                                                                                         |     | 100                              |       | 115  |

| t <sub>start-up</sub>             | Turn-on delay from standby to backlight on                  | PWM input active, ON bit written high                                                                                                                   |     |                                  | 7     | ms   |

| t <sub>STBY</sub>                 | Turn-off delay                                              | PWM input low time before entering standby mode (if PWMSB = 1)                                                                                          |     | 52                               |       | ms   |

| PWM <sub>RES</sub>                | PWM input resolution                                        | $f_{\rm IN}$ < 2.4 kHz<br>$f_{\rm IN}$ < 4.8 kHz<br>$f_{\rm IN}$ < 9.6 kHz<br>$f_{\rm IN}$ < 19.5 kHz<br>$f_{\rm IN}$ < 25 kHz<br>$f_{\rm IN}$ < 50 kHz |     | 12<br>12<br>11<br>10<br>9<br>8   |       | bits |

| UNDERVOLTA                        | GE PROTECTION                                               | -                                                                                                                                                       |     |                                  |       |      |

| V <sub>UVLO</sub>                 | VDD UVLO threshold voltage                                  | VDD falling                                                                                                                                             |     | 2.5                              |       | V    |

| LOGIC INTERF                      | ACE                                                         | VDD rising                                                                                                                                              |     | 2.6                              |       |      |

| Logic Input EN/\                  |                                                             |                                                                                                                                                         |     |                                  |       |      |

|                                   | Supply voltage range                                        |                                                                                                                                                         | 1.7 |                                  | 5.5   | V    |

| V <sub>EN/VDDIO</sub>             | Input current                                               |                                                                                                                                                         | 1.7 | 20                               | 5.5   |      |

| l <sub>l</sub>                    | input current                                               |                                                                                                                                                         |     | 20                               |       | μΑ   |

<sup>(5)</sup> Output Current Accuracy is the difference between the actual value of the output current and programmed value of this current. Matching is the maximum difference from the average. For the constant current sinks on the part (OUTA1 to OUTB6), the following are determined: the maximum output current (MAX), the minimum output current (MIN), and the average output current of all outputs (AVG). Matching number is calculated: (MAX-MIN)/AVG. The typical specification provided is the most likely norm of the matching figure for all parts. LED current sinks were characterized with 1 V headroom voltage. Note that some manufacturers have different definitions in use.

(6) Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at 1 V.

Submit Documentation Feedback

Copyright © 2014, Texas Instruments Incorporated

# Electrical Characteristics<sup>(1)(2)</sup> (continued)

Limits apply over the full ambient temperature range  $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ . Unless otherwise specified: VDD = 3.6 V, EN/VDDIO = 1.8 V, L1 = L2 = 6.8  $\mu$ H,  $C_{\text{IN\_A}} = C_{\text{IN\_B}} = 10~\mu$ F,  $C_{\text{OUT\_A}} = C_{\text{OUT\_B}} = 10~\mu$ F,  $C_{\text{VLDO}} = 10~\mu$ F,  $C_{\text{VDD}} = 1~\mu$ F.

|                 | PARAMETER                           | TEST CONDITIONS             | MIN               | TYP MAX           | UNIT |

|-----------------|-------------------------------------|-----------------------------|-------------------|-------------------|------|

| Logic Inpu      | t PWM/INT, FSET/SDA, ISET/SCL       |                             |                   |                   |      |

| V <sub>IL</sub> | Input low level                     |                             |                   | 0.3 x<br>EN/VDDIO | V    |

| V <sub>IH</sub> | Input high level                    |                             | 0.7 x<br>EN/VDDIO |                   | V    |

| l <sub>l</sub>  | Input current, VIO = 1.7 V to 5.5 V |                             | -1.0              | 1.0               | μΑ   |

| Logic Outp      | out FSET/SDA, PWM/INT               |                             |                   |                   |      |

| V <sub>OL</sub> | Output low level                    | I <sub>PULL-UP</sub> = 3 mA |                   | 0.3 0.4           | V    |

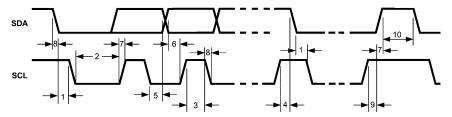

7.6 I<sup>2</sup>C Serial Bus Timing Parameters (FSET/SDA, ISET/SCL)

|                       |                                                                                                   | MIN                   | TYP MAX | UNIT |

|-----------------------|---------------------------------------------------------------------------------------------------|-----------------------|---------|------|

| f <sub>SCL</sub>      | Clock Frequency                                                                                   |                       | 400     | kHz  |

| 1                     | Hold Time (repeated) START Condition                                                              | 0.6                   |         | μs   |

| 2                     | Clock Low Time                                                                                    | 1.3                   |         | μs   |

| 3                     | Clock High Time                                                                                   | 600                   |         | ns   |

| 4                     | Setup Time for a Repeated START Condition                                                         | 600                   |         | ns   |

| 5                     | Data Hold Time                                                                                    | 50                    |         | ns   |

| 6                     | Data Setup Time                                                                                   | 100                   |         | ns   |

| 7                     | Rise Time of SDA and SCL                                                                          | 20+0.1xC <sub>b</sub> | 300     | ns   |

| 8                     | Fall Time of SDA and SCL                                                                          | 15+0.1xC <sub>b</sub> | 300     | ns   |

| 9                     | Set-up Time for STOP condition                                                                    | 600                   |         | ns   |

| 10                    | Bus Free Time between a STOP and a START Condition                                                | 1.3                   |         | μs   |

| C <sub>b</sub>        | Capacitive Load Parameter for Each Bus Line. Load of One Picofarad Corresponds to One Nanosecond. | 10                    | 200     | ns   |

| t <sub>response</sub> | Delay from EN/VDDIO rising to I <sup>2</sup> C bus active                                         |                       | 1       | ms   |

Figure 1. I<sup>2</sup>C Timing Parameters

SNVS857 – FEBRUARY 2014 www.ti.com

# TEXAS INSTRUMENTS

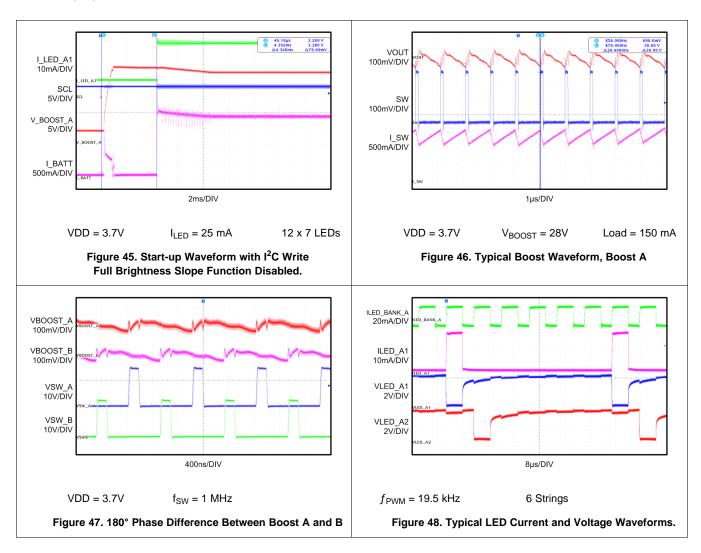

### 7.7 Typical Characteristics

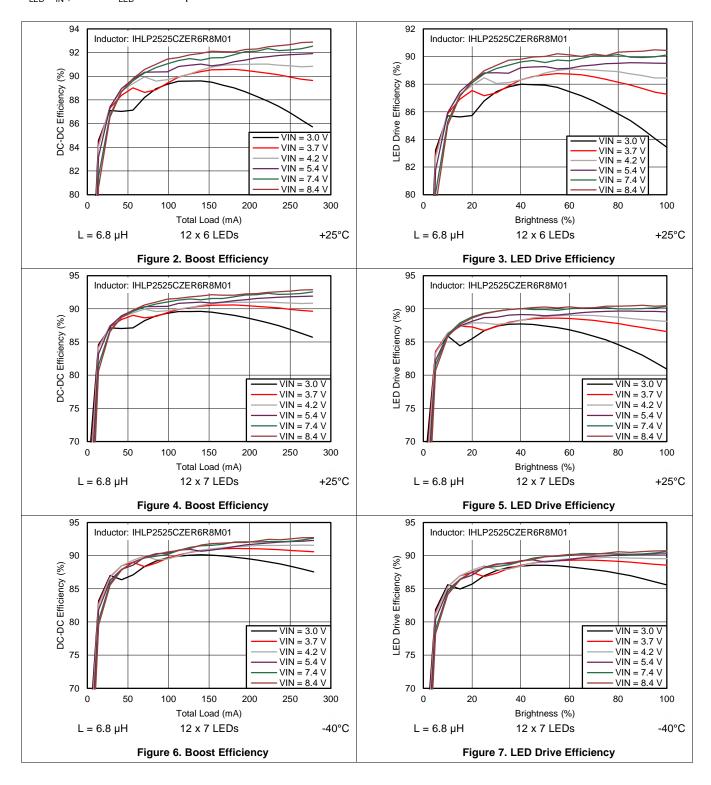

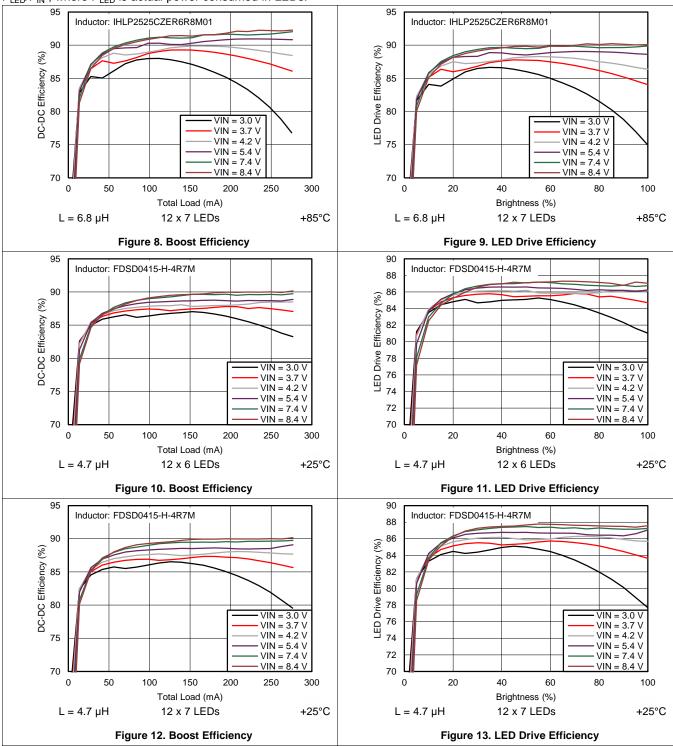

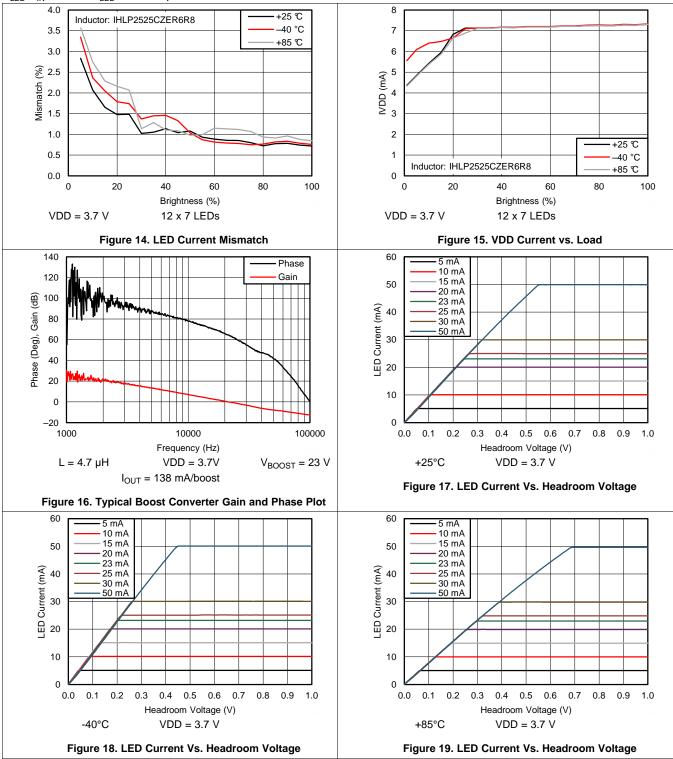

Measured at room temperature unless otherwise noted. Maximum LED current set to 23 mA per string. DC-DC Efficiency is defined as  $P_{OUT}/P_{IN}$ , where  $P_{OUT}$  is total output power measured from boost output(s). LED Drive Efficiency is defined as  $P_{LED}/P_{IN}$ , where  $P_{LED}$  is actual power consumed in LEDs.

## **Typical Characteristics (continued)**

Measured at room temperature unless otherwise noted. Maximum LED current set to 23 mA per string. DC-DC Efficiency is defined as  $P_{OUT}/P_{IN}$ , where  $P_{OUT}$  is total output power measured from boost output(s). LED Drive Efficiency is defined as  $P_{LED}/P_{IN}$ , where  $P_{LED}$  is actual power consumed in LEDs.

## **Typical Characteristics (continued)**

Measured at room temperature unless otherwise noted. Maximum LED current set to 23 mA per string. DC-DC Efficiency is defined as  $P_{OUT}/P_{IN}$ , where  $P_{OUT}$  is total output power measured from boost output(s). LED Drive Efficiency is defined as  $P_{LED}/P_{IN}$ , where  $P_{LED}$  is actual power consumed in LEDs.

## 8 Detailed Description

#### 8.1 Overview

www.ti.com

The LP8555 is a white LED driver featuring an asynchronous boost converter and 12 high-precision current sinks that can be controlled by a PWM input signal, an I<sup>2</sup>C master, or both. The boost converter uses adaptive output voltage control for setting the optimal LED driver voltages as high as 28 V. This feature minimizes the power consumption by adjusting the voltage to the lowest sufficient level under all conditions. The converter can operate at two switching frequencies: 500 and 1000 kHz pre-configured via EPROM.

Proprietary Hybrid PWM and Current Dimming mode allows higher system power saving. In addition, phase-shifted LED PWM dimming allows reduced audible noise and smaller boost output capacitors.

The LP8555 has a full set of safety features that ensure robust operation of the device and external components. The set consists of input undervoltage lockout, thermal shutdown, overcurrent protection, four levels of overvoltage protection, and LED open and short detection.

#### 8.2 Functional Block Diagram

Copyright © 2014, Texas Instruments Incorporated

#### 8.3 Features Description

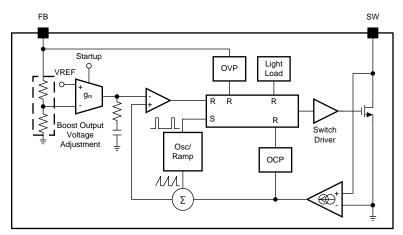

#### 8.3.1 Boost Converter Overview

#### 8.3.1.1 Operation

The boost DC/DC converters generate 7-V to 28-V boost output voltage from a 2.7-V to 20-V boost input voltage (input voltage must be lower than  $V_{BOOST}$ ). The maximum boost output voltage can be set digitally by preconfiguring EPROM memory (VMAX field).

The converter is a magnetic switching PWM mode DC/DC boost converter with a current limit. It uses CPM (current programmed mode) control, where the inductor current is measured and controlled with the feedback. During start-up, the soft-start function reduces the peak inductor current. Figure 20 shows the boost block diagram.

Figure 20. Boost Converter Functional Block Diagram

Both boost converters are operating at 180° phase shift to reduce current spikes from the input rail and EMI.

#### 8.3.1.2 Protection

Three different protection schemes are implemented:

- 1. Overvoltage protection, limits the maximum output voltage:

- Overvoltage protection limit changes dynamically based on output voltage setting. If the boost voltage is over 1.6 V higher than the adaptive control set value, the boost will stop switching.

- Keeps the output below breakdown voltage. The output voltage control limits the boost maximum voltage to 18...28 V (EPROM programmable).

- Prevents boost operation if battery voltage is much higher than desired output.

- 2. Overcurrent protection, limits the maximum inductor current to 3.1 A (EPROM programmable).

- 3. Duty cycle limiting.

### 8.3.1.3 Setting Boost Switching Frequency

The LP8555 boost converter switching frequency can be set by pre-configuring EPROM memory with the choice of boost frequency (BFREQ field). Table 1 summarizes setting of the switching frequency.

**Table 1. Setting Boost Switching Frequency**

| BFREQ | f <sub>SW</sub> [kHz] |

|-------|-----------------------|

| 0     | 500                   |

| 1     | 1000                  |

#### 8.3.1.4 Adaptive Boost Output Voltage Control

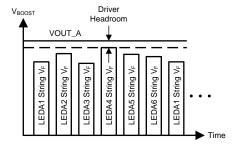

The boost converters operate in adaptive voltage control mode in typical application. The voltages at the LED terminals is monitored by the control loop. It raises the boost voltage when the measured voltage of ANY of the LED strings in a bank falls below the voltage threshold of its corresponding LOW comparator. If the headrooms of ALL of the LED strings in a bank are above the voltage threshold of their corresponding MID comparator, then the boost voltage is lowered. Both banks have independent boost voltage control to save power in case of Vf mismatch between LED strings.

The initial boost voltage is configured with the VINIT field. The VMAX field sets the maximum boost voltage. When an LED terminal is open, the monitored voltage will never have enough headroom and the adaptive mode control loop will keep raising the boost voltage. The VMAX field allows the boost voltage to be limited to stay under the voltage rating of the external components.

Figure 21. Boost Adaptive Control Principle for Bank A Boost Converter With Phase Shifted Outputs

#### 8.3.1.5 EMI Reduction

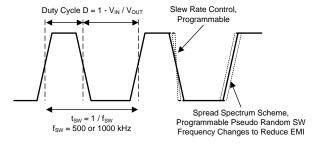

The LP8555 features three EMI reduction schemes.

First scheme, Programmable Slew Rate Control, uses a combination of four drivers for boost switch. Enabling all four drivers allows boost switch on/off transition times to be the shortest. On the other hand, enabling just one driver allows boost switch on/off transition times to be the longest. The longer the transition times, the lower the switching noise on the SW node. It should also be noted that the shortest transition times bring the best efficiency as the switching losses are the lowest. Same controls effect both boost converters.

The second EMI reduction scheme is the Spread Spectrum Scheme which deliberately spreads the frequency content of the boost switching waveform, which inherently has a narrow bandwidth, makes the switching waveform's noise spectrum bandwidth wider and ultimately reduces its EMI spectral density.

The third feature for reducing EMI is Phase Shifted Clocking mode, where boost converters' clocks are operating 180° phase shifted. This prevents boost switches switching on at the same time when operating in PWM mode. This reduces input rail load transient spikes caused by boost inductor current and gate driver currents.

Figure 22. Boost Converter EMI Reduction Schemes

SNVS857 – FEBRUARY 2014 www.ti.com

# TEXAS INSTRUMENTS

#### 8.3.2 Brightness Control

The brightness can be controlled using an external PWM signal or the Brightness registers accessible via an I<sup>2</sup>C interface, or both. Which of these two input sources are selected is set by the BRTMODE EPROM bits. How the brightness is controlled in each of the four possible modes is described in the following sections.

#### 8.3.2.1 PWM Input Duty Measurement

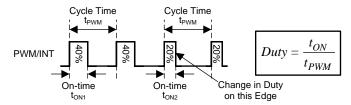

When using PWM input for brightness control the input PWM duty cycle is measured as described in following diagram and the brightness is controlled based on the result. When changing the brightness it must be noted that the measurement cycle is from rising edge to next rising edge and brightness change must be done accordingly (time from rising to rising edge is constant (=cycle time) and falling edge defines the brightness).

Figure 23. PWM Input Duty Cycle Measurement

#### 8.3.2.2 BRTMODE = 00

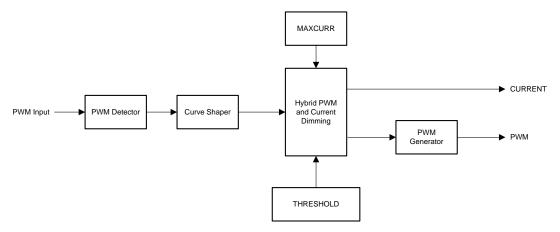

With BRTMODE = 00, the LED output current is controlled by the PWM input duty cycle. The PWM detector block measures the duty cycle at the PWM/INT terminal and uses it to generate a PWM-based brightness code. Before the output is generated, the code goes through the curve Shaper block. Then the code goes into the Hybrid PWM and Current Dimming block which determines the range of the PWM and Current control. The outcome of the Hybrid PWM and Current Dimming block is Current and/or up to 6 PWM output signals.

Figure 24. BRTMODE = 00 Brightness Control

Submit Documentation Feedback

#### 8.3.2.3 BRTMODE = 01

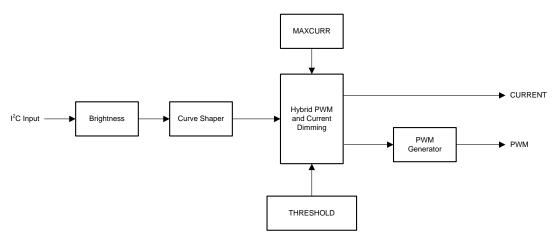

With BRTMODE = 01, the LED output current is controlled by the BRTHI/BRTLO registers. Before the output is generated the BRTHI/BRTLO registers-based brightness code goes through the Curve Shaper block. Then the code goes into the Hybrid PWM and Current Dimming block which determines the range of the PWM and Current control. The outcome of the Hybrid PWM and Current Dimming block is Current and/or up to 6 PWM output signals.

Figure 25. BRTMODE = 01 Brightness Control

#### 8.3.2.4 BRTMODE = 10

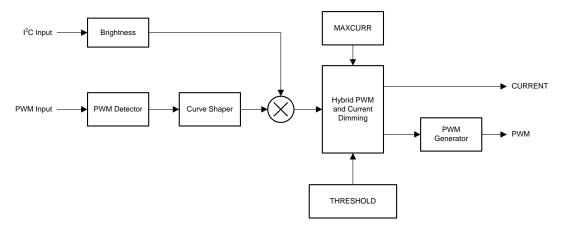

With BRTMODE = 10, the LED output current is controlled by PWM input duty cycle and the BRTHI/BRTLO registers. The PWM detector block measures the duty cycle at the PWM/INT terminal and uses it to generate PWM-based brightness code. Before the code is multiplied with the BRTHI/BRTLO registers-based brightness code, it goes through the Curve Shaper block. After the multiplication, the resulting code goes into the Hybrid PWM and Current Dimming block which determines the range of the PWM and Current control. The outcome of the Hybrid PWM and Current Dimming block is Current and/or up to 6 PWM output signals.

Figure 26. BRTMODE = 10 Brightness Control

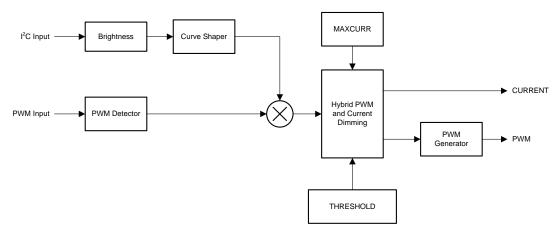

#### 8.3.2.5 BRTMODE = 11

With BRTMODE = 11, the LED output current is controlled by the PWM input duty cycle and the BRTHI/BRTLO registers. The PWM detector block measures the duty cycle at the PWM/INT terminal and uses it to generate PWM-based brightness code. In this mode, the BRTHI/BRTLO registers-based brightness code goes through the Curve Shaper block before it is multiplied with the PWM input duty cycle-based brightness code. After the multiplication, the resulting code goes into the Hybrid PWM and Current Dimming block which determines the range of the PWM and Current control. The outcome of the Hybrid PWM and Current dimming block is Current and/or up to 6 PWM output signals.

Figure 27. BRTMODE = 11 Brightness Control

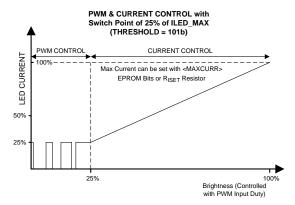

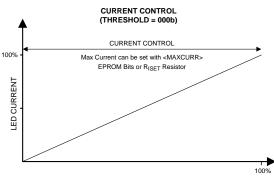

### 8.3.2.6 Hybrid PWM and Current Dimming Control

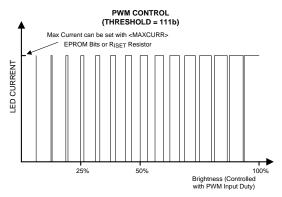

Hybrid PWM and Current Dimming control combines PWM dimming and LED current-dimming control methods. With this dimming control, it is possible to achieve better optical efficiency from the LEDs compared to pure PWM control while still achieving smooth and accurate control and low brightness levels. The switch point from current-to-PWM control is set with THRESHOLD EPROM field, available settings are Pure PWM dimming (THRESHOLD = 111b), 25% switch point (THRESHOLD = 101b) and Pure Current Dimming (THRESHOLD = 000b). 25% setting allows good compromise between good matching of the LEDs brightness/white point at low brightness and good optical efficiency.

Figure 28.

Figure 29.

Figure 30.

Copyright © 2014. Texas Instruments Incorporated Submit Documentation Feedback

SNVS857 – FEBRUARY 2014 www.ti.com

# TEXAS INSTRUMENTS

### 8.3.2.7 Setting PWM Dimming Frequency

The LP8555 LED PWM dimming frequency can be set either by an external resistor (PFSET = 1 selection),  $R_{FSET}$ , or by pre-configuring EPROM memory with the choice of PWM dimming frequency (PFREQ field). Table 2 summarizes setting of the PWM dimming frequency. Setting the PWM dimming frequency using an external resistor is separately shown in Table 3.

**Table 2. Setting PWM Dimming Frequency**

| PFSET | R <sub>FSET</sub> | PFREQ      | f <sub>PWM</sub> [kHz] |

|-------|-------------------|------------|------------------------|

| 1     | See Table 3       | Don't Care | See Table 3            |

| 0     | Don't Care        | 000        | 4.9                    |

| 0     | Don't Care        | 001        | 9.8                    |

| 0     | Don't Care        | 011        | 19.5                   |

| 0     | Don't Care        | 111        | 39.1                   |

Table 3. Setting PWM Dimming Frequency With an External Resistor

| PFSET | R <sub>FSET</sub> [Ω] (Tolerance) | f <sub>PWM</sub> [kHz] |

|-------|-----------------------------------|------------------------|

| 1     | 63.4k (±1%)                       | 4.9                    |

| 1     | 52.3k, 53.6k (±1%)                | 9.8                    |

| 1     | 39.2k (±1%)                       | 19.5                   |

| 1     | 23.2k (±1%)                       | 39.1                   |

| 1     | Grounded or floating              | 19.5                   |

### 8.3.2.8 Setting Full-Scale LED Current

The LP8555 full-scale LED current can be set either by an external resistor  $R_{ISET}$  (ISET = 1 selection), or by preconfiguring EPROM memory with the choice of full-scale LED current (MAXCURR field, ISET = 0). This register can be also written with  $I^2C$  before turning on backlight. Table 4 summarizes setting of the full-scale LED current.

**Table 4. Setting Full-Scale LED Current**

| ISET | R <sub>ISET</sub> [Ω] (Tolerance) | MAXCURR    | ILED [mA] |

|------|-----------------------------------|------------|-----------|

| 1    | Floating                          | Don't Care | 23        |

| 1    | 63.4k (±1%)                       | Don't Care | 5         |

| 1    | 52.3k, 53.6k (±1%)                | Don't Care | 10        |

| 1    | 44.2k, 45.3k (±1%)                | Don't Care | 15        |

| 1    | 39.2k (±1%)                       | Don't Care | 20        |

| 1    | 34.0k (±1%)                       | Don't Care | 23        |

| 1    | 30.1k (±1%)                       | Don't Care | 25        |

| 1    | 26.1k (±1%)                       | Don't Care | 30        |

| 1    | 23.2k (±1%)                       | Don't Care | 50        |

| 1    | 0 (grounded)                      | Don't Care | 23        |

| 0    | Don't Care                        | 000        | 5         |

| 0    | Don't Care                        | 001        | 10        |

| 0    | Don't Care                        | 010        | 15        |

| 0    | Don't Care                        | 011        | 20        |

| 0    | Don't Care                        | 100        | 23        |

| 0    | Don't Care                        | 101        | 25        |

| 0    | Don't Care                        | 110        | 30        |

| 0    | Don't Care                        | 111        | 50        |

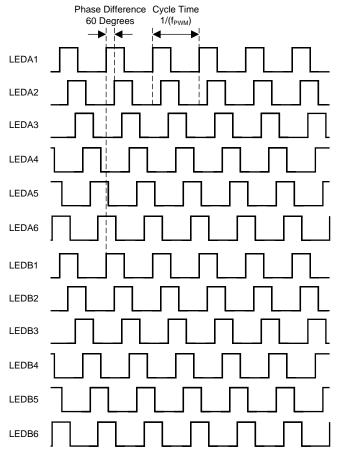

#### 8.3.2.9 Phase-Shift PWM Scheme

The Phase-Shift PWM Scheme (PSPWM) allows delaying of the time when each LED current sink is active. When the LED current sinks are not activated simultaneously, the peak load current from the boost output is greatly decreased during PWM dimming. This reduces the ripple seen on the boost output and allows smaller output capacitors to be used. Reduced ripple also reduces the output ceramic capacitor audible ringing. The PSPWM scheme also increases the load frequency seen on the boost output by up to six times and therefore transfers the possible audible noise to the frequencies outside of the audible range.

The phase difference between each active driver is automatically determined and is 360° / number of active drivers in a bank.

Figure 31. Phase Shifting Example With All 12 Channels Active. (Note: Bank A And Bank B are in the Same Phase.)

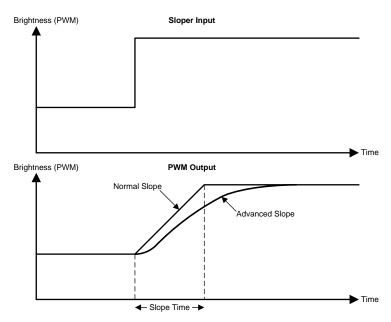

### 8.3.3 LED Brightness Slopes, Normal and Advanced

The transition time between two brightness values can be programmed with the STEP EPROM field from 0 to 200 ms. The same slope time is used for sloping up and down. With advanced slope the brightness changes can be made more pleasing to the human eye. It is implemented with a digital smoothing filter. The filter strength is set with SMOOTH EPROM field.

20

Figure 32. Sloping Principle

#### 8.3.4 Start-up and Shutdown Sequences

Depending on brightness control mode the LP8555 can be started up or shut down differently. Below are explained typical start-up/shutdown sequences with corresponding timings for operation states. Diagrams have more details and illustrated waveforms for typical usage cases.

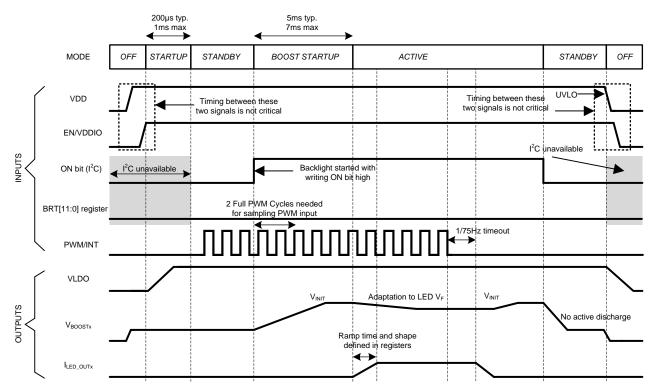

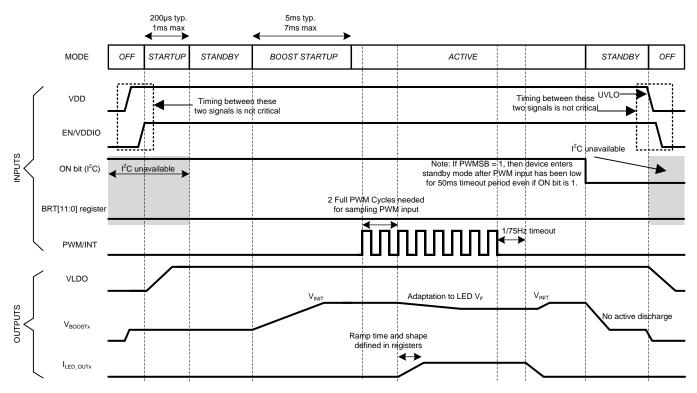

#### 8.3.4.1 Start-up With PWM Input Brightness Control Mode (BRTMODE = 00b)

When VDD and EN/VDDIO are above min operational value the LP8555 enters start-up mode. During start-up mode the LDO is started, and EPROM values are read. I<sup>2</sup>C is available after the start-up sequence has ended.

In standby mode the device waits for the ON bit to go high to start the boost start-up sequence. In standby mode PWM input duty cycle measurement is active.

Once the ON bit is set to 1 (it can be also programmed to 1 by default in EPROM, and no I<sup>2</sup>C write is then needed for entering active mode), boost is started, and device enters active mode with brightness set by PWM input duty cycle. If no brightness is set, the backlight stays off until two PWM pulses are received in the PWM input, or if PWM input is set high for more than 1/75 Hz time. Boost starts initially to the level programmed in EPROM, and after backlight is turned on the adaptive control adjusts the voltage to get to the minimal headroom voltage.

#### 8.3.4.2 Shutdown With PWM Input Brightness Control Mode (BRTMODE = 00b)

The backlight can be turned off by setting PWM input low or by writing the ON bit low. After a 1/75Hz timeout period in the PWM input, the backlight slopes down (if slope is enabled), and boost is returned to the initial voltage level programmed to the EPROM. If the backlight is shut down with the ON bit, it shuts down immediately even if slopes are enabled and boost turns off as well. To enter standby mode where boost is disabled and the power consumption is minimal, the ON bit must be written to 0. If PWMSB bit has been programmed to 1, then the LP8555 enters standby mode when PWM input has been low for more than 50 ms even if the ON bit is high.

The device shuts down completely by setting EN/VDDIO and/or VDD to low state.

Copyright © 2014, Texas Instruments Incorporated

Figure 33. Start-up and Shutdown with PWM Input Control, ON Bit = 0 (BRTMODE = 00b)

Figure 34. Start-up and Shutdown with PWM Input Control, ON Bit = 1 (BRTMODE = 00b)

Submit Documentation Feedback

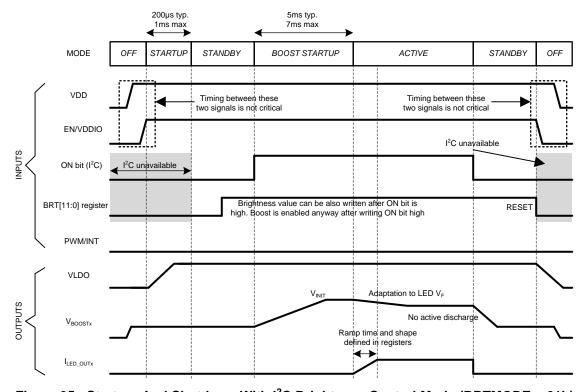

### 8.3.4.3 Start-up With $\hat{F}$ C Brightness Control Mode (BRTMODE = 01b)

When VDD and EN/VDDIO are above min operational value, the LP8555 enters start-up mode. During start-up mode the LDO is started, and EPROM values are read. I<sup>2</sup>C is available after the start-up sequence has ended.

In standby mode the device waits for the ON bit to go high to start the boost start-up sequence. In standby mode  $I^2C$  is active, and brightness / other registers can be written.

Once the ON bit is set to 1 (it can be also programmed to 1 by default in EPROM and no I<sup>2</sup>C write is then needed for entering active mode), boost is started, and device enters active mode with brightness set by I<sup>2</sup>C brightness registers. If no brightness is set, the backlight stays off until brightness value is written to the I<sup>2</sup>C register(s). Boost starts initially to the level programmed in EPROM and, after backlight is turned on, the adaptive control adjusts the voltage to get to the minimal headroom voltage.

#### 8.3.4.4 Shutdown With $^{\rho}$ C Brightness Control Mode (BRTMODE = 01b)

The backlight can be turned off by setting the ON bit low, or by writing brightness to 0. The backlight shuts down immediately if the ON bit is written low even if slope is enabled. If the backlight is turned off by writing brightness to 0, brightness control does slope (if enabled), and the boost is returned to the initial voltage level programmed to EPROM. To enter standby mode where boost is disabled and the power consumption is minimal, the ON bit must be written to 0.

The device shuts down completely by setting EN/VDDIO and/or VDD to low state.

Figure 35. Start-up And Shutdown With I<sup>2</sup>C Brightness Control Mode (BRTMODE = 01b)

Product Folder Links: LP8555

114, Texas instruments incorporated

SNVS857 – FEBRUARY 2014 www.ti.com

# TEXAS INSTRUMENTS

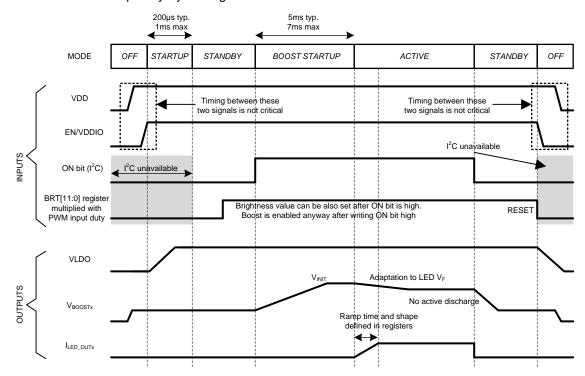

### 8.3.4.5 Start-up with ${}^{\rho}C + PWM$ Input Brightness Control Mode (BRTMODE = 10 or 11b)

When VDD and EN/VDDIO are above min operational value, the LP8555 enters start-up mode. During start-up mode the LDO is started, and EPROM values are read. I<sup>2</sup>C is available after the start-up sequence has ended.

In standby mode the device waits for the ON bit to go high to start the boost start-up sequence. In standby mode I<sup>2</sup>C registers can be written and PWM input duty cycle measurement is active.

Once the ON bit is set to 1 (it can be also programmed to 1 by default in EPROM and no I<sup>2</sup>C write is then needed for entering active mode), boost is started, and device enters active mode with brightness set by PWM input duty cycle multiplied by I<sup>2</sup>C brightness register value. If no brightness is set, the backlight stays off until I<sup>2</sup>C brightness register receives value and two PWM pulses are received in the PWM input, or if PWM input is set high for more than 1/75 Hz time. Boost starts initially to the level programmed in EPROM and after backlight is turned on, the adaptive control adjusts the voltage to get to the minimal headroom voltage.

## 8.3.4.6 Shutdown with $f^2C + PWM$ Input Brightness Control Mode (BRTMODE = 10 or 11b)

The backlight can be turned off by setting the ON bit low, or by setting brightness to 0 either by PWM input (same 1/75 Hz timeout applies here as in PWM input control mode) or by I<sup>2</sup>C brightness register writes. The backlight shuts down immediately if the ON bit is written low even if slope is enabled. If the backlight is turned off by setting brightness to 0, brightness control does slope (if enabled, depending on which input is used – see brightness control modes for details), and the boost is returned to the initial voltage level programmed to EPROM. To enter standby mode where boost is disabled and the power consumption is minimal, the ON bit must be written to 0.

The device shuts down completely by setting EN/VDDIO and/or VDD to low state.

Figure 36. Start-up and Shutdown with I<sup>2</sup>C + PWM Input Brightness Control (BRTMODE = 01b)

24

#### 8.3.5 LED String Count Auto Detection

The LP8555 can be pre-configured to auto-detect the number of the LED strings attached. If the CONFIG.AUTO bit is set to 1, the LP8555 will automatically remove the unused current sink and adjust phasing of the remaining current sinks. The LED OPEN fault condition will not be set in this mode.

#### 8.3.6 Fault Detection

The LP8555 has fault detection for LED OPEN, LED SHORT, UVLO, BST\_OVP, BST\_OCP, BST\_UV and TSD. Faults are recorded in the STATUS register. Each time the STATUS register is read, it is automatically cleared. When BRTMODE is set to 01b any fault may be enabled to cause an interrupt on the PWM/INT terminal.

#### 8.3.6.1 LED Short Detection

Voltages at the individual current sinks are constantly monitored for the LED SHORT fault. This fault may occur when some LEDs in a string are electrically bypassed making that LED string shorter than the other LED strings. The reduced forward voltage causes the current sink attached to that string to have a higher headroom voltage than the other current sinks. When the headroom voltage is higher than the fault comparator threshold (configured with the OV field in the LEDEN register) that current sink is disabled and the PWM phasing is automatically adjusted. The fault comparator threshold may be configured for 1 V, 2 V, 3 V or 4 V.

#### 8.3.6.2 LED Open Detection

Each current sink is also monitored for an LED OPEN condition. The condition is set when the headroom voltage on one or more current sinks is below the LOW comparator threshold and the boost voltage is at the maximum. This fault condition may be caused by one or more OPEN LED strings or by one or more current sinks shorted to GND.

The AUTO bit of the CONFIG register determines how the LP8555 responds to an LED OPEN condition. If the CONFIG.AUTO bit is set to 1, the LP8555 will automatically adjust the phasing to remove the current sink with the LED OPEN condition. In this case the condition is normal and indicates an unpopulated LED string. If the CONFIG.AUTO bit is set to 0, the LP8555 will immediately shut down the backlight whenever an LED OPEN condition is detected on any enabled LED drivers. The backlight will not turn on again (regardless of the COMMAND.ON bit) until the STATUS register is read.

#### 8.3.6.3 Undervoltage Detection

The LP8555 continuously monitors the voltage on the VDD terminal. When the VDD voltage drops below 2.5 V the backlight will be immediately shut down, and the UVLO bit will be set in the STATUS register. The backlight will automatically start again when the voltage has increased above 2.5 V + 50 mV hysteresis. Hysteresis is implemented to avoid continuously triggering undervoltage.

#### 8.3.6.4 Thermal Shutdown

If the internal temperature reaches 150°C, the LP8555 will immediately shut down the backlight to protect it from damage. The TSD bit will also be set in the STATUS register. The device will re-activate the backlight again when the internal temperature drops below 137°C (typ).

#### 8.3.6.5 Boost Overcurrent Protection

The LP8555 will automatically limit boost current to 3.1 A (EPROM programmable). When the 3.1-A limit is reached the BST\_OCP bit is set in the STATUS register.

#### 8.3.6.6 Boost Overvoltage Protection

The LP8555 will automatically limit boost voltage to VBOOST\_MAX+1.6 V. When the limit is reached the BST\_OVP bit is set in the STATUS register. It is possible to set the limit to four threshold levels programmable via EPROM bits.

#### 8.3.6.7 Boost Undervoltage Protection

The LP8555 can detect when the boost voltage is below VBOOST – 2.5 V for longer than 6ms. When the threshold is reached the BST\_UV bit is set in the STATUS register.

#### 8.3.7 I<sup>2</sup>C-Compatible Serial Bus Interface

#### 8.3.7.1 Interface Bus Overview

The I<sup>2</sup>C compatible synchronous serial interface provides access to the programmable functions and registers on the device. This protocol use a two-wire interface for bi-directional communications between the IC's connected to the bus. The two interface lines are the Serial Data Line (FSET/SDA), and the Serial Clock Line (ISET/SCL). These lines should be connected to a positive supply, via a pull-up resistor and remain HIGH even when the bus is idle.

Every device on the bus is assigned a unique address and acts as either a Master or a Slave depending on whether it generates or receives the serial clock (ISET/SCL). The LP8555 is always a slave device.

See the LP8555EVM User Guide for full register map details and programming considerations.

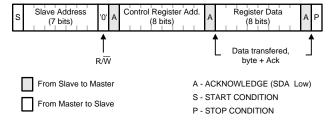

#### 8.3.7.2 Data Transactions

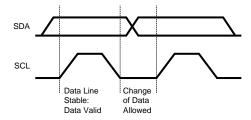

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol permits a single data line to transfer both command/control information and data using the synchronous serial clock.

Figure 37. Bit Transfer

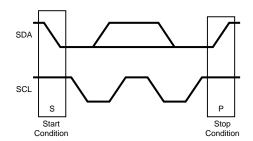

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow. The following sections provide further details of this process.

Figure 38. Start And Stop

The Master device on the bus always generates the Start and Stop Conditions (control codes). After a Start Condition is generated, the bus is considered busy and it retains this status until a certain time after a Stop Condition is generated. A high-to-low transition of the data line (SDA) while the clock (SCL) is high indicates a Start Condition. A low-to-high transition of the SDA line while the SCL is high indicates a Stop Condition.

26

Figure 39. Start And Stop Conditions

In addition to the first Start Condition, a repeated Start Condition can be generated in the middle of a transaction. This allows another device to be accessed, or a register read cycle.

## 8.3.7.3 Acknowledge Cycle

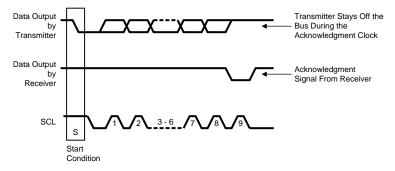

The Acknowledge Cycle consists of two signals: the acknowledge clock pulse the master sends with each byte transferred, and the acknowledge signal sent by the receiving device.

The master generates the acknowledge clock pulse on the ninth clock pulse of the byte transfer. The transmitter releases the SDA line (permits it to go high) to allow the receiver to send the acknowledge signal. The receiver must pull down the SDA line during the acknowledge clock pulse and ensure that SDA remains low during the high period of the clock pulse, thus signaling the correct reception of the last data byte and its readiness to receive the next byte.

#### 8.3.7.4 "Acknowledge After Every Byte" Rule

The master generates an acknowledge clock pulse after each byte transfer. The receiver sends an acknowledge signal after every byte received.

There is one exception to the "acknowledge after every byte" rule. When the master is the receiver, it must indicate to the transmitter an end of data by not-acknowledging ("negative acknowledge") the last byte clocked out of the slave. This "negative acknowledge" still includes the acknowledge clock pulse (generated by the master), but the SDA line is not pulled down.

#### 8.3.7.5 Addressing Transfer Formats

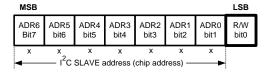

Each device on the bus has a unique slave address. The LP8555 operates as a slave device with 7-bit address combined with data direction bit. Slave address is 2Ch as 7-bit or 58h for write, and 59h for read in an 8-bit format.

Before any data is transmitted, the master transmits the address of the slave being addressed. The slave device should send an acknowledge signal on the SDA line, once it recognizes its address. The slave address is the first seven bits after a Start Condition. The direction of the data transfer (R/W) depends on the bit sent after the slave address — the eighth bit.

When the slave address is sent, each device in the system compares this slave address with its own. If there is a match, the device considers itself addressed and sends an acknowledge signal. Depending upon the state of the R/W bit (1:read, 0:write), the device acts as a transmitter or a receiver.

Figure 40. I<sup>2</sup>C Slave Address

SNVS857 – FEBRUARY 2014 www.ti.com

# TEXAS INSTRUMENTS

#### 8.3.7.6 Control Register Write Cycle

- · Master device generates start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master sends data byte to be written to the addressed register.

- Slave sends acknowledge signal.

- If master will send further data bytes, the control register address will be incremented by one after acknowledge signal.

- Write cycle ends when the master creates stop condition.

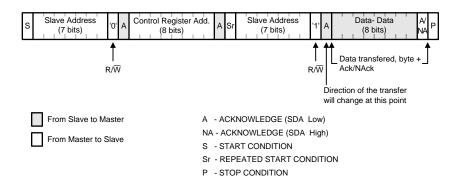

### 8.3.7.7 Control Register Read Cycle

- · Master device generates a start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- · Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master device generates repeated start condition.

- Master sends the slave address (7 bits) and the data direction bit (r/w = 1).

- Slave sends acknowledge signal if the slave address is correct.

- · Slave sends data byte from addressed register.

- If the master device sends acknowledge signal, the control register address will be incremented by one. Slave device sends data byte from addressed register.

- Read cycle ends when the master does not generate acknowledge signal after data byte and generates stop condition.

|            | ADDRESS MODE                                                                          |

|------------|---------------------------------------------------------------------------------------|

| Data Read  | <pre> <start condition=""> <slave address=""><r w="0">[Ack]</r></slave></start></pre> |

| Data Write | <pre> <start condition=""> <slave address=""><r w="0">[Ack]</r></slave></start></pre> |

<> Data from master; [ ] Data from slave.

Figure 41. Register Write Format

28

Figure 42. Register Read Format

#### 8.4 Device Functional Modes

### 8.4.1 Operation Without I<sup>2</sup>C Control

The device can operate without I<sup>2</sup>C control in applications where I<sup>2</sup>C bus is not available. Special EPROM configuration is needed for this setup. In this mode the EN/VDDIO terminal enables the device, and PWM input duty cycle adjusts the brightness. Slopes, PSPWM modes, different boost modes etc. are predefined in the EPROM which device loads at start-up. FSET/SDA and ISET/SCL terminals can be used to set the PWM frequency and LED current based on specific needs (see corresponding sections for setting the frequency and current), without needing separate EPROM configuration for each application. The backlight start-up happens when EN/VDDIO terminal is high and PWM input receives measurable duty cycle. If the PWMSB bit is set 1 in EPROM, the device enters standby mode automatically when PWM/INT is set low. If PWMSB is 0, the device is shut down setting EN/VDDIO low. See start-up and shutdown diagrams for more details.

### 8.4.2 Operation With I<sup>2</sup>C Control

With I<sup>2</sup>C control, user may set the device configuration more freely and have additional I<sup>2</sup>C brightness control. The backlight brightness can be controlled with either PWM input, with I<sup>2</sup>C, or a combination of both. Configuration for slopes, PSPWM, or different boost modes can be used from EPROM defaults, or user can set own configuration before backlight is turned on. Configuration setting is done when EN/VDDIO is high (I<sup>2</sup>C is active) and the ON bit is low. R<sub>FSET</sub> and R<sub>ISET</sub> resistors cannot be used in I<sup>2</sup>C control mode, because they are multiplexed as the I<sup>2</sup>C bus terminals (SDA/SCL). The backlight is started by setting the ON bit high, and shutdown is done by setting ON bit low. See start-up and shutdown diagrams for more details. Details of the I<sup>2</sup>C registers and programming considerations are seen in the LP8555EVM User Guide.

#### 8.4.3 Shutdown Mode

The device is in shutdown mode when the EN/VDDIO terminal is low. the EN/VDDIO terminal enables an LDO, which is used for powering internal logic and analog blocks. Current consumption in this mode from VDD terminal is  $<1 \mu$ A.

#### 8.4.4 Standby Mode

In standby mode the EN/VDDIO terminal is set high (with VDD power present), and logic is powered from an LDO. The device goes through the start-up sequence where NVM (EPROM) is loaded to the registers.  $I^2C$  is available in standby mode, and register settings can be changed. Current consumption is < 30  $\mu$ A in this mode from VDD terminal.

#### 8.4.5 Active Mode

In active mode the backlight is enabled either with setting the ON register bit high (I<sup>2</sup>C control mode) or by activating PWM input. The EN/VDDIO terminal must be high, and VDD must be present. Brightness is controlled with I<sup>2</sup>C writes to brightness registers or by changing PWM input duty cycle (operation without I<sup>2</sup>C control). Configuration registers are not accessible in Active mode to prevent damage to the device by accidental writes. Current consumption from VDD terminal in this mode is typically 4.2 mA when LEDs are not drawing any current.

# 8.5 Register Maps

| Register  | Addr | D7                | D6      | D5              | D4        | D3      | D2      | D1       | D0    |

|-----------|------|-------------------|---------|-----------------|-----------|---------|---------|----------|-------|

| COMMAND   | 00h  | RESET             |         |                 |           |         | SREN    | SSEN     | ON    |

| STATUS    | 01h  | LED_OPEN          | LED_OV  |                 | BST_UV    | BST_OVP | BST_OCP | TSD      | UVLO  |

| MASK      | 02h  | LED_OPEN          | LED_OV  |                 | BST_UV    | BST_OVP | BST_OCP | TSD      | UVLO  |

| BRTLO     | 03h  |                   | BF      | RT[3:0]         |           |         |         |          |       |

| BRTHI     | 04h  |                   |         |                 | BRT[11:4] |         |         |          |       |

| CONFIG    | 10h  | PWMSB             | PWMFILT | EN_BPHASE180    |           | RELOAD  | AUTO    | BRTM     | ODE   |

| CURRENT   | 11h  | ISET              |         |                 |           |         |         | MAXCURR  |       |

| PGEN      | 12h  | PFSET             |         | Т               | HRESHOLD  |         |         | PFREQ    |       |

| BOOST     | 13h  |                   |         |                 |           |         |         | BIND     | BFREQ |

| LEDEN_0   | 14h  |                   | OV      | V ENABLE_0      |           |         |         |          |       |

| STEP      | 15h  | SM                | НТОС    | DTH PWM_IN_HYST |           |         | STEP    |          |       |

| VOLTAGE_0 | 16h  | VM                | AX_0    | X_0 ADAPT_0     |           |         | VINIT_0 |          |       |

| LEDEN_1   | 19h  |                   |         |                 |           | ENABL   | E_1     |          |       |

| VOLTAGE_1 | 1Ah  | VM                | AX_1    | ADAPT_1         |           |         | VINIT_1 |          |       |

| OPTION    | 1Ch  |                   |         | •               |           |         | OPTION  |          |       |

| EXTRA     | 1Dh  |                   |         |                 | EXTRA     |         |         |          |       |

| ID        | 1Eh  |                   | ID_     | CUST            |           |         | ID      | _CFG     |       |

| REVISION  | 1Fh  |                   | M       | AJOR            |           |         | M       | INOR     |       |

| CONF0     | 76h  | BOOST_IS_<br>DIV2 |         | ALTID SRON      |           | RON     | CURR_   | LIMIT    |       |

| CONF1     | 77h  | FMC               | D_DIV   |                 |           |         |         |          |       |

| VHR0      | 78h  |                   |         | VHR_SLOPE       |           |         | _       | VHR_VERT |       |

| VHR1      | 79h  |                   |         | VHR_H           | YST       |         |         | VHR_H    | HORZ  |

| JUMP      | 7Ah  | JEN               |         |                 |           | Jī      | ΓHR     | JVC      | LT    |

Some register fields are loaded from an internal EPROM (shaded above). This EPROM is programmed by TI during final test. This allows default values to be assigned. This feature is intended for applications where the  $I^2C$  interface is not used. With the exception of the ID fields, all EPROM based fields can be written via  $I^2C$  writes like a normal register field. There are limitations on certain configuration bits, their operation and can they be changed "on-the-fly". It is noted in the description of corresponding bit.

#### 8.5.1 COMMAND

Address: 0x00

| D7    | D6 | D5 | D4 | D3 | D2   | D1   | D0 |

|-------|----|----|----|----|------|------|----|

| RESET |    | _  |    |    | SREN | SSEN | ON |

| Bits | Field    | Туре | Description                                                                                                                                       |

|------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|