TPS92391 SNVSBY8 – MARCH 2021

# TPS92391 Boost/SEPIC High Dimming Performance LED Driver with Six 200-mA Channels

# 1 Features

- Input voltage operating range 3 V to 48 V

- Six high-precision current sinks

- Up to 200-mA DC current for each current sink

- Current matching 1% (typical)

- Dimming ratio 32 000:1 using 152-Hz LED output PWM frequency

- Up to 16-bit LED dimming resolution with I2C, or PWM input

- 8 Configurable LED strings configuration

- Auto-phase shift PWM dimming

- 12-bit Analog dimming

- Switching frequency 100 kHz to 2.2 MHz

- · Boost spread spectrum for reduced EMI

- Boost sync input to set boost switching frequency from an external clock

- Up to 48-V V<sub>OUT</sub> boost or SEPIC DC/DC controller

- Switching frequency 100 kHz to 2.2 MHz

- Boost spread spectrum for reduced EMI

- Boost sync input to set boost switching frequency from an external clock

- · Extensive fault diagnostics

# **2** Applications

Backlight for:

- Monitor

- TV

- Medical displays

- Industrial backlighting systems in control panels

- Industrial PC

- · Test and measurement equipment

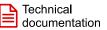

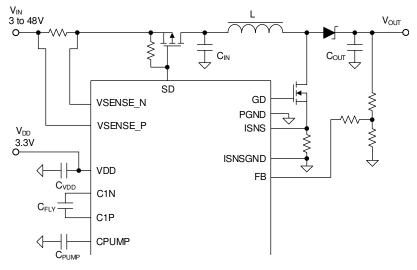

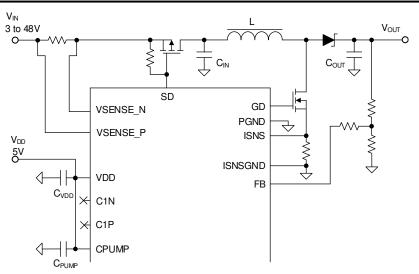

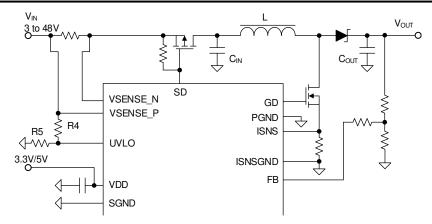

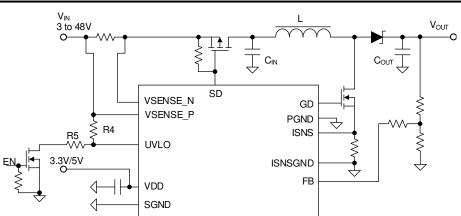

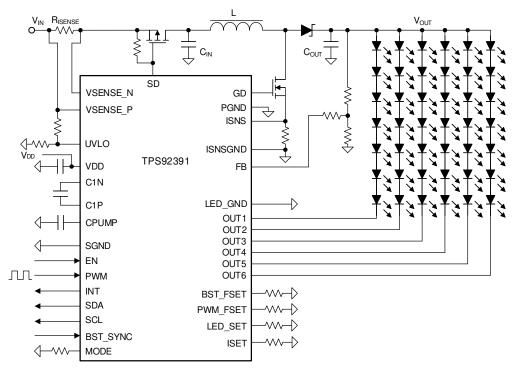

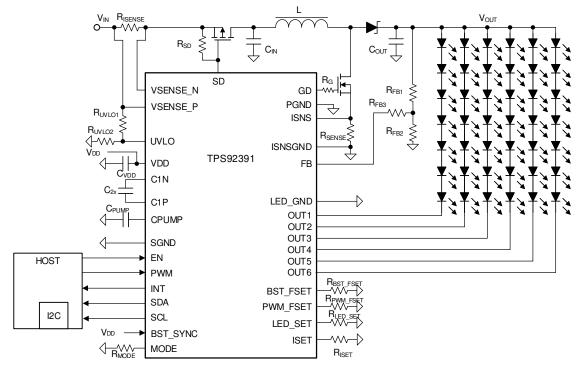

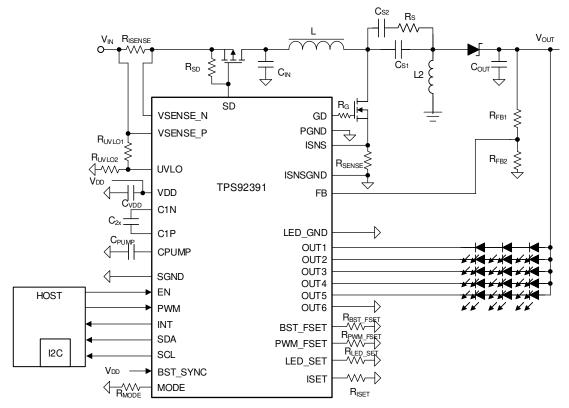

**Simplified Schematic**

# **3 Description**

The TPS92391 is an automotive high-efficiency LED driver with boost controller. The Six high-precision current sinks support phase shifting that is automatically adjusted based on the number of channels in use. LED brightness can be controlled globally through the I<sup>2</sup>C interface or PWM input.

The boost controller has adaptive output voltage control based on the headroom voltages of the LED current sinks. This feature minimizes the power consumption by adjusting the boost voltage to the lowest sufficient level in all conditions. A wide-range adjustable frequency allows the TPS92391 to avoid disturbance for AM radio band.

The TPS92391 supports built-in hybrid PWM dimming and analog current dimming, which reduces EMI, extends the LED lifetime, and increases the total optical efficiency.

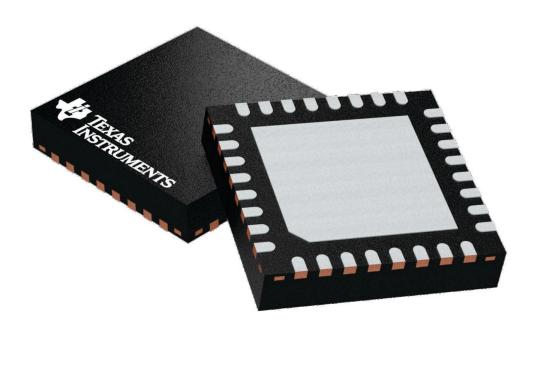

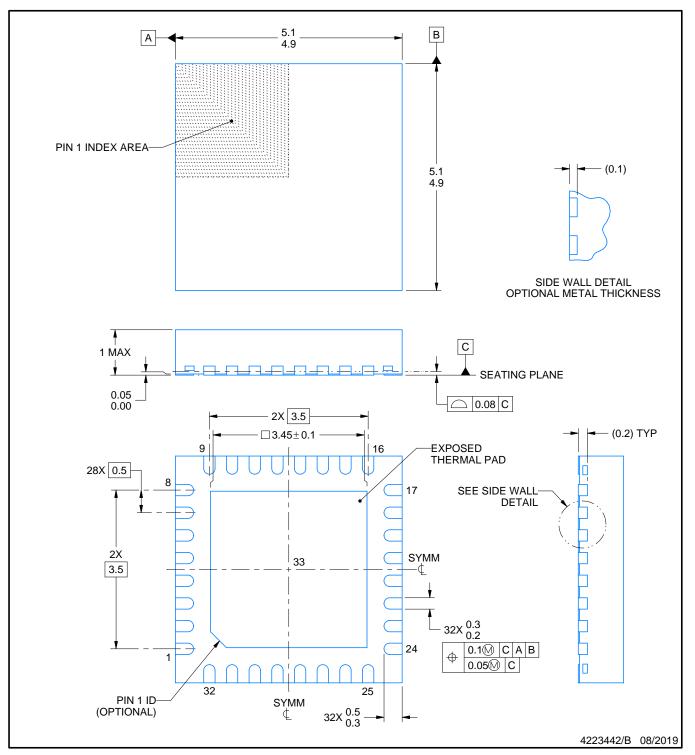

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE  | BODY SIZE (NOM) |

|----------------------------|----------|-----------------|

| TPS92391                   | QFN (32) | 5 mm × 5 mm     |

For all available packages, see the orderable addendum at the end of the data sheet.

# **Table of Contents**

| 1 Features                                | 1  |

|-------------------------------------------|----|

| 2 Applications                            |    |

| 3 Description                             |    |

| 4 Revision History                        |    |

| 5 Pin Configuration and Functions         |    |

| 6 Specifications                          |    |

| 6.1 Absolute Maximum Ratings              |    |

| 6.2 ESD Ratings                           |    |

| 6.3 Recommended Operating Conditions      |    |

| 6.4 Thermal Information                   | 6  |

| 6.5 Electrical Characteristics            | 6  |

| 6.6 Logic Interface Characteristics       | 9  |

| 6.7 Timing Requirements for I2C Interface | 9  |

| 6.8 Typical Characteristics               | 10 |

| 7 Detailed Description                    |    |

| 7.1 Overview                              | 11 |

| 7.2 Functional Block Diagram              | 12 |

| 7.3 Feature Description                   |    |

| 7.4 Device Functional Modes               |    |

|                                           |    |

| 7.5 Programming                                       | 38  |

|-------------------------------------------------------|-----|

| 7.6 Register Maps                                     |     |

| 8 Application and Implementation.                     |     |

| 8.1 Application Information                           |     |

| 8.2 Typical Applications                              |     |

| 9 Power Supply Recommendations                        |     |

| 10 Layout                                             |     |

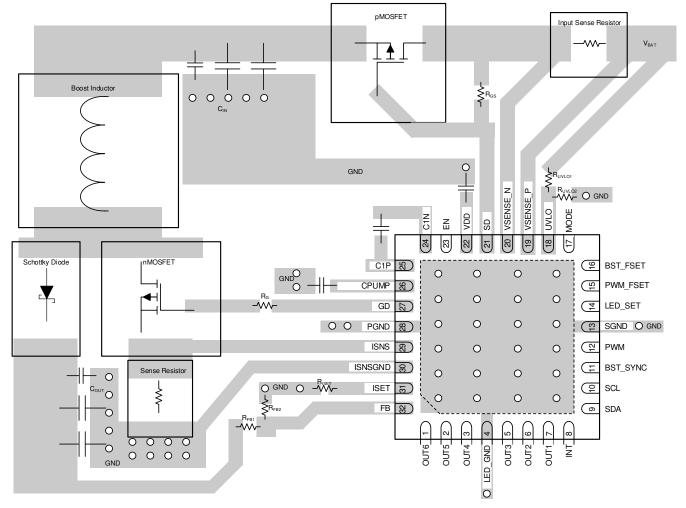

| 10.1 Layout Guidelines                                |     |

| 10.2 Layout Example                                   |     |

| 11 Device and Documentation Support                   | .72 |

| 11.1 Device Support                                   | .72 |

| 11.2 Receiving Notification of Documentation Updates. | .72 |

| 11.3 Support Resources                                | 72  |

| 11.4 Trademarks                                       | 72  |

| 11.5 Electrostatic Discharge Caution                  | .72 |

| 11.6 Glossary                                         | .72 |

| 12 Mechanical, Packaging, and Orderable               |     |

| Information                                           | 73  |

|                                                       |     |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE REVISION |   | NOTES           |

|---------------|---|-----------------|

| March 2021    | * | Initial Release |

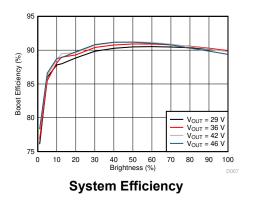

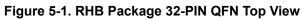

# **5** Pin Configuration and Functions

#### Table 5-1. QFN Pin Functions

| PIN |          |        |                                                                                                                                                             |  |

|-----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME     | TYPE   | DESCRIPTION                                                                                                                                                 |  |

| 1   | OUT6     | Analog | LED current sink output. If unused tie to ground                                                                                                            |  |

| 2   | OUT5     | Analog | LED current sink output. If unused tie to ground                                                                                                            |  |

| 3   | OUT4     | Analog | LED current sink output. If unused tie to ground.                                                                                                           |  |

| 4   | LED_GND  | GND    | LED ground connection.                                                                                                                                      |  |

| 5   | OUT3     | Analog | LED current sink output. If unused tie to ground.                                                                                                           |  |

| 6   | OUT2     | Analog | LED current sink output. If unused tie to ground.                                                                                                           |  |

| 7   | OUT1     | Analog | LED current sink output. If unused tie to ground.                                                                                                           |  |

| 8   | INT      | Analog | Device fault interrupt output, open drain. A 10-k $\Omega$ pullup resistor is recommended.                                                                  |  |

| 9   | SDA      | Analog | SDA for I2C interface. A 10-kΩ pullup resistor is recommended.                                                                                              |  |

| 10  | SCL      | Analog | SCL for I2C interface. A 10-kΩ pullup resistor is recommended.                                                                                              |  |

| 11  | BST_SYNC | Analog | Input for synchronizing boost. When synchronization is not used, connect this pin to ground to disable spread spectrum or to VDD to enable spread spectrum. |  |

| 12  | PWM      | Analog | PWM input for brightness control. Tie to GND if unused.                                                                                                     |  |

| 13  | SGND     | GND    | Signal ground.                                                                                                                                              |  |

| 14  | LED_SET  | Analog | LED string configuration through external resistor. Do not leave floating.                                                                                  |  |

| 15  | PWM_FSET | Analog | LED dimming frequency setup through external resistor. Do not leave floating.                                                                               |  |

| 16  | BST_FSET | Analog | post switching frequency setup through external resistor. Do not leave floating.                                                                            |  |

| 17  | MODE     | Analog | Dimming mode setup through external resistor. Do not leave floating.                                                                                        |  |

| 18  | UVLO     | Analog | Input voltage sense for programming input UVLO threshold through external resistor to VIN.                                                                  |  |

| 19  | VSENSE_P | Analog | Pin for input voltage detection for OVP protection and positive input for input current sense.                                                              |  |

| 20  | VSENSE_N | Analog | Negative input for input current sense. If input current sense is not used, please tie to VSENSE_P pin.                                                     |  |

| 21  | SD       | Analog | Power line FET control. Open Drain output. If unused, leave this pin floating.                                                                              |  |

| 22  | VDD      | Power  | Power supply input for internal analog and digital circuit. Connect a 10-uF capacitor between the VDD pin to GND.                                           |  |

| 23  | EN       | Analog | Enable input.                                                                                                                                               |  |

| 24  | C1N      | Analog | Negative input for charge pump flying capacitor. If feature not used leave this pin floating.                                                               |  |

| 25  | C1P      | Analog | Positive input for charge pump flying capacitor. If feature not used leave this pin floating.                                                               |  |

| 26  | CPUMP    | Power  | Charge pump output pin. Connect to VDD if charge pump is not used. A 4.7-µF decoupling capacitor is recommended on CPUMP pin.                               |  |

| 27  | GD       | Analog | Gate driver output for external N-FET.                                                                                                                      |  |

| 28  | PGND     | GND    | Power ground.                                                                                                                                               |  |

| 29  | ISNS     | Analog | Boost current sense pin.                                                                                                                                    |  |

| 30  | ISNSGND  | GND    | Current sense resistor GND.                                                                                                                                 |  |

| 31  | ISET     | Analog | LED full-scale current setup through external resistor.                                                                                                     |  |

| 32  | FB       | Analog | Boost feedback input.                                                                                                                                       |  |

| DAP | LED_GND  | GND    | LED ground connection.                                                                                                                                      |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1) (2)</sup>

|                 |                                                                                               | MIN  | MAX                   | UNIT |

|-----------------|-----------------------------------------------------------------------------------------------|------|-----------------------|------|

| Voltage on pins | VSENSE_N, SD, UVLO                                                                            | -0.3 | VSENSE<br>_P + 0.3    | V    |

|                 | VSENSE_P, FB , OUT1 to OUT6                                                                   | -0.3 | 52                    | V    |

| Voltage on pins | C1N, C1P, VDD, EN, ISNS, ISNS_GND, INT, MODE, PWM_FSET, BST_FSET, LED_SET, ISET, GD and CPUMP | -0.3 | 6                     | V    |

| Voltage on pins | PWM, BST_SYNC, SDA, SCL                                                                       | -0.3 | VDD +<br>0.3          | V    |

|                 | Continuous power dissipation <sup>(3)</sup>                                                   |      | Internally<br>Limited | W    |

|                 | Ambient temperature, TA <sup>(4)</sup>                                                        | -40  | 125                   |      |

| Thermal         | Junction temperature, TJ <sup>(4)</sup>                                                       | -40  | 150                   | °C   |

|                 | Lead temperature (soldering)                                                                  |      | 260                   | °C   |

|                 | Storage temperature, Tstg                                                                     | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages are with respect to the potential at the GND pins.

- (3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 165^{\circ}C$  (typical) and disengages at  $T_J = 150^{\circ}C$  (typical).

- (4) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{A-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX} = 150^{\circ}$ C), the power dissipation of the device in the application (P), the junction-to-board thermal resistance and the temperature difference between the system board and the ambient ( $\Delta t_{BA}$ ), which is given by the following equation:  $T_{A-MAX} = T_{J-MAX} (\Theta_{JB} \times P) \Delta t_{BA}$

## 6.2 ESD Ratings

|                    |                            |                                      |                                | VALUE | UNIT |

|--------------------|----------------------------|--------------------------------------|--------------------------------|-------|------|

|                    |                            | Human body model (HBM), per AEC Q100 | 0-002 <sup>(1)</sup>           | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged device model (CDM), per AEC  | Corner pins (1, 19, 20 and 38) | ±750  | V    |

|                    |                            | Q100-011                             | Other pins                     | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                    |                                  | MIN | NOM   | MAX | UNIT |

|--------------------|----------------------------------|-----|-------|-----|------|

|                    | VSENSE_P, VSENSE_N, SD, UVLO     | 3   | 12    | 48  |      |

|                    | FB, OUT1 to OUT6                 | 0   |       | 48  |      |

| Voltage on<br>pins | ISNS, ISNSGND                    | 0   |       | 5.5 | V    |

|                    | EN, PWM, INT, SDA, SCL, BST_SYNC | 0   | 3.3   | 5.5 | v    |

|                    | VDD                              | 3   | 3.3/5 | 5.5 |      |

|                    | C1N, C1P, CPUMP,GD               | 0   | 5     | 5.5 |      |

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|         |                                     | MIN | NOM MAX | UNIT |

|---------|-------------------------------------|-----|---------|------|

| Thermal | Ambient temperature, T <sub>A</sub> | -40 | 125     | °C   |

(1) All voltages are with respect to the potential at the GND pins.

#### 6.4 Thermal Information

|                       |                                                       | Device |      |

|-----------------------|-------------------------------------------------------|--------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                         | QFN    | UNIT |

|                       |                                                       | 32-PIN |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance <sup>(2)</sup> | 32.9   |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance             | 19.6   |      |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance                  | 6.8    | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter            | 0.3    | C/VV |

| $\Psi_{JB}$           | Junction-to-board characterization parameter          | 6.8    |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance          | 1.8    |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

## **6.5 Electrical Characteristics**

Limits apply over the full operation temperature range  $-40^{\circ}C \le T_A \le +125^{\circ}C$ , unless otherwise speicified  $V_{IN} = 12 V$ , VDD = 3.3 V

| PARAMETER                    |                                             | TEST CONDITIONS                                                                | MIN  | TYP  | MAX  | UNIT |

|------------------------------|---------------------------------------------|--------------------------------------------------------------------------------|------|------|------|------|

| General E                    | Electrical Characteristics                  |                                                                                |      |      |      |      |

| l <sub>Q</sub>               | Shutdown mode current, VDD pin              | EN = L                                                                         |      | 1    | 5    | μA   |

| l <sub>Q</sub>               | Active mode current, VDD pin <sup>(1)</sup> | FSW = 303 kHz, PWM = H, BOOST-<br>FET IPD25N06S4L-30, Charge Pump<br>Disabled  |      | 15   | 65   | mA   |

| Ι <sub>Q</sub>               | Active mode current, VDD pin <sup>(1)</sup> | FSW = 2200 kHz, PWM = H, BOOST-<br>FET IPD25N06S4L-30, Charge Pump<br>Disabled |      | 40   | 75   | mA   |

| IQ                           | Active mode current, VDD pin <sup>(1)</sup> | FSW = 303 kHz, PWM = H, BOOST-FET<br>IPD25N06S4L-30, Charge Pump Enabled       |      | 20   | 91   | mA   |

| Ι <sub>Q</sub>               | Active mode current, VDD pin <sup>(1)</sup> | FSW = 2200 kHz, PWM = H, BOOST-<br>FET IPD25N06S4L-30, Charge Pump<br>Enabled  |      | 65   | 104  | mA   |

| CPUMP a                      | nd LDO Electrical Characteristics           |                                                                                |      |      |      |      |

| V <sub>CPUMP</sub>           | Voltage accuracy                            | $V_{DD}$ = 3.0 to 3.6 V; $I_{LOAD}$ = 1 to 50 mA                               | 4.8  | 5    | 5.2  | V    |

| f <sub>CP</sub>              | CP switching frequency                      |                                                                                | 387  | 417  | 447  | kHz  |

| V <sub>CPUMP</sub> _<br>uvlo | VCPUMP UVLO threshold                       | V <sub>CPUMP</sub> falling edge                                                | 3.95 | 4.2  | 4.4  | V    |

| V <sub>CPUMP</sub> _<br>uvlo | VCPUMP UVLO threshold                       | V <sub>CPUMP</sub> rising edge                                                 | 4.15 | 4.4  | 4.6  | V    |

| V <sub>CPUMP</sub> _<br>HYS  | VCPUMP UVLO hysteresis                      |                                                                                | 0.1  | 0.2  |      | V    |

| T <sub>START_U</sub><br>P    | Charge pump startup time                    | C <sub>CPUMP</sub> = 10 μF                                                     |      | 1000 | 2000 | μs   |

| Protectio                    | Protection Electrical Characteristics       |                                                                                |      |      |      |      |

| VDD <sub>UVLO</sub><br>_F    | V <sub>DD</sub> UVLO threshold              | V <sub>DD</sub> falling                                                        | 2.68 | 2.8  | 2.92 | V    |

# 6.5 Electrical Characteristics (continued)

Limits apply over the full operation temperature range  $-40^{\circ}C \le T_A \le +125^{\circ}C$ , unless otherwise speicified V<sub>IN</sub> = 12 V, VDD = 3.3 V

|                              | PARAMETER                                    | TEST CONDITIONS                                                    | MIN   | ТҮР   | MAX   | UNIT |

|------------------------------|----------------------------------------------|--------------------------------------------------------------------|-------|-------|-------|------|

| VDD <sub>UVLO</sub><br>_r    | V <sub>DD</sub> UVLO threshold               | V <sub>DD</sub> rising                                             |       |       | 3.0   | V    |

| VDD <sub>UVLO</sub><br>_H    | V <sub>DD</sub> UVLO hysteresis              |                                                                    |       | 0.1   |       | V    |

| VIN <sub>UVLO</sub> _        | UVLO pin threshold                           | V <sub>UVLO</sub> falling                                          | 0.753 | 0.777 | 0.801 | V    |

| I <sub>UVLO</sub>            | UVLO pin bias current                        | $V_{\rm UVLO} = V_{\rm UVLO_{TH}} + 50 v  mV$                      |       | -5    |       | μA   |

| VIN <sub>OVP_T</sub><br>H    | OVP threshold                                | VSENSE_P rising                                                    | 40.8  | 43    | 45.2  | V    |

| VIN <sub>OVP_H</sub><br>ys   | OVP hysteresis                               |                                                                    |       | 1.7   |       | V    |

| VIN <sub>OCP_T</sub><br>H    | Input OCP threshold                          | R <sub>ISENSE</sub> = 20 mΩ                                        | 187   | 220   | 253   | mV   |

| T <sub>SD</sub>              | Thermal shutdown threshold <sup>(1)</sup>    | Temperature rising                                                 | 150   | 165   | 180   | °C   |

| T <sub>SD</sub>              | Thermal shutdown hysteresis <sup>(1)</sup>   |                                                                    |       | 20    |       | °C   |

| I <sub>SD_LEAKA</sub><br>GE  | SD leakage current                           | V <sub>SD</sub> = 48 V                                             |       | 1     |       | μA   |

| I <sub>SD</sub>              | SD pull down current                         | R <sub>SD</sub> = 20 kΩ                                            | 250   | 325   | 400   | μA   |

| V <sub>FB_OVPL</sub>         | FB pin - Boost OVP low threshold             |                                                                    |       | 1.423 |       | V    |

| V <sub>FB_OVPH</sub>         | FB pin - Boost OVP high threshold            |                                                                    |       | 1.76  |       | V    |

| V <sub>FB_UVP</sub>          | FB pin - Boost OCP threshold                 |                                                                    |       | 0.886 |       | V    |

| V <sub>BST_OVP</sub>         | Discharge pin - Boost OVP high threshold     |                                                                    | 48.5  | 50    | 51.8  | V    |

| Input PW                     | M Electrical Characteristics                 |                                                                    |       |       |       |      |

| I <sub>PWM_LEA</sub><br>KAGE | PWM leakage current                          | V <sub>PWM</sub> = 5 V                                             |       | 1     |       | μA   |

| f <sub>PWM_IN</sub>          | PWM input frequency                          |                                                                    | 100   |       | 20000 | Hz   |

| t <sub>PWM_MIN</sub><br>_ON  | PWM input minimum on-time                    | Direct PWM mode                                                    |       |       | 200   | ns   |

| t <sub>PWM_MIN</sub><br>_ON  | PWM input minimum on-time                    | Phase Shift PWM mode, Hybrid mode, Current Dimming mode            |       | 200   | 220   | ns   |

| PWM_IN<br>RES                | PWM input resolution                         | f <sub>PWM_IN</sub> = 100 Hz                                       |       | 16    |       | bit  |

| PWM_IN<br>RES                | PWM input resolution                         | f <sub>PWM_IN</sub> = 20 kHz                                       |       | 10    |       | bit  |

| LED Curr                     | ent Sink and LED PWM Electrical Charac       | teristics                                                          |       |       |       |      |

| LEAKAGE                      | Leakage current on OUTx                      | OUTx = V <sub>OUT</sub> = 45 V, EN= L                              |       | 0.1   | 2.5   | μA   |

| V <sub>ISET</sub>            | ISET voltage                                 |                                                                    | 1.17  | 1.21  | 1.25  | V    |

| I <sub>MAX</sub>             | Maximum LED sink current                     | OUTx                                                               |       | 200   |       | mA   |

| V <sub>ISET_UVL</sub><br>0   | ISET pin undervoltage                        |                                                                    | 0.97  | 1     | 1.03  | V    |

| R <sub>ISET</sub>            | ISET Resistor range                          | I <sub>OUT</sub> = 30 mA to 200 mA                                 | 15.6  |       | 104   | kΩ   |

| I <sub>LED_LIMIT</sub>       | LED current limit when ISET pin short to GND |                                                                    |       | 280   |       | mA   |

| I <sub>ACC</sub>             | LED sink current accuracy                    | R <sub>ISET</sub> = 15.6 kΩ, I <sub>OUT</sub> = 150 mA, PWM = 100% | -4    |       | 4     | %    |

| I <sub>MATCH</sub>           | LED sink current matching                    | R <sub>ISET</sub> = 15.6 kΩ, I <sub>OUT</sub> = 150 mA, PWM = 100% |       | 1     | 3.5   | %    |

# 6.5 Electrical Characteristics (continued)

Limits apply over the full operation temperature range –40°C  $\leq T_A \leq +125$ °C , unless otherwise speicified V<sub>IN</sub> = 12 V, VDD = 3.3 V

|                               | PARAMETER                                         | TEST CONDITIONS                                                                                                      | MIN   | TYP     | MAX   | UNIT |

|-------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|---------|-------|------|

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 3.92 kΩ                                                                                                   | 141   | 152     | 163   |      |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 4.75 kΩ                                                                                                   | 283   | 305     | 327   |      |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 5.76 kΩ                                                                                                   | 567   | 610     | 653   |      |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 7.87 kΩ                                                                                                   | 1135  | 1221    | 1307  | 11-  |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 11 kΩ                                                                                                     | 2270  | 2441    | 2612  | Hz   |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 17.8 kΩ                                                                                                   | 4541  | 4883    | 5225  |      |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 42.4 kΩ                                                                                                   | 9082  | 9766    | 10450 |      |

| f <sub>DIM</sub>              | LED dimming frequency                             | PWM_FSET = 124 kΩ                                                                                                    | 18163 | 19531   | 20899 |      |

| DIM                           | Dimming ratio                                     | f <sub>PWM_OUT</sub> = 152 Hz                                                                                        |       | 32000:1 |       |      |

| DIM                           | Dimming ratio                                     | f <sub>PWM_OUT</sub> = 4.88 kHz                                                                                      |       | 1000:1  |       |      |

| V <sub>HEADRO</sub><br>om     | LED sink headroom                                 |                                                                                                                      |       | 0.7     |       | V    |

| V <sub>HEADRO</sub><br>OM_HYS | LED sink headroom hysteresis                      |                                                                                                                      |       | 0.8     |       | V    |

| V <sub>LEDSHO</sub><br>rt     | LED internal short threshold                      |                                                                                                                      |       | 5.4     |       | V    |

| V <sub>SHORTG</sub><br>ND     | LED short to ground threshold                     |                                                                                                                      |       | 0.24    |       | V    |

| t <sub>PWM_OUT</sub>          | LED output minimum pulse                          |                                                                                                                      |       | 200     |       | ns   |

| Boost Co                      | onverter Electrical Characteristics               |                                                                                                                      |       |         |       |      |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 7.87 kΩ                                                                                                   | 93    | 100     | 107   | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 4.75 kΩ                                                                                                   | 186   | 200     | 214   | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 5.76 kΩ                                                                                                   | 281   | 303     | 325   | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 3.92 kΩ                                                                                                   | 372   | 400     | 428   | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 11 kΩ                                                                                                     | 465   | 500     | 535   | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 17.8 kΩ                                                                                                   | 1690  | 1818    | 1946  | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 42.4 kΩ                                                                                                   | 1860  | 2000    | 2140  | kHz  |

| f <sub>SW</sub>               | Switching Frequency                               | BST_FSET = 124 kΩ                                                                                                    | 2066  | 2222    | 2378  | kHz  |

| VISNS                         | External FET current limit                        | $V_{ISNS}$ threshold, $R_{SENSE}$ = 15 to 50 m $\Omega$                                                              | 180   | 200     | 220   | mV   |

| I <sub>SEL_MAX</sub>          | IDAC maximum current                              | V <sub>DD</sub> = 3.3 V                                                                                              | 36.4  | 38.7    | 40.2  | μA   |

| R <sub>DS_ONH</sub>           | R <sub>DSON</sub> of high-side FET to gate driver | V <sub>GD</sub> /(R <sub>DS_ON</sub> + total resistance to gate<br>input of SW FET) must not be higher than<br>2.5 A |       | 1.4     |       | Ω    |

| R <sub>DS_ONL</sub>           | R <sub>DSON</sub> of low-side FET to gate driver  | V <sub>GD</sub> /(R <sub>DS_ON</sub> + total resistance to gate<br>input of SW FET) must not be higher than<br>2.5 A |       | 0.75    |       | Ω    |

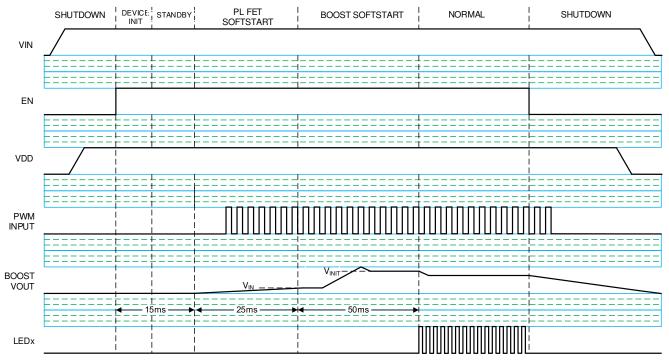

| t <sub>STARTUP</sub>          | Start-up time                                     | Delay from beginning of boost Soft-start to when LED drivers can begin                                               |       | 50      |       | ms   |

| T <sub>ON</sub>               | Minimum switch on-time                            |                                                                                                                      |       | 150     |       | ns   |

| T <sub>OFF</sub>              | Minimum switch off time                           |                                                                                                                      |       | 150     |       | ns   |

(1) This specification is not ensured by ATE

# 6.6 Logic Interface Characteristics

Limits apply over the full operation temperature range  $-40^{\circ}C \le T_A \le +125^{\circ}C$ , unless otherwise speicified,  $V_{IN} = 12 V$ , VDD = 5 V,  $V_{EN} = 3.3 V$

|                      | PARAMETER                            | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |

|----------------------|--------------------------------------|---------------------------------|-----|-----|-----|------|

| LOGIC IN             | IPUT EN                              |                                 |     |     |     |      |

| VENIL                | EN logic low threshold               |                                 |     |     | 0.4 | V    |

| VENIH                | EN logic high threshold              |                                 | 1.2 |     |     | V    |

| R <sub>ENPD</sub>    | EN pin internal pull down resistance |                                 |     | 1   |     | MΩ   |

| LOGIC IN             | IPUT SDA, SCL, BST_SYNC and PWM      |                                 |     |     |     |      |

| V <sub>IL</sub>      | Logic low threshold                  | V <sub>DD</sub> = 3.3 V and 5 V |     |     | 0.4 | V    |

| V <sub>IH</sub>      | Logic high threshold                 | V <sub>DD</sub> = 3.3 V and 5 V | 1.2 |     |     | V    |

| LOGIC O              | UTPUT SDA, INT                       |                                 |     |     |     |      |

| V <sub>OL</sub>      | Output level low                     | I = 3 mA                        |     | 0.2 | 0.4 | V    |

| I <sub>LEAKAGE</sub> | Output leakage current               | V = 3.3 V                       |     |     | 1   | μA   |

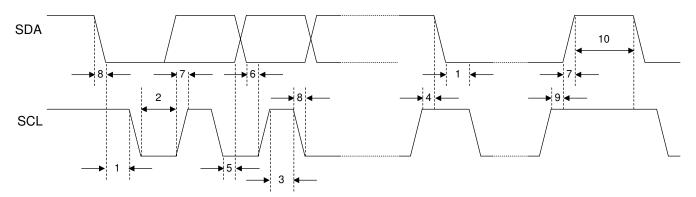

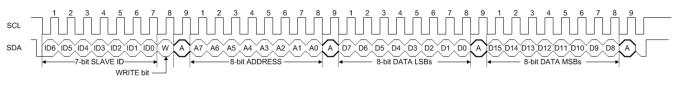

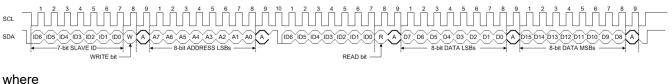

# 6.7 Timing Requirements for I2C Interface

Limits apply over the full operation temperature range  $-40^{\circ}C \le T_A \le +125^{\circ}C$ , unless otherwise speicified V<sub>IN</sub> = 12 V, VDD = 5 V, V<sub>EN</sub> = 3.3 V.

|                   | PARAMETER                                  | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|-------------------|--------------------------------------------|-----------------|-----|---------|------|

| f <sub>SCLK</sub> | Clock frequency                            |                 |     | 400     | kHz  |

| 1                 | Hold time (repeated) START condition       |                 | 0.6 |         | μs   |

| 2                 | Clock low time                             |                 | 1.3 |         | μs   |

| 3                 | Clock high time                            |                 | 600 |         | ns   |

| 4                 | Set-up time for a repeated START condition | n               | 600 |         | ns   |

| 5                 | Data hold time                             |                 | 50  |         | ns   |

| 6                 | Data setup time                            |                 | 100 |         | ns   |

| 7                 | Rise time of SDA and SCL                   |                 |     | 300     | ns   |

| 8                 | Fall time of SDA and SCL                   |                 |     | 300     | ns   |

| 9                 | Set-up time for STOP condition             |                 | 600 |         | ns   |

| 10                | Bus free time between a STOP and a STA     | RT condition    | 1.3 |         | μs   |

Figure 6-1. I2C Timing Diagram

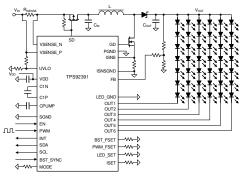

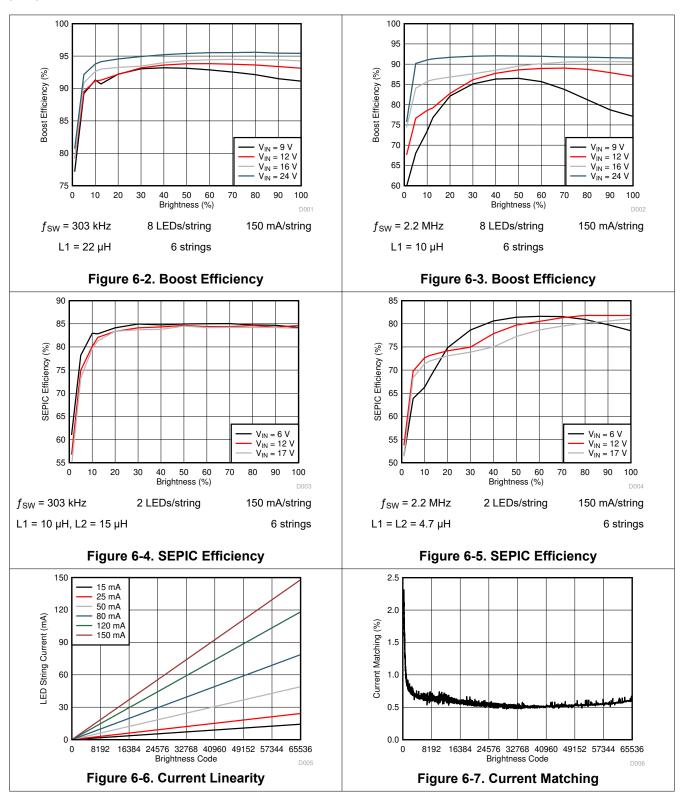

## 6.8 Typical Characteristics

Unless otherwise specified:  $C_{IN} = C_{OUT} = 2 \times 10$ -µF ceramic and  $2 \times 33$ -µF electrolytic,  $V_{DD} = 3.3$  V, charge pump enabled,  $T_A = 25^{\circ}C$

# 7 Detailed Description

## 7.1 Overview

The TPS92391 device is a high-voltage LED driver for large screen display LED backlight applications. PWM input is used for brightness control by default. Alternatively, the brightness can also be controlled by I2C Interface.

The boost frequency, LED PWM frequency, and LED string current are configured with external resistors through the BST\_FSET, PWM\_FSET, and ISET pins. The INT pin is used to report faults to the system. Fault interrupt status can be cleared with the I2C interface, or is cleared on the falling edge of the EN pin.

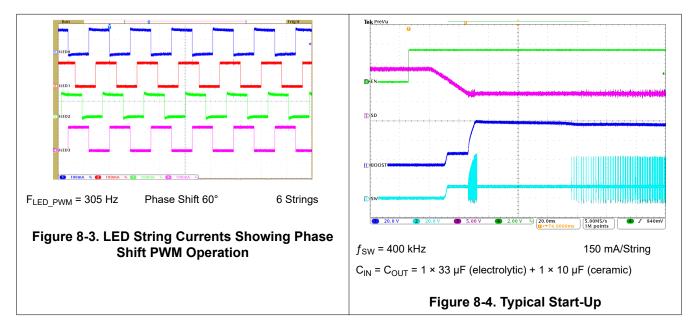

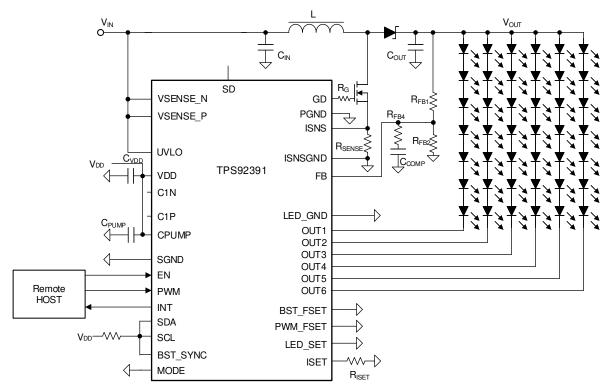

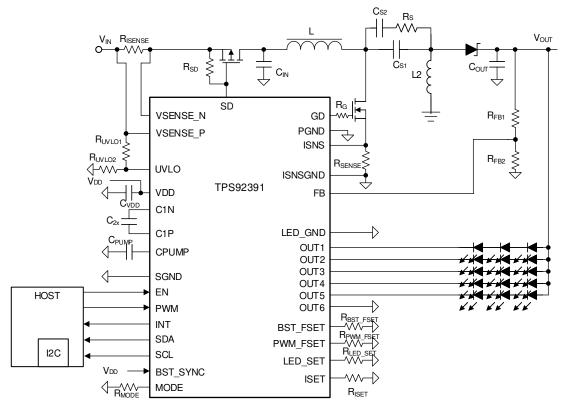

The TPS92391 supports pure PWM dimming. The six LED current drivers provide up to 200 mA per output and can be tied together to support higher current LEDs. The maximum output current of the LED drivers is set with the ISET resistor and can be optionally scaled by the LEDx\_CURRENT[11:0] register bits with I2C interface. The LED output PWM frequency is set with a PWM\_FSET resistor. The number of connected LED strings is configured by the LED\_SET resistor, and the device automatically selects the corresponding phase shift mode. For example, if the device is set to 4-strings mode, each LED output is phase shifted by 90 degrees with each other(= 360 / 4). Unused outputs, which must be connected to GND, will be disabled and excluded from adaptive voltage and won't generate any LED faults.

A resistor divider connected from  $V_{OUT}$  to the FB pin sets the maximum voltage of the boost. For best efficiency, the boost voltage is adapted automatically to the minimum necessary level needed to drive the LED strings by monitoring all the LED output voltages continuously. The switching frequency of the boost regulator can be set between 100 kHz and 2.2 MHz by the BST\_FSET resistor. The boost has a start-up feature that reduces the peak current from the power-line during start-up. The TPS92391 can also control a power-line FET to reduce battery leakage when disabled and provide isolation and protection in the event of a fault.

Fault detection features of TPS92391 include:

- Open-string and shorted LED detection

- LED fault detection prevents system overheating in case of open or short in some of the LED strings

- LED short-to-ground detection

- ISET/BST FSET/PWM FSET/LED SET/MODE resistor out-of-range detection

- Boost overcurrent

- Boost overvoltage

- Device undervoltage protection (VDD UVLO)

- Threshold sensing from VDD pin

- $V_{IN}$  input overvoltage protection ( $V_{IN}$  OVP)

- Threshold sensing from VSENSE\_P pin

- V<sub>IN</sub> input undervoltage protection (V<sub>IN</sub> UVLO)

- Threshold sensing from UVLO pin

- $V_{IN}$  input overcurrent protection ( $V_{IN}$  OCP)

- Threshold sensing across voltage between VSENSE\_P pin and VSENSE\_N pin

- Thermal shutdown in case of die overtemperature

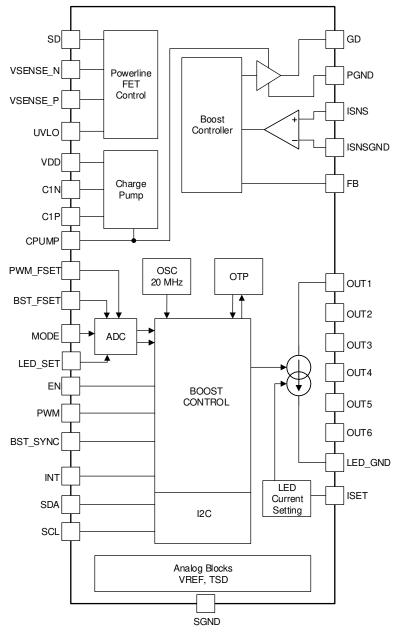

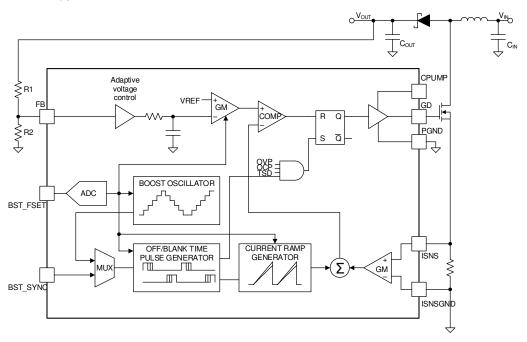

# 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Control Interface

Device control interface includes:

- EN is the enable input for the TPS92391 device.

- PWM is the default input to control the brightness of all current sinks by duty cycle.

- INT is an open-drain fault output indicating fault condition detection.

- SDA and SCL are data and clock line for I2C interface to control the brightness of all current sinks and read back the fault conditions for diagnosis.

- BST\_SYNC is used to input an external clock for the boost switching frequency and control the internal boost clock mode.

- The external clock is auto detected at start-up and, if missing, the internal clock is used.

- Optionally, the BST\_SYNC can be tied to VDD to enable the boost spread spectrum function or tied to GND to disable it.

• ISET pin to set the maximum LED current level per string.

#### 7.3.2 Function Setting

Device parameter setting includes:

- BST\_FSET pin is used to set the boost switching frequency through a resistor to signal ground.

- PWM\_FSET pin is used to set the LED output PWM dimming frequency through a resistor to signal ground.

- MODE pin is used to set the dimming mode via an external resistor to signal ground.

- LED\_SET pin is used to set the LED configuration through a resistor to signal ground.

- ISET pin is used to set the maximum LED current level per OUTx pin.

## 7.3.3 Device Supply (VDD)

All internal analog and digital blocks of TPS92391 are biased from external supply from VDD pin. Either a typical 5-V or 3.3-V supply rail is able to supply VDD from previous linear regulator or DC/DC converter with at least 200-mA current capability.

## 7.3.4 Enable (EN)

The TPS92391 only turns on when the input voltage of EN pin is above the voltage threshold (VEN<sub>IH</sub>) and turns off when the voltage of EN pin is below the threshold (VEN<sub>IL</sub>). All analog and digital blocks start operating once the TPS92391 is enabled by asserting EN pin. The SD pin is floating, I2C interface and Fault detection are not active if the EN pin is de-asserted.

#### 7.3.5 Charge Pump

An integrated regulated charge pump can be used to supply the gate drive for the external FET of the boost controller. The charge pump is enabled or disabled by automatically detecting whether VDD and CPUMP pin are connected together. If VDD is < 4.5 V then use the charge pump to generate a 5-V gate voltage to drive the external boost switching FET. To use the charge pump, a 2.2- $\mu$ F capacitor is placed between C1N and C1P. If the charge pump is not required, C1N and C1P could be left unconnected and CPUMP pins tied to VDD. A 4.7- $\mu$ F CPUMP capacitor is used to store energy for the gate driver. The CPUMP capacitor is required to be used in both charge pump enabled and disabled conditions and must be placed as close as possible to the CPUMP pins. Figure 7-1 and Figure 7-2 show required connections for both use cases.

Figure 7-1. Charge Pump Enabled Circuit

Figure 7-2. Charge Pump Disabled Circuit

If the charge pump is enabled, the CPCAP\_STATUS bit shows whether a fly capacitor was detected and the CP\_STATUS bit shows status of any charge pump faults and generates an INT signal. The CP\_INT\_EN bit can be used to prevent the charge-pump fault from causing an interrupt on the INT pin.

## 7.3.6 Boost Controller

The TPS92391 current-mode-controlled boost DC/DC controller generates the anode voltage for the LEDs. The boost is a current-mode-controlled topology with a cycle by cycle current limit. The boost converter senses the switch current and across the external sense resistor connected between ISNS and ISNSGND. A 20-m $\Omega$  sense resistor results in a 10-A cycle by cycle current limit. The sense resistor value could vary from 15 m $\Omega$  to 50 m $\Omega$  depending on the application. Maximum boost voltage is configured with external FB-pin resistor divider connected between V<sub>OUT</sub> and FB. The FB-divider equation is described in Section 7.3.6.3.

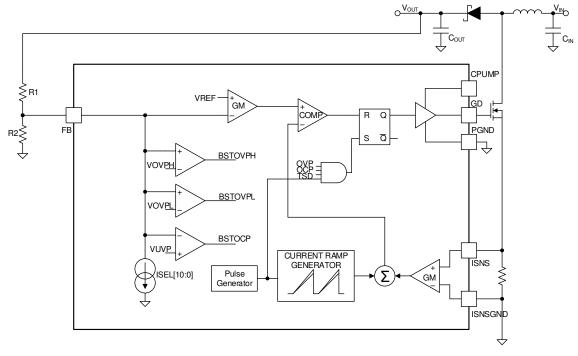

Figure 7-3. Boost Controller Block Diagram

The boost switching frequency is adjustable from 100 kHz to 2.2 MHz via an external resistor at BST\_FSET (see Table 7-1). Resistor with 1% accuracy is needed to ensure proper operation.

(1)

| Table 7-1. Doost i requency delection |  |  |  |  |  |  |

|---------------------------------------|--|--|--|--|--|--|

| BOOST FREQUENCY (kHz)                 |  |  |  |  |  |  |

| 400                                   |  |  |  |  |  |  |

| 200                                   |  |  |  |  |  |  |

| 303                                   |  |  |  |  |  |  |

| 100                                   |  |  |  |  |  |  |

| 500                                   |  |  |  |  |  |  |

| 1818                                  |  |  |  |  |  |  |

| 2000                                  |  |  |  |  |  |  |

| 2222                                  |  |  |  |  |  |  |

|                                       |  |  |  |  |  |  |

## Table 7-1. Boost Frequency Selection

## 7.3.6.1 Boost Cycle-by-Cycle Current Limit

The voltage between ISNS and ISNSGND is used for both boost DC/DC controller's current sensing and cycle-by-cycle current limit settings. When the cycle-by-cycle current limit is reached, the controller will turn off the switching MOSFET immediately and turn on it again in next siwtching cycle. This cycle-by-cycle current limit could be used as a common protection for all related DC/DC components (inductor, schottky diode and switching MOSFET) to avoid current running over their max limit. Cycle-by-Cycle current limit won't trigger any faults of the device.

$$I_{CYCLE\_LIMIT} = \frac{V_{ISNS}}{R_{SENSE}}$$

where

• V<sub>ISNS</sub> = 200 mV

## 7.3.6.2 Controller Min On/Off Time

The device boost DC/DC controller has minimum on/off time as below table. Minimum off time should be specially taken care in system design. The SW node rising time plus falling time should be higher than minimum off time to avoid controller not turning off the MOSFET.

| Frequency (kHz) | Minimum Switch OFF Time (ns) | Minimum Switch ON Time (ns) |  |  |  |  |

|-----------------|------------------------------|-----------------------------|--|--|--|--|

| 100 to 500      | 150                          | 150                         |  |  |  |  |

| 1818 to 2222    | 40                           | 110                         |  |  |  |  |

#### Table 7-2. Controller Minimum On/Off Time

#### 7.3.6.3 Boost Adaptive Voltage Control

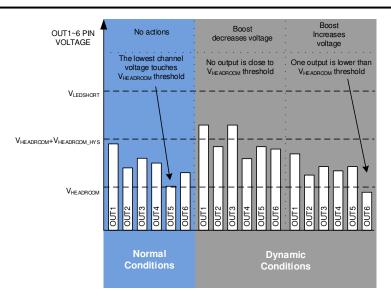

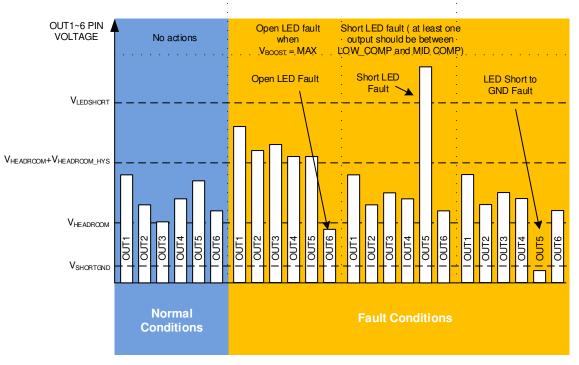

The TPS92391 boost DC/DC converter generates the anode voltage for the LEDs. During normal operation, boost output voltage is adjusted automatically based on the LED current sink headroom voltages. This is called adaptive boost control. The number of used LED outputs is set by LED\_SET pin and only the active LED outputs are monitored to control the adaptive boost voltage. Any LED strings with open or short faults are also removed from the adaptive voltage control loop. The LED driver pin voltages are periodically monitored by the control loop and the boost voltage is raised if any of the LED outputs falls below the V<sub>HEADROOM</sub> threshold. The boost voltage is lowered until any of the LED outputs touch the V<sub>HEADROOM</sub> threshold. See Figure 7-4 for how the boost voltage automatically scales based on the OUTx-pin voltage, V<sub>HEADROOM</sub> and V<sub>HEADROOM</sub> HYS.

Figure 7-4. Adaptive Boost Voltage Control Loop Function

The resistive divider ( $R_1$ ,  $R_2$ ) defines both the minimum and maximum adaptive boost voltage levels. The feedback circuit operates the same in boost and SEPIC topologies. Choose maximum boost voltage based on the maximum LED string voltage specification. Before the LED drivers are active, the boost starts up to the initial boost level. The initial boost voltage is approximately in the 88% point of minimum to maximum boost voltage. Once the LED driver channels are active, the boost output voltage is adjusted automatically based on OUTx pin voltages. The FB pin resistor divider also scales the boost OVP, OCP levels and the LED short level in HUD application.

## 7.3.6.3.1 FB Divider Using Two-Resistor Method

A typical FB-pin circuit uses a two-resistor divider circuit between the boost output voltage and ground.

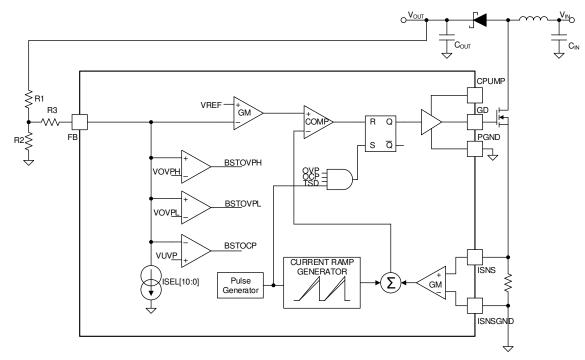

Figure 7-5. Two-Resistor FB Divider Circuit

Maximum boost voltage can be calculated with Equation 2. The maximum boost voltage can be reached during OPEN string detection or if all LED strings are left disconnected.

$$V_{\text{BOOST}_MAX} = I_{\text{SEL}_MAX} \times R_1 + \left(\frac{R_1}{R_2} + 1\right) \times V_{\text{REF}}$$

<sup>(2)</sup>

where

- V<sub>REF</sub>= 1.21 V

- I<sub>SEL\_MAX</sub> = 38.7 μA

- $R_1/R_2$  normal recommended range is 7~15

The minimum boost voltage must be less than the minimum LED string voltage. Minimum boost voltage is calculated with Equation 3:

$$V_{\text{BOOST}_{\text{MIN}}} = \left(\frac{R_1}{R_2} + 1\right) \times V_{\text{REF}}$$

(3)

where

• V<sub>REF</sub> = 1.21 V

When the boost OVP\_LOW level is reached, the boost controller stops switching the boost FET and the BSTOVPL\_STATUS bit is set. The LED drivers are still active during this condition, and the boost resumes normal switching operation once the boost output level falls. The boost OVP low voltage threshold changes dynamically with current boost voltage. It is calculated in Equation 4:

$$V_{\text{BOOST}_\text{OVPL}} = V_{\text{BOOST}} + \left(\frac{R_1}{R_2} + 1\right) \times (V_{\text{FB}_\text{OVPL}} - V_{\text{REF}})$$

(4)

where

- V<sub>FB OVPL</sub> = 1.423 V

- V<sub>REF</sub> = 1.21 V

When the boost OVP\_HIGH level is reached the boost controller enters fault recovery mode, and the BSTOVPH\_STATUS bit is set. The boost OVP high-voltage threshold also changes dynamically with current boost voltage and is calculated in Equation 5:

$$V_{\text{BOOST}_\text{OVPH}} = V_{\text{BOOST}} + \left(\frac{R_1}{R_2} + 1\right) \times (V_{\text{FB}_\text{OVPH}} - V_{\text{REF}})$$

<sup>(5)</sup>

where

• V<sub>FB OVPH</sub> = 1.76 V

When the boost UVP level is reached the boost controller starts a 110-ms OCP counter. The TPS92391 device enters the fault recovery mode and sets the BSTOCP\_STATUS bit if the boost voltage does not rise above the UVP threshold before the timer expires. The boost UVP voltage threshold also changes dynamically with current boost voltage and is calculated in Equation 6:

Copyright © 2021 Texas Instruments Incorporated

$$V_{BOOST\_UVP} = V_{BOOST} - \left(\frac{R_1}{R_2} + 1\right) \times (V_{REF} - V_{UVP})$$

(6)

where

- V<sub>UVP</sub> = 0.886 V

- V<sub>REF</sub> = 1.21 V

#### 7.3.6.3.2 FB Divider Using Three-Resistor Method

A FB-pin circuit using a three-resistor divider circuit can be used for applications where less than 200-k $\Omega$  resistors are required.

Figure 7-6. Three-Resistor FB Divider Circuit

Maximum boost voltage can be calculated with Equation 7. The maximum boost voltage can be reached during OPEN string detection or if all LED strings are left disconnected.

$$V_{\text{BOOST}_MAX} = \left(\frac{R_1 \times R_3}{R_2} + R_1 + R_3\right) \times I_{\text{SEL}_MAX} + \left(\frac{R_1}{R_2} + 1\right) \times V_{\text{REF}}$$

(7)

where

- V<sub>REF</sub> = 1.21 V

- I<sub>SEL MAX</sub> = 38.7 μA

- $R_1/R_2$  normal recommended range is 7 to 15

The minimum boost voltage must be less than the minimum LED string voltage. Minimum boost voltage is calculated in Equation 8:

$$V_{\text{BOOST}_MIN} = \left(\frac{R_1}{R_2} + 1\right) \times V_{\text{REF}}$$

(8)

When the boost OVP\_LOW level is reached the boost controller stops switching the boost FET, and the BSTOVPL\_STATUS bit is set. The LED drivers are still active during this condition, and the boost resumes normal switching operation once the boost output level falls. The boost OVP low voltage threshold changes dynamically with current boost voltage. It is calculated in Equation 9:

$$V_{\text{BOOST}_\text{OVPL}} = V_{\text{BOOST}} + \left(\frac{R_1}{R_2} + 1\right) \times (V_{\text{FB}_\text{OVPL}} - V_{\text{REF}})$$

<sup>(9)</sup>

where

- V<sub>FB OVPL</sub>= 1.423 V

- V<sub>REF</sub>= 1.21 V

When the boost OVP\_LOW level is reached the boost controller enters fault recovery mode, and the BSTOVPH\_STATUS bit is set. The boost OVP high-voltage threshold also changes dynamically with current boost voltage and is calculated in Equation 10:

$$V_{\text{BOOST}_\text{OVPH}} = V_{\text{BOOST}} + \left(\frac{R_1}{R_2} + 1\right) \times (V_{\text{FB}_\text{OVPH}} - V_{\text{REF}})$$

<sup>(10)</sup>

where

- V<sub>FB\_OVPH</sub> = 1.76 V

- V<sub>REF</sub>= 1.21 V

When the boost UVP level is reached the boost controller starts a 110-ms OCP counter. The TPS92391 device enters the fault recovery mode and sets the BSTOCP\_STATUS bit if the boost voltage does not rise above the UVP threshold before the timer expires. The boost UVP voltage threshold also changes dynamically with current boost voltage and is calculated in Equation 11:

$$V_{\text{BOOST}_{\text{UVP}}} = V_{\text{BOOST}} - \left(\frac{R_1}{R_2} + 1\right) \times (V_{\text{REF}} - V_{\text{UVP}})$$

<sup>(11)</sup>

where

• V<sub>UVP</sub> = 0.886 V

• V<sub>REF</sub>= 1.21 V

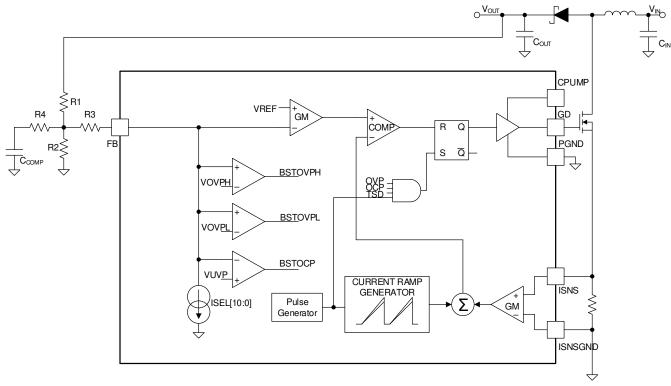

#### 7.3.6.3.3 FB Divider Using External Compensation

The device has internal compensation network to keep the DC-DC control loop in good stability in most cases. However, an additional external compensation network could also be added on FB-pin to offer more flexibility in loop design or solving some extreme use-cases.

Figure 7-7. External Compensation Network

This network will create one additional pole and one additional zero in the loop.

$$f_{\text{POLE}\_\text{COMP}} = \frac{1}{2\pi [(R_1 || R_2) + R_4] C_{\text{COMP}}}$$

(12)

$$f_{\text{ZERO}\_\text{COMP}} = \frac{1}{2\pi R_4 C_{\text{COMP}}}$$

(13)

It could be noted that  $R_3$  doesn't take part in the compensation. So this external compensation network could be both used in two-divider network and T-divider network with no equation change.

In real application, for example, when DC-DC loop has stability concern, putting the additional pole in 1 kHz and the additional zero in 2 kHz will suppress the loop gain by approximately 6 dB after 2 kHz. This will benefit gain margin and phase margin a lot.

#### 7.3.6.4 Boost Sync and Spread Spectrum

Spread spectrum function could be enabled when BST\_SYNC pin is high and disabled when BST\_SYNC pin is low.

If an external CLK signal is on the BST\_SYNC pin, the boost controller can be clocked by this signal. If the clock disappears later, the boost continues operation at the frequency defined by RBST\_FSET resistor, and the spread spectrum function will be enabled or disabled depending on the final pin level of BST\_SYNC.

| BST_SYNC PIN LEVEL | BOOST CLOCK MODE         |  |  |  |  |  |

|--------------------|--------------------------|--|--|--|--|--|

| Low (GND)          | Spread spectrum disabled |  |  |  |  |  |

| High (VDDIO)       | Spread spectrum enabled  |  |  |  |  |  |

#### Table 7-3. Boost Synchronization Mode

#### Table 7-3. Boost Synchronization Mode (continued)

| BST_SYNC PIN LEVEL                  | BOOST CLOCK MODE                                        |

|-------------------------------------|---------------------------------------------------------|

| 100-kHz to 2222-kHz clock frequency | Spread spectrum disabled, external synchronization mode |

If using the external BST\_SYNC input, the R<sub>BST\_SET</sub> resistor should be chosen the closest boost frequency options with the external frequency.

The spread spectrum function helps to reduce EMI noise around the switching frequency and its harmonic frequencies. The internal spread spectrum function modulates the boost frequency  $\pm 3.3\%$  to 7.2% from the central frequency with a 200-Hz to 1.2-kHz modulation frequency. The switching frequency variation is programmable by SPREAD\_RANGE register, and the modulation frequency is programmable by SPREAD\_MOD\_FREQ register. The spread-spectrum function cannot be used when an external synchronization clock is used.

| Table 7-4. Spread Spectrum Frequency Range          |       |  |  |  |  |

|-----------------------------------------------------|-------|--|--|--|--|

| SPREAD_RANGE (Binary) SWITCHING FREQUENCY VARIATION |       |  |  |  |  |

| 00                                                  | ±3.3% |  |  |  |  |

| 01                                                  | ±4.3% |  |  |  |  |

| 10 (Default)                                        | ±5.3% |  |  |  |  |

| 11                                                  | ±7.2% |  |  |  |  |

| Table 7-5. Spread Spectrum Modulation Frequency |                      |  |  |  |  |

|-------------------------------------------------|----------------------|--|--|--|--|

| SPREAD_MOD_FREQ (Binary)                        | MODULATION FREQUENCY |  |  |  |  |

| 00 (Default)                                    | 200 Hz               |  |  |  |  |

| 01                                              | 500 Hz               |  |  |  |  |

| 10                                              | 800 Hz               |  |  |  |  |

1200 Hz

#### 7.3.6.5 Light Load Mode

The DC-DC controller will enter into light load mode in below condition:

V<sub>IN</sub> voltage is very close to V<sub>OUT</sub>

11

- Loading current is very low

- PWM pulse width is very short

When DC-DC converter enters into light load mode, it stops switching occasionally to make sure output voltage won't rise up too much. It could also be called as PFM mode, since the DC-DC converter switching frequency will change in this mode.

## 7.3.7 LED Current Sinks

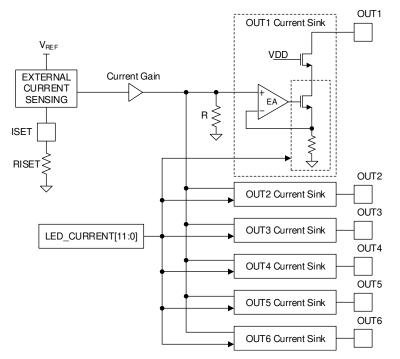

#### 7.3.7.1 LED Output Current Setting

The maximum output LED current is set by an external resistor value. For the application only using external resistor  $R_{ISET}$  to set the maximum LED current for each string, the Equation 14 is used to calculate the current setting of all strings:

$$I_{LED} = \frac{1.21V}{R_{ISET}} \times 2580$$

(14)

The LEDx\_CURRENT[11:0] registers can also be used to adjust strings current down from this maximum. The default value for LEDx\_CURRENT[11:0] registers is the maximum 0xFFF(4095). Equation 15 is used to calculate the current setting of an individual string:

$$I_{\text{LED}} = \left(\frac{1.21V}{R_{\text{ISET}}} \times 2580\right) \times \left(\frac{\text{LED}_\text{CURRENT}[11:0]}{4095}\right)$$

(15)

For high accuracy of LED current, the ILED current is recommended to set in range from 30 mA to 200 mA. So the R<sub>ISET</sub> value is in the range from 15.6 k $\Omega$  to 104 k $\Omega$ .

Figure 7-8. LED Driver Current Setting Circuit

## 7.3.7.2 LED Output String Configuration

The Six LED driver channels of the TPS92391 device is configured by the LED\_SET resistor, which supports applications using one to Six LED strings. Resistor with 1% accuracy is needed to ensure proper operation. The driver channels can also be tied together in groups of one, two or three. This allows the TPS92391 device to drive three 400-mA LED strings, two 600-mA LED strings, or one 1200-mA LED string. The LED strings are always appropriately phase shifted for their string configuration. This reduces the ripple seen at the boost output, which allows smaller output capacitors and reduces audible ringing in the capacitors. Phase shift increases the load frequency, which can move potential capacitor noise above the audible band while still keeping PWM frequency low to support a higher dimming ratio.

When the TPS92391 device is firstly powered on, the string configuration is configured by the LED\_SET resistor and the phases of each channel are automatically configured. The LED string configuration must not be changed unless the TPS92391 is powered off in shutdown state. The unused LEDx pins should be tied to ground.

| R_LED_SET (kΩ) | CONFIGURATION | OUT1   | OUT2   | OUT3   | OUT4             | OUT5             | OUT6          | AUTOMATIC<br>PHASE<br>SHIFT |

|----------------|---------------|--------|--------|--------|------------------|------------------|---------------|-----------------------------|

| 3.92           | 6 Channels    | 200 mA | 200 mA | 200 mA | 200 mA           | 200 mA           | 200 mA        | 60°                         |

| 4.75           | 5 Channels    | 200 mA | 200 mA | 200 mA | 200 mA           | 200 mA           | (Tied to GND) | 72°                         |

| 5.76           | 4 Channels    | 200 mA | 200 mA | 200 mA | 200 mA           | (Tied to<br>GND) | (Tied to GND) | 90°                         |

| 7.87           | 3 Channels    | 200 mA | 200 mA | 200 mA | (Tied to<br>GND) | (Tied to<br>GND) | (Tied to GND) | 120°                        |

Table 7-6. LED Output String Configuration

| R_LED_SET (kΩ) | CONFIGURATION | OUT1   | OUT2          | OUT3          | OUT4             | OUT5             | OUT6          | AUTOMATIC<br>PHASE<br>SHIFT |

|----------------|---------------|--------|---------------|---------------|------------------|------------------|---------------|-----------------------------|

| 11             | 2 Channels    | 200 mA | 200 mA        | (Tied to GND) | (Tied to<br>GND) | (Tied to<br>GND) | (Tied to GND) | 180°                        |

| 17.8           | 3 Channels    | 400    | mA            | 400           | mA               | 40               | 0 mA          | 120°                        |

| 42.2           | 2 Channels    |        | 600 mA 600 mA |               |                  |                  | 180°          |                             |

| 124            | 1 Channels    |        | 1200 mA       |               |                  |                  | None          |                             |

#### Table 7-6. LED Output String Configuration (continued)

## 7.3.7.3 LED Output PWM Clock Generation

The LED PWM frequency is asynchronous from the input PWM frequency. The LED PWM frequency is generated from the internal 20-MHz oscillator and can be set to eight discrete frequencies from 152 Hz to 19.531 kHz. The PWM dimming resolution is highest when the lowest PWM frequency is used. The PWM\_FSET resistor determines the LED PWM frequency based on Table 7-8. PWM resolution in Table 7-8 is with PWM dither disabled.

#### 7.3.8 Brightness Control

The TPS92391 supports global brightness control for all LED strings through either duty cycle input on PWM pin or register by I2C bus. An internal 20-MHz clock is used for generating PWM outputs.

#### 7.3.8.1 Brightness Control Signal Path

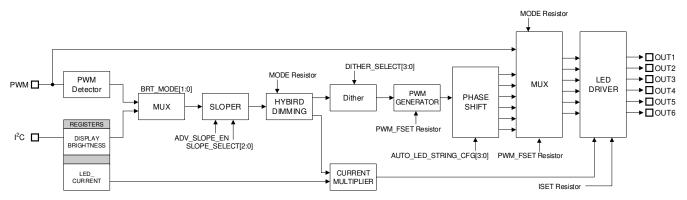

The BRT\_MODE register selects whether the input to the display brightness path is the PWM input pin or DISP\_BRT register. PWM input control will be the default setup after power on. The brightness control signal path diagram is shown in Figure 7-9

The display brightness path has sloper function that can be enabled. By default the sloper function is enabled. The sloper and dither function also can be programmable by I2C control. The sloper function is described in Section 7.3.8.7, and the dither function is described in Section 7.3.8.9.

Figure 7-9. TPS92391 Brightness Path Diagram

## 7.3.8.2 Dimming Mode

Dimming mode can be adjusted via an external resistor to MODE pin (see Table 7-7). Resistor with 1% accuracy is needed to ensure proper operation.

| R_MODE (kΩ) | MODE                 | I2C Address |  |  |  |  |

|-------------|----------------------|-------------|--|--|--|--|

| 3.92        | Phase-shift PWM Mode | 0x2B        |  |  |  |  |

| 4.75        | Hybrid Mode          | 0x2B        |  |  |  |  |

| 5.76        | Current Dimming Mode | 0x2B        |  |  |  |  |

| 7.87        | Direct PWM Mode      | 0x2B        |  |  |  |  |

| Table 7-7. Dimming Mode Configuration (continued) |                      |             |  |  |  |

|---------------------------------------------------|----------------------|-------------|--|--|--|

| R_MODE (kΩ)                                       | MODE                 | I2C Address |  |  |  |

| 11                                                | Phase-shift PWM Mode | 0x2A        |  |  |  |

| 17.8                                              | Hybrid Mode          | 0x2A        |  |  |  |

| 42.2                                              | Current Dimming Mode | 0x2A        |  |  |  |

| 124                                               | Direct PWM Mode      | 0x2A        |  |  |  |

# . .

## 7.3.8.3 LED Dimming Frequency

The LED dimming frequency is asynchronous from the input PWM frequency for phase-shift PWM mode and hybrid dimming mode. The LED dimming frequency is generated from the internal 20-MHz oscillator and can be set to eight discrete frequencies from 152 Hz to 19.531 kHz. The PWM dimming resolution is highest when the lowest PWM frequency is used. The PWM\_FSET resistor determines the LED Dimming frequency based on Table 7-8. Resistor with 1% accuracy is needed to ensure proper operation. PWM resolution in Table 7-8 is with PWM dither disabled.

| R_PWM_FSET (kΩ) | LED PWM FREQUENCY (Hz) | PWM DIMMING RESOLUTION (bits) |

|-----------------|------------------------|-------------------------------|

| 3.92            | 152                    | 16                            |

| 4.75            | 305                    | 16                            |

| 5.76            | 610                    | 15                            |

| 7.87            | 1221                   | 14                            |

| 11              | 2441                   | 13                            |

| 17.8            | 4883                   | 12                            |

| 42.2            | 9766                   | 11                            |

| 124             | 19531                  | 10                            |

#### Table 7-8. LED PWM Frequency Selection

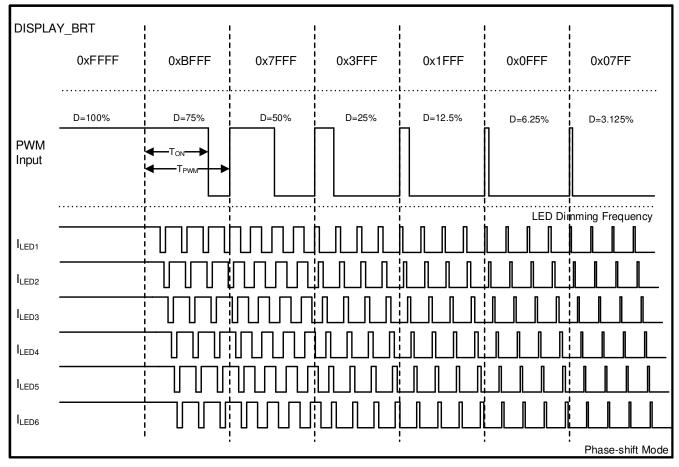

#### 7.3.8.4 Phase-Shift PWM Mode

In Phase-Shift PWM mode, all current active channels are turned on and off at LED dimming frequency with a constant delay. However, the number of used channels or channel groups determine the phase delay time between two neighboring channels as shown in Figure 7-10.

Figure 7-10. Phase-shift Dimming Diagram

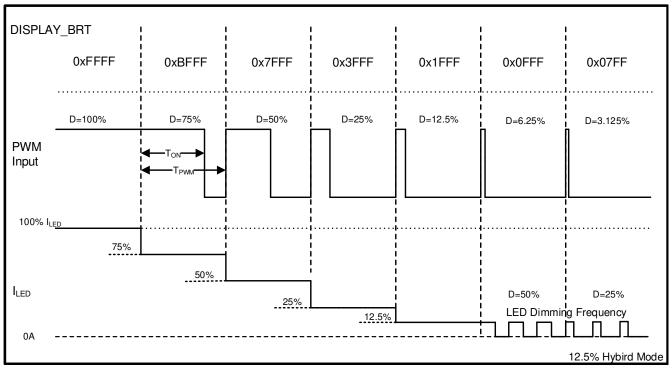

## 7.3.8.5 Hybrid Mode

In addition to phase-shift PWM dimming, TPS92391 supports a hybrid-dimming mode. Hybrid dimming combines PWM and current modes for brightness control for the display brightness path. By using hybrid dimming, dimming ratio could be increased by another 8 times. In hybrid mode, PWM dimming is used for low brightness range of brightness, and current dimming is used for high brightness levels as shown in Figure 7-11. Current dimming control enables improved optical efficiency due to increased LED efficiency at lower currents. PWM dimming control at low brightness levels ensures linear and accurate control. Hybrid mode can be selected through resistor value at MODE pin as Table 7-7. The PWM and current modes transition threshold can be set at 12.5% or at 0% brightness. The latter selection allows for pure current dimming control mode.

Figure 7-11. Hybrid Dimming Diagram

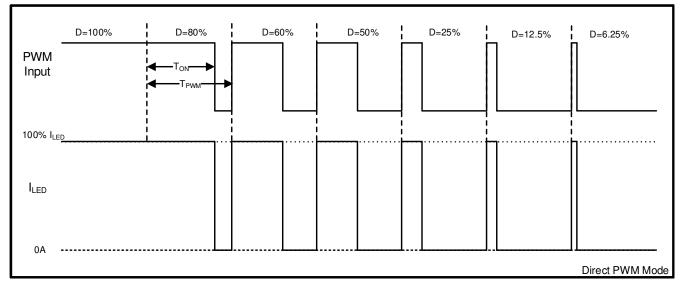

# 7.3.8.6 Direct PWM Mode

In direct PWM mode, all active channels are turned on and off and are synchronized with the input PWM signal.

Figure 7-12. Direct PWM Dimming Diagram

## 7.3.8.7 Sloper

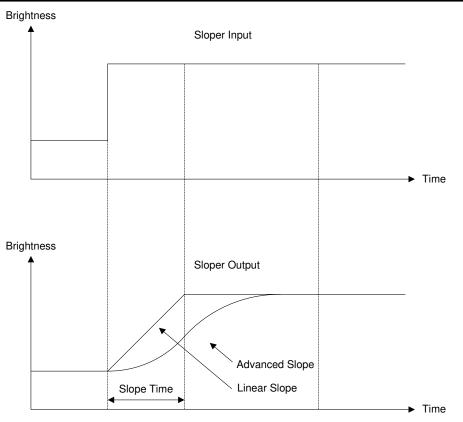

An optional sloper function makes the transition from one brightness value to another optically smooth. By default the advanced sloper is enabled with a 200-ms linear sloper duration. Transition time between two brightness values is programmed with the SLOPE\_SELECT[2:0] bits (when 000, sloper is disabled). With advanced sloper enabled the brightness changes are further smoothed to be more pleasing to the human eye. Advanced slope is enabled with ADV\_SLOPE\_ENABLE register bit.

Figure 7-13. Brightness Sloper

## 7.3.8.8 PWM Detector Hysteresis

PWM detector has an internal hysteresis function. It means when PWM input is used (except direct PWM mode), PWM output duty cycle will change only when PWM input on-time changes by more than 6.4us. This is to avoid the PWM duty cycle sampling error due to the onboard PWM signal's rising/falling time.

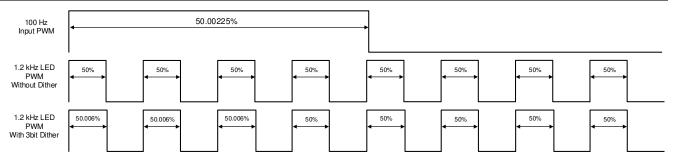

## 7.3.8.9 Dither

The number of brightness steps when using LED output PWM dimming is equal to the 20-MHz oscillator frequency divided by the LED PWM frequency (set by PWM\_FSET resistor). The PWM duty cycle dither is a function the TPS92391 uses to increase the number of brightness dimming steps beyond this oscillator clock limitation. The dither function modulates the LED driver output duty cycle over time to create more possible average brightness levels. The DITHER\_SELECT[3:0] register bits control the level of dither, disabled, 1, 2, 3 or 4 bits using the I2C interface. By default the dither is disabled.

When the 1-bit dither is selected, to support higher brightness resolution, the width of every second PWM pulse could be increased by one LSB (one 20-MHz clock period). When the 3-bit dither is selected, within a sequence of 8 PWM periods the number of pulses with increased length varies depending on the dither value: dither value 000 - all 8 pulses at default length; 001 - one of the 8 pulses is longer; 010 - two of the 8 pulses are longer, and so forth, until at 111 - seven of the 8 pulses have increased length. Figure 7-14 shows one example of PWM output dither.

Figure 7-14. PWM Dither Example

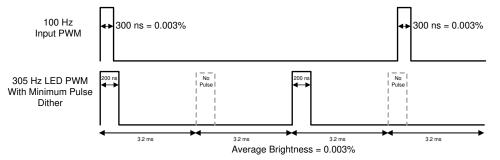

The dither block also helps in low brightness scenario when dimming ratio is limited by LED PWM output frequency and the LED output pulse is less than the minimum pulse width (200 ns). In such scenario, the dither block will skip some of the PWM pulses to reduce the brightness further, enabling high dimming ratio. The end result is that the LED PWM frequency is reduced as more and more minimum pulses are skipped or dithered out. At the same time, dither block will also guarantee that the minimum LED PWM frequency is not less than 152 Hz to ensure no brightness flickering. Figure 7-15 shows how the dither works in low brightness scenario.

Figure 7-15. Minimum Brightness Dither Example

## 7.3.9 Protection and Fault Detections

The TPS92391 device includes fault detections for LED open, short and short-to-GND conditions, boost input undervoltage, overvoltage and overcurrent, boost output overvoltage and overcurrent, VDD undervoltage, die overtemperature and external components. The host can monitor the status of the faults in registers SUPPLY\_FAULT\_STATUS, BOOST\_FAULT\_STATUS and LED\_STATUS.

## 7.3.9.1 Supply Faults

## 7.3.9.1.1 V<sub>IN</sub> Undervoltage Faults (VINUVLO)

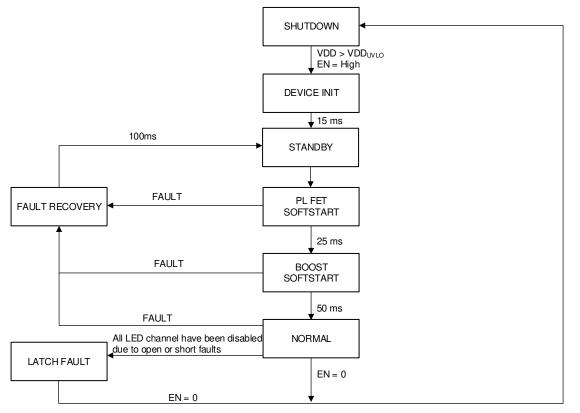

The TPS92391 device supports  $V_{IN}$  undervoltage and overvoltage protection. The undervoltage threshold is programmable through external resistor divider on UVLO pin. If during operation of the TPS92391 device, the UVLO pin voltage falls below the UVLO falling level (0.787 V typical), the boost, LED outputs, and power-line FET will be turned off, and the device will enter STANDBY mode. The VINUVLO\_STATUS bit is also set in the SUPPLY\_FAULT\_STATUS register, and the INT pin is triggered. When the UVLO voltage rises above the rising threshold level the TPS92391 exits STANDBY and begins the start-up sequence.

Figure 7-16. V<sub>IN</sub> UVLO Setting Circuit

The following equation is used to calculate the UVLO threshold for VIN rising edge:

$$VIN_{UVLO\_RISING} = \left(\frac{R_4}{R_5} + 1\right) \times VIN_{UVLO\_TH}$$

<sup>(16)</sup>

where

• VIN<sub>UVLO TH</sub> = 0.787 V

The hysteresis of UVLO threshold can be designed and calculated with the following equation.

$$VIN_{HYST} = R_4 \times I_{UVLO}$$

<sup>(17)</sup>

where

• I<sub>UVLO</sub> = 5 μA

So the following equation can be used for UVLO threshold for VIN falling edge:

$$VIN_{UVLO}FALLING} = VIN_{UVLO}RISING} - VIN_{HYST}$$

(18)

The bottom resistors,  $R_5$  of voltage divider is able to be disconnected to the GND through an additional external N-type of FET as Figure 7-17. This design is to minimize the current leakage from VIN in shutdown mode to extend the battery life.

Figure 7-17. VIN UVLO Setting Circuit Without Current Leakage Path

## 7.3.9.1.2 V<sub>IN</sub> Overvoltage Faults (VINOVP)

The overvoltage threshold for  $V_{IN}$  rising edge is internal fixed at typical 43 V. If during TPS92391 operation, VSENSE\_P pin voltage rises above the OVP rising threshold, boost, LED outputs, and power-line FET will be turned off, and the device will enter STANDBY mode. The VINOVP\_STATUS bit will also be set in the SUPPLY\_FAULT\_STATUS register, and the INT pin will be triggered. When the VSENSE\_P pin voltage falls below the falling threshold level, the TPS92391 exits STANDBY and begins the start-up sequence.

## 7.3.9.1.3 V<sub>DD</sub> Undervoltage Faults (VDDUVLO)

If during TPS92391 device operation VDD falls below VDDUVLO falling level, boost, power-line FET, and LED outputs are turned off, and the device enters STANDBY mode. The VDDUVLO\_STATUS fault bit will be set in the SUPPLY\_FAULT\_STATUS register, and the INT pin will be triggered. The TPS92391 restarts automatically to ACTIVE mode when V<sub>DD</sub> rises above VDDUVLO rising threshold.

## 7.3.9.1.4 V<sub>IN</sub> OCP Faults (VINOCP)

If during TPS92391 device operation voltage drop on RISENSE resistor rises above 220 mV, boost, power-line FET, and LED outputs are turned off, and the device enters Fault Recovery mode and then attempt to restart 100 ms after fault occurs. The VINOCP\_STATUS fault bit are set in the SUPPLY\_FAULT\_STATUS register, and the INT pin is triggered.

$$I_{VIN\_OCP} = \frac{VIN_{OCP\_TH}}{R_{ISENSE}}$$

where

• VIN<sub>OCP TH</sub> = 220 mV

## 7.3.9.1.4.1 VIN OCP Current Limit vs. Boost Cycle-by-Cycle Current Limit

VIN OCP current limit is totally different from boost cycle-by-cycle current limit.

Boost cycle-by-cycle current limit is to protect the DC/DC components (inductor, schottky diode and switching MOSFET) in normal scenario, avoiding current running over their max limit. The normal scenario means when loading has sharp change or input voltage has sharp change. It won't trigger any device fault.

VIN OCP current limit is to protect system from ciritical system hazard (e.g, inductor short, switching MOSFET short). It will trigger the device to shutdown all the LED channels and enter into fault recovery state.

VIN OCP current limit should be always greater than boost cycle-by-cycle current limit. This means  $R_{ISENSE}$  should be always no smaller than  $R_{SENSE}$ .

(19)