### Triple half-bridge gate driver

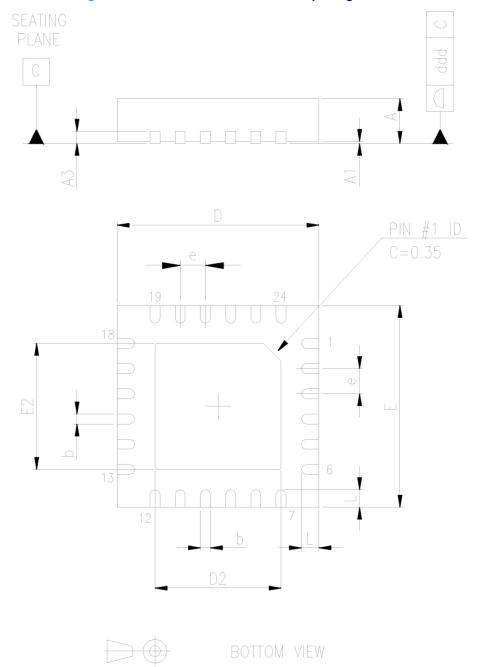

VFQFPN 4 x 4 x 1.0 mm 24 leads pitch 0.5 mm

#### **Features**

- Operating voltage from 5.5 to 75 V

- 600 mA sink/source current capability

- 3.3 V and 5 V control logic

- Two input strategies:

- ENx/INx with adjustable deadtime generation

- INHx/INLx with interlocking

- · Matched propagation delay for all channels

- Very short propagation delay: 40 ns

- Integrated bootstrap diodes

- 12 V LDO linear regulator (50 mA max.)

- Embedded V<sub>DS</sub> monitor for each external MOSFET

- Overcurrent comparator

- UVLO and thermal shutdown protection

- · Standby mode for low current consumption operation

### **Application**

- · Home automation and appliances

- e-bikes

- Power tools

- · Fans and pumps

- · Industrial automation

- Textile machines

- · Gaming and consoles

#### Product status link

STDRIVE101

#### Product label

### Description

The STDRIVE101 is a low voltage gate driver suitable for driving three-phase brushless motors.

It is a single-chip with three half-bridge gate drivers for N-channel power MOSFETs. Each driver has a current capability of 600 mA (sink/source). It integrates a low drop linear regulator generating the supply voltage for both low-side and high-side gate drivers through a bootstrap circuitry.

The device provides Under Voltage Lock Out (UVLO) on both the low-side and highside sections, preventing the power switches from operating in low efficiency or dangerous conditions.

The control logic integrated into the STDRIVE101 allows two input strategies (high-side and low-side or enable and PWM driving signals). The driving method is selected according to DT/MODE pin. In both cases, prevention from cross conduction is ensured by interlocking or internally generated deadtime.

The STDRIVE101 also features a  $V_{DS}$  monitoring protection for each external MOSFET, thermal shutdown and can be put in the standby mode to reduce the power consumption.

The device is available in a VFQFPN 4x4 24 leads package option.

## 1 Block diagram

Ţ S 12 V LDO Reg STBY V<sub>SCREF</sub> VBOOT SCREF Half-bridge 1 V<sub>DSth</sub> ► ΗH GHS1 DT/MODE OUT1 IN3/INH3 IN2/INH2 GLS1 IN1/INH1 ↓<sup>+</sup>V<sub>DSth</sub> Decoding logic and dead-time BOOT2 GHS2 OUT2 I GLS2 EN3/INL3 EN2/INL2 M Half-bridge 2 EN1/INL1 ВООТЗ GHS3 OUT3 GLS3 nFAULT Half-bridge 3 СР

Figure 1. STDRIVE101 block diagram

DS13472 - Rev 1 page 2/32

## 2 Electrical data

## 2.1 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in Table 1 may cause permanent damage to the device. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 1. Absolute maximum ratings

| Symbol                | Parameter                                               | Test Condition                         | Value                                           | Unit |

|-----------------------|---------------------------------------------------------|----------------------------------------|-------------------------------------------------|------|

| V <sub>S</sub>        | Supply voltage                                          |                                        | -0.3 to 78                                      | V    |

| dV <sub>S</sub> /dt   | Supply voltage slew rate                                |                                        | ± 10                                            | V/µs |

| V <sub>REG12</sub>    | Gate driving supply voltage                             | REG12 shorted to VS                    | -0.3 to 20                                      | V    |

| V <sub>OUTx</sub>     | OUTx pin voltage                                        |                                        | -2 to V <sub>S</sub> + 2                        | V    |

| V <sub>BOOTx</sub>    | Bootstrap pin voltage                                   |                                        | -0.3 to 98                                      | V    |

| V <sub>BOx</sub>      | High-side driver supply voltage                         | V <sub>BOOTx</sub> - V <sub>OUTx</sub> | -0.3 to 20                                      | V    |

| V <sub>GHSx</sub>     | High-side gates voltage                                 |                                        | V <sub>OUT</sub> -0.3 to V <sub>BOOT</sub> +0.3 | V    |

| $V_{GLSx}$            | Low-side gates voltage                                  |                                        | -0.3 to V <sub>REG12</sub> +0.3                 | V    |

| dV <sub>OUT</sub> /dt | Output slew rate                                        |                                        | ± 10                                            | V/ns |

| V <sub>IN</sub>       | Logic input voltage                                     |                                        | -0.3 to 5.5                                     | V    |

| V <sub>CP</sub>       | Overcurrent comparator inputs voltage                   |                                        | -2 to 5.5                                       | V    |

| V <sub>DT/MODE</sub>  | Deadtime input voltage                                  |                                        | -0.3 to 3.6                                     | V    |

| V <sub>SCREF</sub>    | V <sub>DS</sub> monitoring protection reference voltage |                                        | -0.3 to 3.6                                     | V    |

| V <sub>FAULT</sub>    | nFAULT output voltage                                   |                                        | -0.3 to 5.5                                     | V    |

| I <sub>FAULT</sub>    | nFAULT output sink current                              |                                        | Up to 8                                         | mA   |

| T <sub>stg</sub>      | Storage temperature                                     |                                        | -55 to 150                                      | °C   |

| T <sub>J</sub>        | Junction temperature                                    |                                        | -40 to 150                                      | °C   |

DS13472 - Rev 1 page 3/32

### 2.2 Recommended operating conditions

Table 2. Recommended operating conditions

| Symbol             | Parameter                                                      | Test Condition                                   | Min.               | Тур. | Max.               | Unit |

|--------------------|----------------------------------------------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| Vs                 | Supply voltage                                                 |                                                  | 5.5 <sup>(1)</sup> |      | 75                 | V    |

| \/                 | 12 V linear regulator output and                               | V <sub>S</sub> ≥ 15 V                            |                    | 12   |                    | V    |

| V <sub>REG12</sub> | gate driving supply voltage                                    | VS shorted to REG12                              | 5.5 <sup>(1)</sup> |      | 15                 | V    |

| V <sub>BOOTx</sub> | Bootstrap pin voltage                                          |                                                  |                    |      | 89                 | V    |

| I <sub>REG12</sub> | 12 V linear regulator total current consumption <sup>(2)</sup> | Internal (gate drivers) and external consumption |                    |      | 50                 | mA   |

| C <sub>REG12</sub> | 12 V linear regulator output capacitance                       |                                                  | 4.7                |      |                    | μF   |

| R <sub>DT</sub>    | Deadtime resistor                                              | ENx/INx mode                                     | 50                 |      | 250                | kΩ   |

| וטא                | Deautime resistor                                              | INHx/INLx mode                                   | Short to ground    |      | nd                 | K\$2 |

| V <sub>IN</sub>    | Logic input voltage                                            |                                                  | 0                  |      | 5 (3)              | V    |

| V <sub>CP</sub>    | Overcurrent comparator input voltage                           |                                                  | -1                 |      | 1                  | V    |

| V <sub>SCREF</sub> | V <sub>DS</sub> monitoring protection                          | Protection enabled                               | 0.2                |      | 2.5                | V    |

| VSCREF             | reference voltage (4)                                          | Protection disabled                              | 2.9                |      | 3.3                | V    |

| V <sub>FAULT</sub> | nFAULT output voltage                                          |                                                  | 0                  |      | 5                  | V    |

| T <sub>amb</sub>   | Operative ambient temperature                                  |                                                  | -40                |      | 125 <sup>(5)</sup> | °C   |

<sup>1.</sup> Actual operative range can be limited by UVLO protections

#### Important:

It is mandatory to use a VS voltage equal or greater than power stage voltage (VM in Figure 1). If not, the device is damaged.

DS13472 - Rev 1 page 4/32

<sup>2.</sup> Actual linear regulator current consumption can be limited by power dissipation

<sup>3.</sup> All digital inputs are 3.3 V TTL/CMOS thresholds compliant and 5 V tolerant. They can be biased within the respective AMR whatever the supply condition of the device (supplied, floating or shorted to ground) without causing damage to the device.

<sup>4.</sup> SCREF pin structure does not allow a bias without VS supply voltage

<sup>5.</sup> Actual operative range is limited by thermal shutdown

### 2.3 Thermal data

Table 3. Thermal data

| Symbol               | Parameter                                         | Conditions                                                                                   | Value | Unit |

|----------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------|

| R <sub>thJA</sub>    | Junction-to-ambient thermal resistance            | Natural convection, according to JESD51-2a (1) Cold plate on top, according to JESD51-12 (1) |       | °C/W |

| R <sub>thJCtop</sub> | Junction-to-case thermal resistance (top side)    |                                                                                              |       | °C/W |

| R <sub>thJCbot</sub> | Junction-to-case thermal resistance (bottom side) | Cold plate on exposed pad, according to JESD51-12 <sup>(1)</sup>                             | 1.47  | °C/W |

| R <sub>thJB</sub>    | Junction-to-board thermal resistance              | According to JESD51-8 <sup>(1)</sup>                                                         | 14.4  | °C/W |

| Ψ <sub>JT</sub>      | Junction-to-top characterization parameter        | According to JESD51-2a <sup>(1)</sup>                                                        |       | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter      | According to JESD51-2a <sup>(1)</sup>                                                        | 14.2  | °C/W |

<sup>1.</sup> Simulated on a 21.2x21.2 mm board, 2s2p 1 Oz copper and four 300  $\mu m$  vias below exposed pad.

### 2.4 Electrical sensitivity characteristics

**Table 4. ESD protection ratings**

| Symbol | Parameter Test Condition |                                           | Class | Value | Unit |

|--------|--------------------------|-------------------------------------------|-------|-------|------|

| HBM    | Human Body Model         | Conforming to ANSI/ESDA/JEDEC JS-001-2017 | H2    | 2     | kV   |

| CDM    | Charge Device Model      | Conforming to ANSI/ESDA/JEDEC JS-002-2014 | C2B   | 750   | V    |

DS13472 - Rev 1 page 5/32

## 3 Electrical characteristics

Testing conditions:  $V_S$  = 60 V unless otherwise specified.

Typical values are tested at  $T_J$  = 25 °C, minimum and maximum values are guaranteed by thermal characterization in the temperature range of -40 to 125 °C, unless otherwise specified.

Table 5. Electrical characteristics

| Symbol                   | Parameter                                                          | Test Condition                                                                               | Min. | Тур. | Max.  | Unit |

|--------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|-------|------|

| Supply and s             | tandby mode                                                        |                                                                                              | '    |      |       |      |

| V <sub>REG12(On)</sub>   | V <sub>REG12</sub> UVLO turn-on threshold                          | V <sub>REG12</sub> rising                                                                    |      |      | 5.5   | V    |

| V <sub>REG12(Hyst)</sub> | V <sub>REG12</sub> UVLO hysteresis                                 | V <sub>REG12</sub> falling                                                                   | 100  |      |       | mV   |

| V <sub>BO(On)</sub>      | $V_{BOOT}$ - $V_{OUT}$ UVLO turn-<br>on threshold                  | V <sub>BOOT</sub> rising                                                                     |      |      | 5     | V    |

| V <sub>BO(Hyst)</sub>    | V <sub>BOOT</sub> - V <sub>OUT</sub> UVLO<br>hysteresis            | V <sub>BOOT</sub> falling                                                                    | 100  |      |       |      |

| I <sub>BOOT</sub>        | V <sub>BOOT</sub> - V <sub>OUT</sub> quiescent current             | T <sub>J</sub> = 25 °C                                                                       | 85   | 155  | 225   | μΑ   |

| I <sub>qu</sub>          | Overall quiescent consumption from VS                              | $V_S$ = 60 V<br>All gate driver outputs low<br>SCREF = 3.3 V                                 |      | 1700 | 2800  | μA   |

| I <sub>STBY</sub>        | Overall standby consumption from VS                                | $V_S$ = 60 V, Device in standby mode $T_J$ = 25 °C                                           |      | 10   | 16    | μА   |

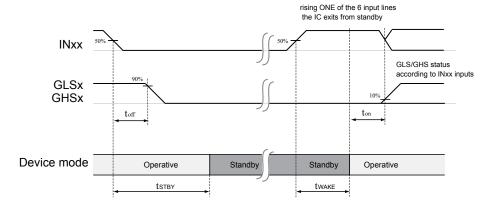

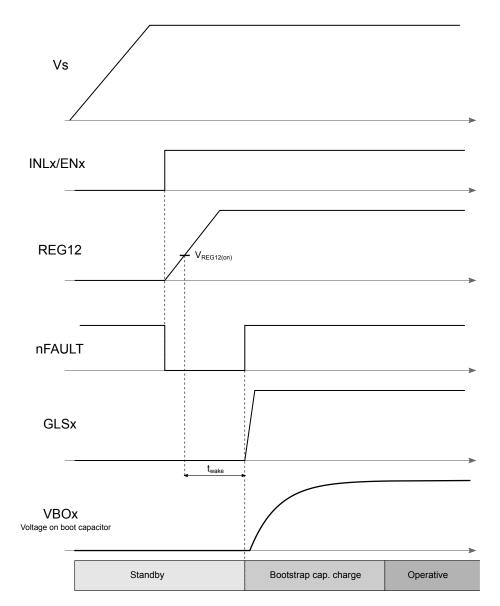

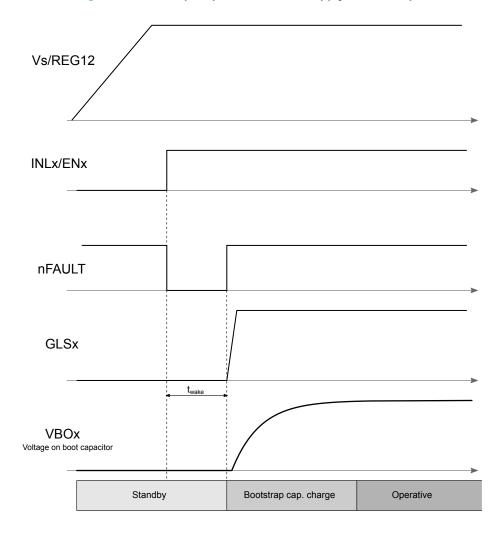

| t <sub>STBY</sub>        | Standby time                                                       | See Figure 15 and Figure 16                                                                  | 300  |      | 1200  | μs   |

| t <sub>WAKE</sub>        | Wake-up time                                                       | V <sub>S</sub> = V <sub>REG12</sub> = 12 V<br>Figure 15 and Figure 16                        |      |      | 50    | μs   |

| 12 V Linear re           | egulator                                                           |                                                                                              |      |      |       |      |

| V <sub>REG12</sub>       | 12 V linear regulator output<br>and gate driving supply<br>voltage | $V_S$ = 60 V $I_{REG12}$ = 50 mA All gate driver outputs low                                 | 11.4 | 12.2 | 12.75 | V    |

| I <sub>REG12lim</sub>    | 12 V linear regulator current limit                                | REG12 shorted to ground                                                                      | 55   |      |       | mA   |

| Gate drivers             |                                                                    |                                                                                              |      |      |       |      |

|                          |                                                                    | $V_S = V_{REG12} = 12 \text{ V}$ $V_{BOOTx}-V_{OUTx} = 12 \text{ V}$ $T_J = 25 \text{ °C}$   | 400  | 600  |       | mA   |

| I <sub>SI</sub>          | Maximum sink current capabilities                                  | $V_S = V_{REG12} = 12 \text{ V}$ $V_{BOOTx}-V_{OUTx} = 12 \text{ V}$ Full temperature range  | 300  |      |       | mA   |

|                          |                                                                    | $V_S = V_{REG12} = 5.5 \text{ V}$ $V_{BOOTx}-V_{OUTx} = 5.5 \text{ V}$ $T_J = 25 \text{ °C}$ | 350  |      |       | mA   |

DS13472 - Rev 1 page 6/32

| Symbol                             | Parameter                         | Test Condition                                | Min. | Тур. | Max. | Unit |

|------------------------------------|-----------------------------------|-----------------------------------------------|------|------|------|------|

|                                    |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 5.5 V   |      |      |      |      |

| I <sub>SI</sub>                    | Maximum sink current capabilities | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 5.5 V | 250  |      |      | mA   |

|                                    |                                   | Full temperature range                        |      |      |      |      |

|                                    |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 12 V    |      |      |      |      |

|                                    |                                   | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 12 V  | 350  | 600  |      | mA   |

|                                    |                                   | T <sub>J</sub> = 25 °C                        |      |      |      |      |

|                                    |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 12 V    |      |      |      |      |

|                                    |                                   | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 12 V  | 300  |      |      | mA   |

|                                    | Maximum source current            | Full temperature range                        |      |      |      |      |

| I <sub>SO</sub>                    | capabilities                      | V <sub>S</sub> = V <sub>REG12</sub> = 5.5 V   |      |      |      |      |

|                                    |                                   | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 5.5 V | 300  |      |      | mA   |

|                                    |                                   | T <sub>J</sub> = 25 °C                        |      |      |      |      |

|                                    |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 5.5 V   |      |      |      |      |

|                                    |                                   | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 5.5 V | 250  |      |      | mA   |

|                                    |                                   | Full temperature range                        |      |      |      |      |

|                                    |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 12 V    |      |      |      |      |

|                                    | PMOS on resistance                | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 12 V  |      |      |      |      |

|                                    |                                   | I <sub>source</sub> = 100 mA                  |      | 3.8  | 4.8  | Ω    |

|                                    |                                   | T <sub>J</sub> = 25 °C                        |      |      |      |      |

| R <sub>PMOS</sub>                  |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 5.5 V   |      |      |      |      |

|                                    |                                   | $V_{BOOTx}$ - $V_{OUTx}$ = 5.5 V              |      |      |      |      |

|                                    |                                   | I <sub>source</sub> = 100 mA                  |      |      | 6.1  | Ω    |

|                                    |                                   | Full temperature range                        |      |      |      |      |

|                                    |                                   | V <sub>S</sub> = V <sub>REG12</sub> = 12 V    |      |      |      |      |

|                                    |                                   | $V_{BOOTx}-V_{OUTx} = 12 \text{ V}$           |      |      |      |      |

|                                    |                                   | I <sub>sink</sub> = 100 mA                    |      | 1.8  | 2.3  | Ω    |

|                                    |                                   | T <sub>J</sub> = 25 °C                        |      |      |      |      |

| R <sub>NMOS</sub>                  | NMOS on resistance                | V <sub>S</sub> = V <sub>REG12</sub> = 5.5 V   |      |      |      |      |

|                                    |                                   | $V_{BOOTx}$ - $V_{OUTx}$ = 5.5 V              |      |      |      |      |

|                                    |                                   | I <sub>sink</sub> = 100 mA                    |      |      | 3    | Ω    |

|                                    |                                   | Full temperature range                        |      |      |      |      |

|                                    |                                   | OUTx = VS = 60 V                              |      |      |      |      |

|                                    |                                   | T <sub>J</sub> = 25 °C                        | 85   | 155  | 225  | μA   |

| I <sub>OUT,bias</sub>              | OUTx bias current                 | OUTx = 0 V                                    |      |      |      |      |

|                                    |                                   | T <sub>J</sub> = 25 °C                        | 85   | 155  | 225  | μA   |

|                                    |                                   | (1)                                           |      | 40   | 70   | ns   |

|                                    | Input to output propagation       | V <sub>S</sub> = V <sub>REG12</sub> = 5.5 V   |      |      |      |      |

| t <sub>on</sub> , t <sub>off</sub> | delay                             | V <sub>BOOTx</sub> -V <sub>OUTx</sub> = 5.5 V |      |      | 120  | ns   |

|                                    |                                   | Full temperature range                        |      |      |      |      |

DS13472 - Rev 1 page 7/32

| Symbol                    | Parameter                                               | Test Condition                          | Min. | Тур. | Max. | Unit |

|---------------------------|---------------------------------------------------------|-----------------------------------------|------|------|------|------|

| MT                        | Delay matching, HS and LS turn-on/off                   | (2)                                     |      |      | 20   | ns   |

| MT <sub>CH</sub>          | Delay matching between channels                         | (3)                                     |      |      | 20   | ns   |

| R <sub>DS_diode</sub>     | Bootstrap diode ON resistance                           |                                         |      | 100  | 240  | Ω    |

|                           |                                                         | $R_{DT} = 50 \text{ k}\Omega$           | 480  | 570  | 650  |      |

| t <sub>DT</sub>           | Deadtime                                                | $R_{DT}$ = 250 k $\Omega$ ;             | 2100 | 2600 | 2200 | ns   |

|                           |                                                         | T <sub>J</sub> = 25 °C                  | 2100 | 2000 | 3200 |      |

| MDT                       | Matching deadtime                                       | $R_{DT}$ = 50 k $\Omega$ <sup>(4)</sup> |      |      | 70   | ns   |

| MDT <sub>CH</sub>         | Matching deadtime between channels                      | $R_{DT} = 50 \text{ k}\Omega$ (5)       |      |      | 70   | ns   |

| Logic inputs              | ·                                                       |                                         |      |      |      |      |

| V <sub>IL</sub>           | Low logic input voltage                                 |                                         |      |      | 0.8  | V    |

| V <sub>IH</sub>           | High logic input voltage                                |                                         | 2    |      |      | V    |

| I <sub>IH</sub>           | Logic "1" input bias current                            | IN = 3.3 V<br>T <sub>J</sub> = 25 °C    | 12   | 16.5 | 25   | μΑ   |

| I <sub>IL</sub>           | Logic "0" input bias current                            | IN = 0 V<br>T <sub>J</sub> = 25 °C      |      |      | 100  | nA   |

| R <sub>PDin</sub>         | Input lines pull-down resistor                          | T <sub>J</sub> = 25 °C                  | 132  | 200  | 275  | kΩ   |

| V <sub>FAULT,L</sub>      | nFAULT low logic output voltage                         | I <sub>SINK</sub> = 4 mA                |      |      | 0.6  | V    |

| Overcurrent C             | Comparator                                              |                                         | ·    |      |      |      |

| $V_{REF}$                 | Comparator reference voltage                            | Full temperature range                  | 470  | 505  | 525  | mV   |

| l                         | Comparator input leakage                                | V <sub>CP</sub> = 1 V                   |      |      | 2    | μA   |

| I <sub>CP</sub>           | current                                                 | V <sub>CP</sub> = -0.5 V                | -2.5 |      |      | μA   |

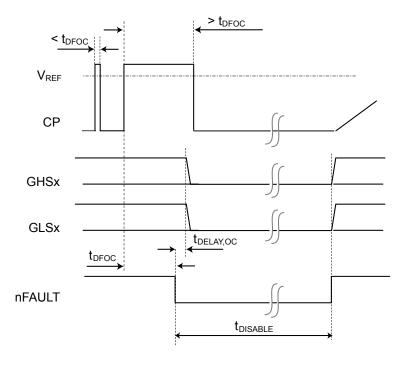

| t <sub>DELAY,OC</sub>     | Overcurrent delay time                                  | See Figure 5                            |      |      | 200  | ns   |

| t <sub>DFOC</sub>         | Deglitch filter time                                    | See Figure 5                            | 1.3  | 1.8  | 2.8  | μs   |

| t <sub>DISABLE</sub>      | Overcurrent disable time                                | See Figure 5                            | 455  | 600  | 865  | μs   |

| V <sub>DS</sub> monitorin | ng protection                                           |                                         |      | ı    |      |      |

|                           |                                                         | V <sub>SCREF</sub> = 0.2 V              | 0.1  | 0.2  | 0.3  |      |

| $V_{DSth}$                | V <sub>DS</sub> monitoring protection threshold         | V <sub>SCREF</sub> = 1 V                | 0.8  | 1    | 1.2  | V    |

|                           | tillesiloid                                             | V <sub>SCREF</sub> = 2.5 V              | 2.2  | 2.5  | 2.8  | -    |

| V <sub>SCREF,dis</sub>    | V <sub>DS</sub> monitoring protection disable voltage   |                                         | 2.9  |      |      | V    |

| V <sub>SCREF,en</sub>     | V <sub>DS</sub> monitoring protection enable voltage    |                                         |      |      | 2.54 | V    |

| R <sub>SCREF</sub>        | V <sub>DS</sub> monitoring reference pull-down resistor |                                         |      | 450  |      | kΩ   |

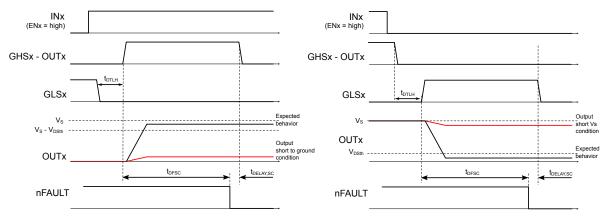

| t <sub>DFSC</sub>         | V <sub>DS</sub> monitoring protection deglitch time     | See Figure 6                            | 2.75 | 4.4  | 6.45 | μs   |

DS13472 - Rev 1 page 8/32

| Symbol                | Parameter                                        | Test Condition | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------------|----------------|------|------|------|------|

| t <sub>DELAY,SC</sub> | V <sub>DS</sub> monitoring protection delay time | See Figure 6   |      |      | 200  | ns   |

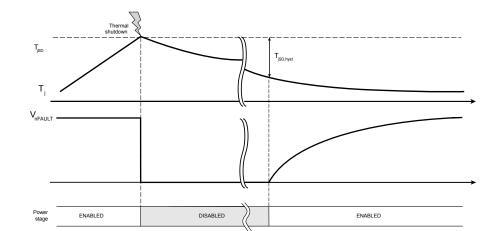

| Thermal protect       | ction <sup>(6)</sup>                             |                |      |      |      |      |

| T <sub>SD</sub>       | Thermal shutdown temperature                     |                | 150  | 165  |      | °C   |

| T <sub>SDhys</sub>    | Thermal shutdown hystreresis                     |                |      | 30   |      | °C   |

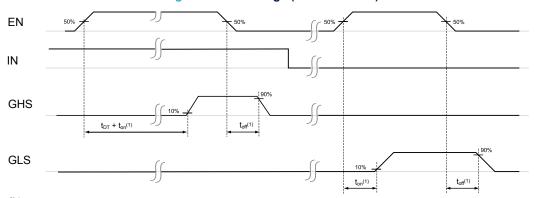

- These timings are measured using INHx/INLx mode (refer to Figure 4). An extra time is added when the device works with ENx/INx mode (refer to Figure 2 and Figure 3)

- $2. \quad MT = max. \ (|t_{on(GLS)} t_{off(GLS)}|, \ |t_{on(GHS)} t_{off(GHS)}|, \ |t_{off(GLS)} t_{on(GHS)}|, \ |t_{off(GHS)} t_{on(GHS)}|).$

- 3.  $MT_{CH}$  is the difference between the  $t_{on}$  and  $t_{off}$  of a channel and the same timings of any other channel.

- 4.  $MDT = |t_{DTHL} t_{DTLH}|$  see Figure 2.

- 5.  $MDT_{CH}$  is the difference between the  $t_{DTHL}$  and  $t_{DTLH}$  of a channel and the same timings of any other channel.

- Based on characterization data on a limited number of samples, not tested during production

ΕN IN **GHS**  $t_{\text{off}}^{(1)}$ GLS  $t_{\rm off}^{(1)}$ t<sub>DTHI</sub>

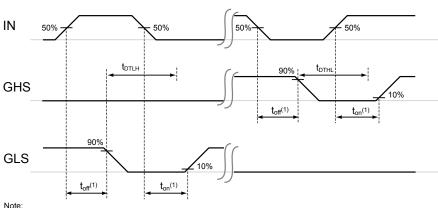

Figure 2. INx timings and deadtime (ENx/INx mode)

Note: (1) this propagation delay is typically 16 ns longer than the one measured in INH/INL driving mode (testing condition).

Figure 3. ENx timings (ENx/INx mode)

Note:

(1) this propagation delay is typically 16 ns longer than the one measured in INH/INL driving mode (testing condition)

DS13472 - Rev 1 page 9/32

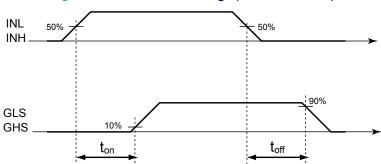

Figure 4. INHx and INLx timings (INHx/INLx mode)

Figure 5. Overcurrent comparator timings

Figure 6. V<sub>DS</sub> monitoring protection timing

DS13472 - Rev 1 page 10/32

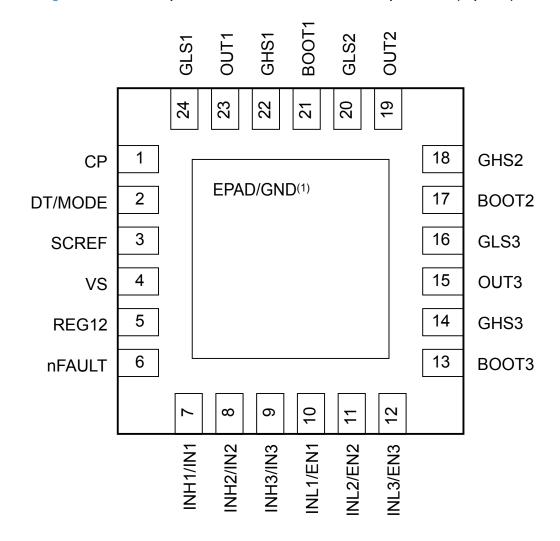

## 4 Pin description

Figure 7. STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view)

(1) The Exposed PAD is the ground connection of the device

DS13472 - Rev 1 page 11/32

Table 6. STDRIVE101 pin description

| QFN 24L | Name           | Туре              | Function                                                                                                                    |

|---------|----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1       | СР             | Analog in         | Overcurrent comparator input.                                                                                               |

| 2       | DT/MODE        | Analog in         | Adjust deadtime duration through a pull-down resistor (EHx/INx mode).  When shorted to ground, deadtime is disabled and the |

|         |                |                   | INHx/INLx driving mode is selected.                                                                                         |

|         | 00055          |                   | Set the threshold voltage of the V <sub>DS</sub> monitoring protection.                                                     |

| 3       | SCREF          | Analog in         | If the pin is left floating, the $V_{DS}$ monitoring protection is disabled.                                                |

| 4       | VS             | Power             | Supply voltage.                                                                                                             |

| 5       | REG12          | Power             | 12 V linear regulator output and gate drivers supply voltage.                                                               |

|         |                |                   | Fault output                                                                                                                |

|         |                |                   | Forced low when one of the following failure conditions occurs:                                                             |

| 6       | nFAULT         | Open-drain output | Overcurrent                                                                                                                 |

|         |                |                   | V <sub>DS</sub> monitoring protection triggered     Thermal shutdown                                                        |

|         |                |                   | UVLO on REG12 pin                                                                                                           |

| _       | 15.11.14.45.14 | B I.              | Output 1 high-side driving input (INHx/INLx mode)                                                                           |

| 7       | INH1/IN1       | Digital in        | Output 1 driving input (EHx/INx mode)                                                                                       |

| 8       | INH2/IN2       | Digital in        | Output 2 high-side driving input (INHx/INLx mode)                                                                           |

| 0       | 1111 12/11112  | Digital III       | Output 2 driving input (EHx/INx mode)                                                                                       |

| 9       | INH3/IN3       | Digital in        | Output 3 high-side driving input (INHx/INLx mode)                                                                           |

|         |                | 3 **              | Output 3 driving input                                                                                                      |

| 10      | INL1/EN1       | Digital in        | Output 1 low-side driving input (INHx/INLx mode)                                                                            |

|         |                | -                 | Output 1 enable input (EHx/INx mode)                                                                                        |

| 11      | INL2/EN2       | Digital in        | Output 2 low-side driving input (INHx/INLx mode)                                                                            |

|         |                |                   | Output 2 enable input (EHx/INx mode)  Output 3 low-side driving input (INHx/INLx mode)                                      |

| 12      | INL3/EN3       | Digital in        | Output 3 enable input (EHx/INx mode)                                                                                        |

| 13      | воотз          | Power             | Half-bridge 3 bootstrap voltage                                                                                             |

| 14      | GHS3           | Analog out        | Half-bridge 3 high-side gate driver output                                                                                  |

| 15      | OUT3           | Power             | Half-bridge 3 high-side (floating) common voltage                                                                           |

| 16      | GLS3           | Analog out        | Half-bridge 3 low-side gate driver output                                                                                   |

| 17      | BOOT2          | Power             | Half-bridge 2 bootstrap voltage                                                                                             |

| 18      | GHS2           | Analog out        | Half-bridge 2 high-side gate driver output                                                                                  |

| 19      | OUT2           | Power             | Half-bridge 2 high-side (floating) common voltage                                                                           |

| 20      | GLS2           | Analog out        | Half-bridge 2 low-side gate driver output                                                                                   |

| 21      | BOOT1          | Power             | Half-bridge 1 bootstrap voltage                                                                                             |

| 22      | GHS1           | Analog out        | Half-bridge 1 high-side gate driver output                                                                                  |

| 23      | OUT1           | Power             | Half-bridge 1 high-side (floating) common voltage                                                                           |

| 24      | GLS1           | Analog out        | Half-bridge 1 low-side gate driver output                                                                                   |

|         | EPAD/GND       | Power             | Ground                                                                                                                      |

DS13472 - Rev 1 page 12/32

### 5 Device description

The STDRIVE101 is a low voltage gate driver for three-phase power stages with integrated linear regulator.

The device supply voltage is applied to VS pin. The VS is also used both as input voltage of 12 V LDO linear regulator and to supply some internal circuitries, including the V<sub>DS</sub> monitoring protection reference voltage for the high-side driver.

The power stage voltage (VM in Figure 1) must be equal or lower than VS voltage. If the VM voltage exceeds the VS voltage, the device is damaged due to the violation of OUT pins absolute maximum rating as reported in Table 1

If a VM voltage lower than VS is used, the  $V_{DS}$  monitoring protection cannot be used (refer to dedicated Section 5.6).

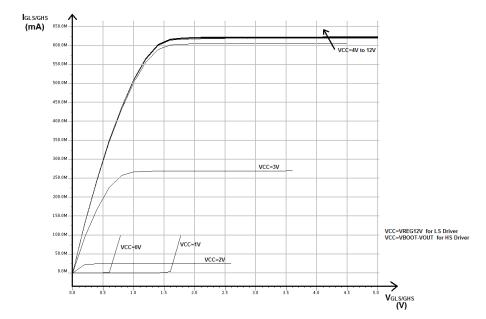

#### 5.1 Gate drivers' characteristics

The STDRIVE101 integrates a triple half-bridge gate driver able to drive N-channel power MOSFETs. The high-side section is supplied by a bootstrapped voltage technique with integrated bootstrap diode.

Figure 8. Gate drivers' outputs characteristics in UVLO conditions

The device is designed to operate using VS as the supply voltage of the external power stage (i.e. motor supply voltage). For this reason, the AMR rating of the OUTx pins is strictly related to the VS value and, more generally, it is not possible to bias the OUT pins when the VS supply is not present (i.e. floating or shorted to ground).

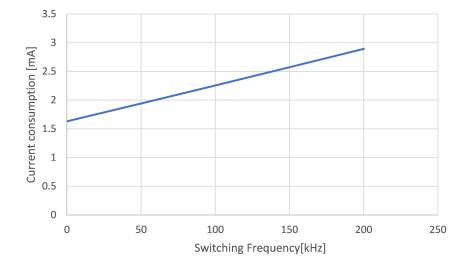

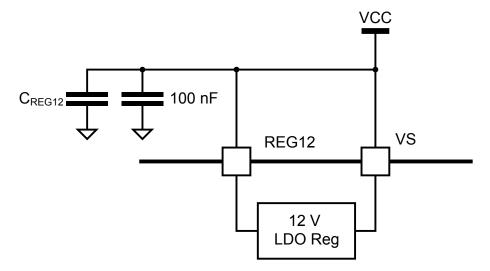

### 5.2 12 V LDO linear regulator

The device integrates a LDO linear regulator generating 12 V output starting from the VS supply. The regulator is disabled during standby mode.

DS13472 - Rev 1 page 13/32

VS 100 nF 220 nF VS REG12 12 V LDO reg

Figure 9. 12 V LDO linear regulator typical configuration

The regulator supplies the gate drivers and can be used to supply small external loads. The average current consumption I<sub>REG12</sub> is given by the internal consumption of the gate drivers, the current provided to the gates of the external MOSFETs and the external load consumption, if any. I<sub>REG12</sub> cannot exceed I<sub>REG12lim</sub>.

The internal consumption of the gate drivers is proportional to the switching frequency and its typical value is reported in Figure 10; this is the overall consumption of the six gate drivers and it is measured without any load connected on the drivers' outputs.

Figure 10. Typical current consumption (driver' outputs unloaded)

On top of this, the current supplied to the external MOSFETs' gates must be considered. The overall gate current I<sub>G.tot</sub> for the six MOSFETs of the power stage can be calculated as:

**Equation 1**

(1)  $I_{G, tot} = 6 \cdot Q_g \cdot f_{SW}$

where  $Q_g$  is the gate charge value of the external MOSFETs, taken at gate voltage equal to  $V_{REG12}$  and  $f_{SW}$  is the switching frequency of the MOSFETs (i.e. the frequency of the PWM signals applied to the drivers).

Another aspect to consider for the maximum current of the linear regulator is the power dissipation. An excessive power dissipation leads to the thermal shutdown of the device (Section 5.8). The total power dissipation of the regulator P<sub>REG12</sub> can be calculated as:

DS13472 - Rev 1 page 14/32

#### **Equation 2**

(2)

$$P_{REG12} = (V_S - V_{REG12}) \cdot I_{REG12}$$

where  $V_S$  is the voltage supply of the STDRIVE101,  $V_{REG12}$  is the regulator output voltage and  $I_{REG12}$  is the average current consumption described previously.

Note: The size of the external power MOSFETs and the switching frequency increase the gate driver's consumption, thus reducing the current availability for external loads.

In addition to the average value  $I_{REG12}$  dynamic contributions must be considered: these are the currents needed to charge the bootstrap capacitors, e.g. after the high-side MOSFET is kept on for a considerable amount of time or after leaving the stand-by condition. In these cases, the amount of current is higher than  $I_{REG12lim}$ , so it is mainly provided by the bypass capacitor  $C_{REG12}$  connected to REG12 pin. In this situation, a voltage drop  $\Delta V_{REG12}$  occurs on REG12, while the LDO maximum current  $I_{REG12lim}$  mainly recharges  $C_{REG12}$ . During this recharge time ( $t_{charge,REG12}$  expressed in Equation 3), the availability of current for external loads is reduced.

#### **Equation 3**

(3)

$$t_{charge, REG12} > C_{REG} \frac{\Delta V_{REG12}}{I_{REG12lim}}$$

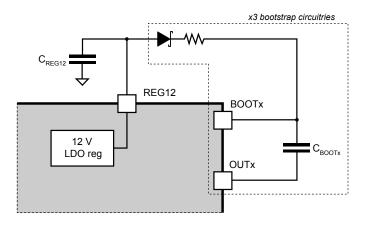

#### 5.2.1 Bootstrap section

The bootstrap circuitry allows to generate a voltage higher than the supply VS and it is used to supply the high-side drivers. When one high-side MOSFET is turned on, its source voltage (OUTx pin) increases up to VS. Therefore, the gate must be driven at a voltage higher than VS. The bootstrap capacitor is referred to the OUTx pin:

- When the OUTx pin is forced to GND (i.e. the respective low-side MOSFET is on), the bootstrap capacitor is charged through the bootstrap diode.

- When the OUTx is forced to VS (i.e. the respective high-side MOSFET is on), the bootstrap capacitor supplies the respective high-side driver and discharges.

The voltage drop on the bootstrap capacitors corresponds to the supply of the high-side drivers. Each bootstrap capacitor must be charged after the corresponding high-side is turned on, otherwise its voltage falls below the  $V_{BO(On)}$  -  $V_{BO(Hyst)}$  threshold, causing the turning off of the respective driver (Section 5.5). A limitation in a bootstrap architecture is that the high-side MOSFET cannot be kept on for an indefinite amount of time. In fact, when the high-side is on, the respective bootstrap capacitor starts discharging. If not recharged, the bootstrap capacitor voltage falls below the  $V_{BO(On)}$  -  $V_{BO(Hyst)}$  (i.e. the UVLO on BOOTx pin). For this reason, working at 100% duty cycle is possible, but only for a limited number of PWM periods. The bigger the bootstrap capacitor, the longer the time the high-side MOSFET can be kept on.

To avoid excessive drop on the REG12 pin, a proper bypass capacitor is required. Even using an external supply connected to the REG12 pin, it is important to have a bypass capacitor with low ESR providing fast current transients when required by the bootstrap capacitors.

The bypass capacitor on REG12 pin must provide the charge for the three bootstrap capacitors: the bigger the bootstrap capacitors are, the bigger should be the REG12 capacitor (refer to Equation 4 in Section 5.2.1.2).

### 5.2.1.1 Power-up and wake-up

During the power-up or after leaving the standby condition, there may be no charge in bootstrap capacitors. In these cases, the drivers cannot start immediately with normal operation, but the bootstrap capacitor should be charged turning on the low-side MOSFET. At the beginning of this procedure, a large amount of current could be required. If the internal 12 V LDO regulator is used, its current is limited at  $I_{REG12lim}$  (Section 5.2).

### 5.2.1.2 Charging time and external bootstrap diodes

The charging time required to charge the bootstrap capacitors depends on their value but also on the resistance of the bootstrap diode (R<sub>DS\_diode</sub>), which limits the current flow. In order to reduce the minimum time for bootstrap recharge (i.e. the minimum time the low-side MOSFET must be on), external bootstrap diodes can be used as shown in Figure 11.

DS13472 - Rev 1 page 15/32

Each diode is in parallel with the corresponding internal bootstrap diode. An external series resistor, smaller than  $R_{DS\_diode}$ , can be still used together with each diode to reduce the maximum charging current and helps to limit the voltage drop on the REG12 pin. The maximum drop on the  $C_{REG12}$  capacitor occurs when the three bootstrap capacitors must be recharged and no series resistor is used with the external diodes. This drop can be approximated as:

#### **Equation 4**

$\Delta V_{CREG12} \approx V_{REG12} \cdot \frac{3 \cdot C_{BOOT}}{C_{REG12} + 3 \cdot C_{BOOT}} \tag{4}$

Figure 11. External bootstrap diode configuration

#### 5.2.2 Externally provided gate driver's supply voltage

It is possible to provide externally the supply voltage for the gate driving circuitry directly, bypassing the integrated regulator and shorting VS and REG12 pins together.

Important: Using this configuration the consumption is partially reduced in standby mode.

Figure 12. 12 V LDO supply voltage externally provided

DS13472 - Rev 1 page 16/32

### 5.3 Control logic

The device integrates a control logic providing two input strategies. The driving method is selected according to DT/MODE pin status:

- DT/MODE connected to the ground through an R<sub>DT</sub> resistor: digital inputs provide enable and input lines for each half-bridge and an internal deadtime is generated according to R<sub>DT</sub> value (ENx/INx mode).

- DT/MODE shorted to ground: digital inputs provide high and low-side driving lines for each half-bridge, no deadtime is internally generated (INHx/INLx mode). In any case, the high and low-side outputs of same half-bridge cannot be simultaneously driven high because of the integrated interlocking function.

#### Note: The DT/MODE pin status must not be changed during device operation.

All the input lines have an internal pull-down to guarantee the low logic level even if no driving input is present.

INxL **INxH GHS**x **GHL**x 'x' Half-bridge condition ī ī ī ī Disabled L Н Low-side on Н L Н L High-side on Н Н L L Disabled (interlocking)

Table 7. INxL and INxH inputs truth table

| Table 8. ENx and INx inputs truth table | h table | truth | puts | ini | <b>INx</b> | and | <b>EN</b> x | 8. | <b>Table</b> |  |

|-----------------------------------------|---------|-------|------|-----|------------|-----|-------------|----|--------------|--|

|-----------------------------------------|---------|-------|------|-----|------------|-----|-------------|----|--------------|--|

| ENx | INx | GHSx | GLSx | 'x' Half-bridge condition |

|-----|-----|------|------|---------------------------|

| L   | X   | L    | L    | Disabled                  |

| Н   | L   | L    | Н    | Low-side on               |

| Н   | Н   | Н    | L    | High-side on              |

Note: X: don't care

#### 5.3.1 Deadtime

When the DT/MODE pin is connected to the ground through an  $R_{DT}$  resistor (ENx/INx mode selected), the device internally generates a deadtime between the MOSFET turn-off and the turn-on of the opposite one.

Input pulses shorter than the deadtime cause an immediate turn on of the gate driver, back to the former status as shown in Figure 13.

DS13472 - Rev 1 page 17/32

(5)

Figure 13. Deadtime management for short pulses

Note:

(1) this propagation delay is typically 16 ns longer than the one measured in INH/INL driving mode (testing condition).

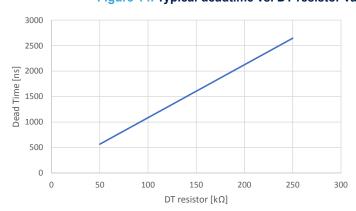

The deadtime depends on the R<sub>DT</sub> value according to the following equation:

#### **Equation 5**

$$R_{DT}[k\Omega] = 96.15 \cdot DT [\mu s] - 4.45$$

The equation is valid only with  $R_{DT}$  value ranging from 50  $k\Omega$  to 250  $k\Omega.$

Figure 14. Typical deadtime vs. DT resistor value

Note: If DT/MODE pin is left floating, the resulting deadtime is about 1  $\mu$ s (typical at  $T_J$  = 25°C). However, it should not be considered an operative condition. If the DT/MODE pin is shorted to ground, the device operates in INHx/INLx mode.

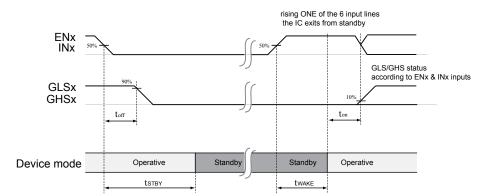

### 5.4 Standby mode

The STDRIVE101 provides a standby mode to reduce power consumption, in particular:

- · All the outputs driver forced low (external power switches turned off)

- The overcurrent comparator is disabled

- TheV<sub>DS</sub> monitoring protection is disabled

- · The UVLO protection is disabled

- The 12 V LDO linear regulator is switched off

DS13472 - Rev 1 page 18/32

Important: If the 12 V regulator is bypassed, the consumption in standby mode is not reduced.

The device enters standby mode keeping low all the driving input pins (INx/INHx and ENx/INLx) for at least t<sub>STBY</sub> time. At power-up, if all the driving inputs are low, the device is immediately set in standby condition. The device leaves standby mode after a t<sub>WAKE</sub> time after at least one of the logic inputs is set high (refer to Figure 15 and Figure 16). Considering the standby condition disables the 12 V regulator, the device returns operative only after the REG12 voltage returns above the UVLO turn-on threshold. When the device exits from standby condition, the bootstrap capacitors charge via low-side turn-on is required, as described in Section 5.2.1.1

Figure 15. Standby and wake-up time (ENx/INx mode, with  $V_S = V_{REG12} = 12 \text{ V}$ )

Figure 16. Standby and wake-up time (INHx/INLx mode, with  $V_S = V_{REG12} = 12 \text{ V}$ )

### 5.5 Undervoltage protection

The device provides UVLO protections on each power supply.

During power-up (see Figure 17), the device leaves the UVLO condition when the respective supply voltage rises above the turn-on threshold. When the supply voltage is below the on-threshold voltage of a hysteresis, the UVLO condition is set.

Table 9 summarizes which blocks are switched off in UVLO condition.

Table 9. UVLO and OT protection management

| Block                    | VREG12 UVLO        | VBOOTx UVLO            |

|--------------------------|--------------------|------------------------|

| HSU, HSV, HSW output     | LOW <sup>(1)</sup> | LOW <sup>(1)</sup> (2) |

| LSU, LSV, LSW output     | LOW <sup>(1)</sup> |                        |

| nFAULT open-drain output | LOW                | OPEN                   |

DS13472 - Rev 1 page 19/32

- 1. The N-channel of the gate driver is turned ON with all the available supply voltage, refer to Figure 8.

- 2. Each high-side gate driver provides independent UVLO protection (e.g. UVLO on BOOTU causes the HSU to turn off only).

Figure 17. Power-up sequence, internal 12 V regulator used

DS13472 - Rev 1 page 20/32

When the REG12 pin is supplied externally, the internal regulator is disabled. When leaving the standby condition raising one of the digital inputs, the nFAULT pin goes low, even if there is no UVLO condition on the REG12 pin, as shown in Figure 18

Figure 18. Power-up sequence, external supply on REG12 pin

### 5.6 V<sub>DS</sub> monitoring protection

The device monitors the  $V_{DS}$  of the power stage's MOSFETs in order to detect anomalous conditions. The  $V_{DS}$  of each MOSFET is compared to a reference threshold ( $V_{DSth}$ ).

The reference threshold is generated according to the voltage applied to the SCREF pin:

#### **Equation 6**

$V_{DSth} = V_{SCREF} \tag{6}$

The SCREF voltage must be in the range between 0.2 V to V<sub>SCREF,en</sub>.

If the voltage is above V<sub>SCREF,dis</sub>, the protection is disabled.

When enabled, the protection triggers one of the following conditions occur:

GLSx output is high and V<sub>OUTx</sub> > V<sub>DSth</sub> for more than t<sub>DFSC</sub>

DS13472 - Rev 1 page 21/32

GHSx output is high and (V<sub>S</sub> - V<sub>OUTx</sub>) > V<sub>DSth</sub> for more than t<sub>DFSC</sub>

#### Important:

The  $V_{DS}$  monitoring is implemented assuming that the supply of the power stage (VM) is at the same voltage of the STDRIVE101 supply (VS). Supplying the power stage with a voltage VM lower than VS the  $V_{DS}$  monitoring protection could not work properly. In particular, if the voltage difference 'VS - VM' is greater than  $V_{DSth}$ , the protection will be triggered each time the high-side is turned on, regardless of the current flowing in the MOSFET.

For this reason it is recommended, when using the  $V_{DS}$  monitoring protection to supply the STDRIVE101 (VS) and the power stage (VM) at the same voltage. In case it is required to use a VM voltage lower than VS, the  $V_{DS}$  monitoring protection must be disabled setting the SCREF pin above the  $V_{SCREF,dis}$  voltage.

As soon as the protection is triggered, all the gate drivers outputs are forced low, the nFAULT output is forced low and the protection is latched. In this condition all the gate driver outputs are kept low whatever the driving inputs (refer to Figure 6).

The protection is released only when the device enters standby mode.

Note: SCREF pins structure does not allow a bias without VS supply voltage.

### 5.7 Overcurrent comparator

The STDRIVE101 embeds a comparator suitable for overcurrent detection of the power stage through a shunt resistor.

When the input voltage at CP pin is higher than internal reference voltage ( $V_{REF}$ ), the device enters into a protection state: all the gate driver outputs are forced low and the nFAULT open drain output is forced low. The device automatically leaves the protection state after a  $t_{DISABLE}$  time (refer to Figure 5 for details).

#### 5.8 Thermal protection

The device embeds an overtemperature shutdown protection through thermal sensor placed next to the linear regulator block.

When the overtemperature protection occurs, the linear regulator is switched off and the nFAULT output is forced low. The thermal shutdown condition expires when the temperature goes below the "T<sub>SD</sub>- T<sub>SDhys</sub>" temperature (auto-restart).

Figure 19. Thermal shutdown management

DS13472 - Rev 1 page 22/32

# 6 ESD protection strategy

Deficient /O (RMS,MIL, JML2, JML2)

OF, MODE of participation of the control of t

Figure 20. ESD protection strategy

DS13472 - Rev 1 page 23/32

## 7 Application example

Figure 21 shows an application example using the STDRIVE101 to drive a three-phase motor with triple shunt configuration.

Value Name  $\mathsf{C}_\mathsf{S}$ 100 nF / 100 V 120 μF / 100 V **C**SPOL  $\mathsf{C}_{\mathsf{REG}}$ 100 nF / 25 V  $4.7 \, \mu F / 25 \, V$ C<sub>REGPOL</sub>  $R_{DT}$  $50~\text{k}\Omega~(t_{DT}\cong\!570~\text{ns})$ R<sub>SC1</sub>  $18 k\Omega$ R<sub>SC2</sub>  $10 \ k\Omega$  $39 k\Omega$ **R**FAULT  $R_{S1}, R_{S2}, R_{S3}$ Values according to application requirements  $R_{SNS1},\,R_{SNS2},\,R_{SNS3}$ Values according to application requirements  $\mathsf{C}_\mathsf{CP}$ 2.2 nF / 16 V  $\mathsf{R}_\mathsf{CP}$ Values according to application requirements

Table 10. Typical application values (V<sub>DD</sub> = 3.3 V)

The others features implemented are:

- V<sub>DS</sub> monitoring protection with SCREF = 1.2 V (V<sub>DD</sub> = 3.3 V)

- Overcurrent protection with internal comparator (CP pin)

V<sub>SCHEF</sub>

V<sub>SCHEF</sub>

Rest

SCREEF

Rest

NAJBNH3

Figure 21. Typical application schematic

DS13472 - Rev 1 page 24/32

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

Figure 22. VFQFPN 4x4x1.0 24 PITCH 0.5 package outline

DS13472 - Rev 1 page 25/32

Table 11. VFQFPN 4x4x1.0 24 PITCH 0.5 package mechanical data

| Symbol | Dimensions (mm) |      |      |  |

|--------|-----------------|------|------|--|

| Symbol | Min.            | Тур. | Max. |  |

| Α      | 0.80            | 0.90 | 1.00 |  |

| A1     | 0.00            | 0.02 | 0.05 |  |

| А3     |                 | 0.20 |      |  |

| b      | 0.18            | 0.25 | 0.30 |  |

| D      | 3.85            | 4.00 | 4.15 |  |

| D2     | 2.40            | 2.50 | 2.60 |  |

| E      | 3.85            | 4.00 | 4.15 |  |

| E2     | 2.40            | 2.50 | 2.60 |  |

| е      |                 | 0.50 |      |  |

| L      | 0.30            | 0.40 | 0.50 |  |

| ddd    |                 |      | 0.08 |  |

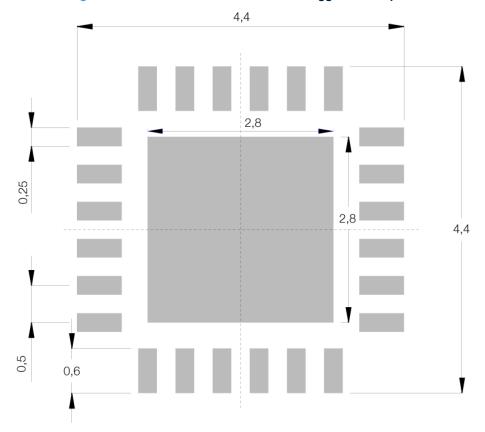

Figure 23. VFQFPN 4x4x1.0 24 PITCH 0.5 suggested footprint

DS13472 - Rev 1 page 26/32

# 9 Ordering information

Table 12. Device summary

| Order code   | Package                     | Packaging   |

|--------------|-----------------------------|-------------|

| STDRIVE101   | VFQFPN 4x4x1.0 24 PITCH 0.5 | Tube        |

| STDRIVE101TR | VFQFPN 4x4x1.0 24 PITCH 0.5 | Tape & Reel |

DS13472 - Rev 1 page 27/32

## **Revision history**

Table 13. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 26-Oct-2020 | 1       | Initial release. |

DS13472 - Rev 1 page 28/32

## **Contents**

| 1   | Block   | ck diagram                                             | 2             |  |

|-----|---------|--------------------------------------------------------|---------------|--|

| 2   | Elect   | etrical data                                           |               |  |

|     | 2.1     | Absolute maximum ratings                               | 3             |  |

|     | 2.2     | Recommended operating conditions                       | 4             |  |

|     | 2.3     | Thermal data                                           | 5             |  |

|     | 2.4     | Electrical sensitivity characteristics                 | 5             |  |

| 3   | Elect   | etrical characteristics                                | 6             |  |

| 4   | Pin d   | description                                            | 11            |  |

| 5   | Devi    | ice description                                        | 13            |  |

|     | 5.1     | Gate drivers' characteristics                          | 13            |  |

|     | 5.2     | 12 V LDO linear regulator                              | 13            |  |

|     |         | 5.2.1 Bootstrap section                                | 15            |  |

|     |         | 5.2.2 Externally provided gate driver's supply voltage | 16            |  |

|     | 5.3     | Control logic                                          | 17            |  |

|     |         | <b>5.3.1</b> Deadtime                                  | 17            |  |

|     | 5.4     | Standby mode                                           | 18            |  |

|     | 5.5     | Undervoltage protection                                | 19            |  |

|     | 5.6     | V <sub>DS</sub> monitoring protection                  | 21            |  |

|     | 5.7     | Overcurrent comparator                                 | 22            |  |

|     | 5.8     | Thermal protection                                     | 22            |  |

| 6   | ESD     | protection strategy                                    | 23            |  |

| 7   | Appli   | lication example                                       | 24            |  |

| 8   | Pack    | kage information                                       | 25            |  |

| 9   | Orde    | ering information                                      | 27            |  |

| Rev | ision h | history                                                | 28            |  |

|     |         | · · · · · · · · · · · · · · · · · · ·                  |               |  |

|     |         | bles                                                   |               |  |

|     |         | gures                                                  |               |  |

|     | ~       | y                                                      | · · · · · · · |  |

## **List of tables**

| Table 1.  | Absolute maximum ratings                             | . చ |

|-----------|------------------------------------------------------|-----|

| Table 2.  | Recommended operating conditions                     | . 4 |

| Table 3.  | Thermal data                                         |     |

| Table 4.  | ESD protection ratings                               | . 5 |

| Table 5.  | Electrical characteristics                           | . 6 |

| Table 6.  | STDRIVE101 pin description                           |     |

| Table 7.  | INxL and INxH inputs truth table                     |     |

| Table 8.  | ENx and INx inputs truth table                       | 17  |

| Table 9.  | UVLO and OT protection management                    | 19  |

| Table 10. | Typical application values (V <sub>DD</sub> = 3.3 V) | 24  |

| Table 11. | VFQFPN 4x4x1.0 24 PITCH 0.5 package mechanical data  | 26  |

| Table 12. | Device summary                                       | 27  |

| Table 13. | Document revision history                            | 28  |

|           |                                                      |     |

# **List of figures**

| Figure 3.ENx timings (ENx/INx mode)9Figure 4.INHx and INLx timings (INHx/INLx mode)10Figure 5.Overcurrent comparator timings10Figure 6. $V_{DS}$ monitoring protection timing.10Figure 7.STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view)11Figure 8.Gate drivers' outputs characteristics in UVLO conditions13Figure 9.12 V LDO linear regulator typical configuration14Figure 10.Typical current consumption (driver' outputs unloaded)14Figure 11.External bootstrap diode configuration16Figure 12.12 V LDO supply voltage externally provided16Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25 | Figure 1.  | STDRIVE101 block diagram                                                                   | . 2 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------|-----|

| Figure 4.INHx and INLx timings (INHx/INLx mode).10Figure 5.Overcurrent comparator timings.10Figure 6. $V_{DS}$ monitoring protection timing.10Figure 7.STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view).11Figure 8.Gate drivers' outputs characteristics in UVLO conditions.13Figure 9.12 V LDO linear regulator typical configuration.14Figure 10.Typical current consumption (driver' outputs unloaded).14Figure 11.External bootstrap diode configuration.16Figure 12.12 V LDO supply voltage externally provided.16Figure 13.Deadtime management for short pulses.18Figure 14.Typical deadtime vs. DT resistor value.18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ ).19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ ).19Figure 17.Power-up sequence, internal 12 V regulator used.20Figure 18.Power-up sequence, external supply on REG12 pin.21Figure 19.Thermal shutdown management.22Figure 20.ESD protection strategy.23Figure 21.Typical application schematic.24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline.25                   | Figure 2.  | INx timings and deadtime (ENx/INx mode)                                                    | . 9 |

| Figure 4.INHx and INLx timings (INHx/INLx mode).10Figure 5.Overcurrent comparator timings.10Figure 6. $V_{DS}$ monitoring protection timing.10Figure 7.STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view).11Figure 8.Gate drivers' outputs characteristics in UVLO conditions.13Figure 9.12 V LDO linear regulator typical configuration.14Figure 10.Typical current consumption (driver' outputs unloaded).14Figure 11.External bootstrap diode configuration.16Figure 12.12 V LDO supply voltage externally provided.16Figure 13.Deadtime management for short pulses.18Figure 14.Typical deadtime vs. DT resistor value.18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ ).19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ ).19Figure 17.Power-up sequence, internal 12 V regulator used.20Figure 18.Power-up sequence, external supply on REG12 pin.21Figure 19.Thermal shutdown management.22Figure 20.ESD protection strategy.23Figure 21.Typical application schematic.24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline.25                   | Figure 3.  | ENx timings (ENx/INx mode)                                                                 | . 9 |

| Figure 6. V <sub>DS</sub> monitoring protection timing. 10  Figure 7. STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view) 11  Figure 8. Gate drivers' outputs characteristics in UVLO conditions 13  Figure 9. 12 V LDO linear regulator typical configuration 14  Figure 10. Typical current consumption (driver' outputs unloaded) 14  Figure 11. External bootstrap diode configuration 16  Figure 12. 12 V LDO supply voltage externally provided 16  Figure 13. Deadtime management for short pulses 18  Figure 14. Typical deadtime vs. DT resistor value 18  Figure 15. Standby and wake-up time (ENx/INx mode, with V <sub>S</sub> = V <sub>REG12</sub> = 12 V) 19  Figure 16. Standby and wake-up time (INHx/INLx mode, with V <sub>S</sub> = V <sub>REG12</sub> = 12 V) 19  Figure 17. Power-up sequence, internal 12 V regulator used 20  Figure 18. Power-up sequence, external supply on REG12 pin 21  Figure 20. ESD protection strategy 23  Figure 21. Typical application schematic 24  VFQFPN 4x4x1.0 24 PITCH 0.5 package outline 25                                                                                           | Figure 4.  |                                                                                            |     |

| Figure 7.STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view).11Figure 8.Gate drivers' outputs characteristics in UVLO conditions.13Figure 9.12 V LDO linear regulator typical configuration.14Figure 10.Typical current consumption (driver' outputs unloaded).14Figure 11.External bootstrap diode configuration.16Figure 12.12 V LDO supply voltage externally provided.16Figure 13.Deadtime management for short pulses.18Figure 14.Typical deadtime vs. DT resistor value.18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ ).19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ ).19Figure 17.Power-up sequence, internal 12 V regulator used.20Figure 18.Power-up sequence, external supply on REG12 pin.21Figure 19.Thermal shutdown management.22Figure 20.ESD protection strategy.23Figure 21.Typical application schematic.24VFQFPN 4x4x1.0 24 PITCH 0.5 package outline.25                                                                                                                                                                           | Figure 5.  | Overcurrent comparator timings                                                             | 10  |

| Figure 8.Gate drivers' outputs characteristics in UVLO conditions13Figure 9.12 V LDO linear regulator typical configuration14Figure 10.Typical current consumption (driver' outputs unloaded)14Figure 11.External bootstrap diode configuration16Figure 12.12 V LDO supply voltage externally provided16Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25                                                                                                                                                                                                                                                                          | Figure 6.  | V <sub>DS</sub> monitoring protection timing                                               | 10  |

| Figure 9.12 V LDO linear regulator typical configuration14Figure 10.Typical current consumption (driver' outputs unloaded)14Figure 11.External bootstrap diode configuration16Figure 12.12 V LDO supply voltage externally provided16Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with V <sub>S</sub> = V <sub>REG12</sub> = 12 V)19Figure 16.Standby and wake-up time (INHx/INLx mode, with V <sub>S</sub> = V <sub>REG12</sub> = 12 V)19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25                                                                                                                                                                                                                                                                                                                 | Figure 7.  | STDRIVE101 pin connection in QFN 4x4 24L with exposed PAD (Top view)                       | 11  |

| Figure 10.Typical current consumption (driver' outputs unloaded)14Figure 11.External bootstrap diode configuration16Figure 12.12 V LDO supply voltage externally provided16Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with Vs = VREG12 = 12 V)19Figure 16.Standby and wake-up time (INHx/INLx mode, with Vs = VREG12 = 12 V)19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 8.  | Gate drivers' outputs characteristics in UVLO conditions                                   | 13  |

| Figure 11.External bootstrap diode configuration16Figure 12.12 V LDO supply voltage externally provided16Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with Vs = VREG12 = 12 V)19Figure 16.Standby and wake-up time (INHx/INLx mode, with Vs = VREG12 = 12 V)19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 9.  | 12 V LDO linear regulator typical configuration                                            | 14  |

| Figure 12. $12 \text{ V LDO}$ supply voltage externally provided16Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 10. | Typical current consumption (driver' outputs unloaded)                                     | 14  |

| Figure 13.Deadtime management for short pulses18Figure 14.Typical deadtime vs. DT resistor value18Figure 15.Standby and wake-up time (ENx/INx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 16.Standby and wake-up time (INHx/INLx mode, with $V_S = V_{REG12} = 12 \text{ V}$ )19Figure 17.Power-up sequence, internal 12 V regulator used20Figure 18.Power-up sequence, external supply on REG12 pin21Figure 19.Thermal shutdown management22Figure 20.ESD protection strategy23Figure 21.Typical application schematic24Figure 22.VFQFPN 4x4x1.0 24 PITCH 0.5 package outline25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 11. | External bootstrap diode configuration                                                     | 16  |