# L7292

### Five buck regulators power management unit

#### **Datasheet - production data**

### **Features**

- Key specification

- Vin range from 2.7 V to 5.5 V

- Interface

- Two-wire I<sup>2</sup>C serial interface supports 3.4-Mbit protocol (high speed mode)

- 8-bit register bank

- Random and Sequential Read modes

- Automatic address incrementing

- Programmable buck regulators

- Regulators with programmable DC set point and soft-start

- Buck regulators include integrated PMOS and NMOS switching elements

- Up to 90% efficiency

- PWM and PFM modes

- Two pins to select four sets of DC voltages

- ± 1% feedback voltage accuracy

- All regulators with auto discharge function on reset.

- Programmable bucks

- Support functions

- 128-bit EEPROM for:

- Default Vout

- Power up sequence

- Reset IC delay time

- Regulator enable

- Integrated voltage monitor with digital filters

- Thermal protection

- Package: VQFN 5 x 5 x 0.9 40L

#### May 2016

#### DocID028601 Rev 2

This is information on a product in full production.

# Applications

• SSD (Solid-State Drive), portable phone, etc.

### Description

The L7292 is a power management device designed for consumer applications. Five bucks provide voltages for the µController and Flash memory with efficiency up to 90% in light-load condition.

The device communicates with the  $\mu$ Controller via an I<sup>2</sup>C serial interface operating at clock speeds up to 3.4 Mbit/s.

The regulators operate at 1.3 MHz switching frequency and enter automatically in the PFM operation to maintain high efficiency over the entire load current range.

The device can be forced into the PWM mode by writing a bit in the serial port register.

Low quiescent current (e.g.: All SW reg. ON with no load Iq =  $175 \mu A$ ).

The L7292 device has a DSM mode to reduce the quiescent current at the minimum value (1 x SW reg. ON with no load Iq =  $60 \mu$ A).

| Tahlo | 1 | Dovico | summary |

|-------|---|--------|---------|

| Table |   | Device | Summary |

| Regulator | Vout range [V] | DC lload [A] |

|-----------|----------------|--------------|

| BUCK1     | 0.9 - 1.6      | 1.0          |

| BUCK2     | 1.5 - 2.1      | 0.8          |

| BUCK3     | 0.7 - 1.3      | 0.5          |

| BUCK4     | 0.7 - 1.3      | 1.0          |

| BUCK5     | 0.7 - 1.3      | 1.6          |

# Contents

| 1 |                    | <b>6</b> x 5 x 0.9 40L package                  |  |  |  |

|---|--------------------|-------------------------------------------------|--|--|--|

| 2 | Pin o              | Pin description                                 |  |  |  |

| 3 | Турі               | cal application                                 |  |  |  |

| 4 | Abso               | olute maximum ratings 11                        |  |  |  |

| 5 | Elec               | trical characteristics                          |  |  |  |

|   | 5.1                | Recommended operating conditions                |  |  |  |

|   | 5.2                | Bias DC characteristics                         |  |  |  |

|   | 5.3                | Interface                                       |  |  |  |

|   |                    | 5.3.1 I <sup>2</sup> C electrical specification |  |  |  |

|   |                    | 5.3.2 MODA, MODB                                |  |  |  |

|   | 5.4                | EEPROM                                          |  |  |  |

|   | 5.5                | Voltage monitor and POR generator               |  |  |  |

| 6 | Volta              | age regulators                                  |  |  |  |

|   | 6.1                | BUCK1 switching regulator 15                    |  |  |  |

|   | 6.2                | BUCK2 switching regulator 16                    |  |  |  |

|   | 6.3                | BUCK3 switching regulator 17                    |  |  |  |

|   | 6.4                | BUCK4 switching regulator 18                    |  |  |  |

|   | 6.5                | BUCK5 switching regulator 19                    |  |  |  |

|   | 6.6                | Thermal shutdown                                |  |  |  |

| 7 | Gen                | eral description                                |  |  |  |

| 8 | I <sup>2</sup> C i | nterface                                        |  |  |  |

|   | 8.1                | Description                                     |  |  |  |

|   | 8.2                | Signal description                              |  |  |  |

|   |                    | 8.2.1 Serial clock (SCL)                        |  |  |  |

|   |                    | 8.2.2 Serial data (SDA)                         |  |  |  |

|   |                    |                                                 |  |  |  |

| 8.3 | I <sup>2</sup> C dev | vice operation                                    |

|-----|----------------------|---------------------------------------------------|

|     | 8.3.1                | Start condition                                   |

|     | 8.3.2                | Stop condition                                    |

|     | 8.3.3                | Acknowledge bit (ACK)24                           |

|     | 8.3.4                | Data input24                                      |

|     | 8.3.5                | Register bank addressing2                         |

|     | 8.3.6                | Write operations                                  |

|     | 8.3.7                | Byte Write                                        |

|     | 8.3.8                | Sequential Write                                  |

|     | 8.3.9                | Read operations                                   |

|     | 8.3.10               | Random Address Read                               |

|     | 8.3.11               | Current Address Read                              |

|     | 8.3.12               | Sequential Read                                   |

|     | 8.3.13               | Acknowledge in Read mode2                         |

| 8.4 | High sp              | peed mode support                                 |

| _   |                      |                                                   |

|     |                      | p 29                                              |

| 9.1 | Genera               | al overview                                       |

| 9.2 | Detaile              | ed register description                           |

|     | 9.2.1                | PSR1VL.VL - voltage level                         |

|     | 9.2.2                | PSR2VL.VL - voltage level                         |

|     | 9.2.3                | PSR3VL.VL - PSR4VL.VL - PSR5VL.VL - voltage level |

|     | 9.2.4                | PSRxLV.PSRxLVEN - voltage level selection enable  |

|     | 9.2.5                | PSRxLV.PSRxOCDIS - overcurrent disable            |

|     | 9.2.6                | PSRxCFG.PFMDIS - PFM disable                      |

|     | 9.2.7                | YYYxCFG.ORDER - order in power up sequence        |

|     | 9.2.8                | PSRxCFG.RSLEW - driver slew rate                  |

|     | 9.2.9                | PSRxCFG.LSDIS - low side disable                  |

|     | 9.2.10               | YYYxCFG.UVM - mask undervoltage fault             |

|     | 9.2.11               | SEQCFG.DLY2 - Delay 2                             |

|     | 9.2.12               | SEQCFG.DLY1CFG - Delay 1 configuration            |

|     | 9.2.13               | SEQCFG.DLY1 - Delay 1                             |

|     | 9.2.14               | PSCFG.EUVM - external undervoltage mask           |

|     | 9.2.15               | PSCFG.IUVM - internal undervoltage mask           |

|     | 9.2.16               | PSCFG.DEGL - deglitch                             |

|     | 9.2.17               | REGCTRL.DSM - deep sleep mode                     |

|     | 9.2.18               | REGCTRL.LDO pull-down                             |

|     |                      |                                                   |

9

|    |       | 9.2.19 REGCTRL.YYYxDIS - PSRx/LDO disable   |

|----|-------|---------------------------------------------|

|    |       | 9.2.20 SETCTRL.BUSY - busy                  |

|    |       | 9.2.21 SETCTRL.SDI - setting data integrity |

|    |       | 9.2.22 SETCTRL.CMD - command                |

|    |       | 9.2.23 STATUS.YYYxFL - fault                |

| 10 | EEPR  | ОМ                                          |

|    | EEPR  | DM description                              |

| 11 | Buck  | regulator description                       |

|    | 11.1  | MOD selection - pin MODA, MODB              |

|    | 11.2  | VOUT selection                              |

|    | 11.3  | Regulator sequence programmability 41       |

|    | 11.4  | Soft-start                                  |

|    | 11.5  | PWM mode                                    |

|    | 11.6  | PFM mode                                    |

|    | 11.7  | Forced PWM                                  |

|    | 11.8  | Current limiting                            |

|    | 11.9  | Short-circuit protection                    |

|    | 11.10 | Deep sleep mode                             |

|    | 11.11 | Forced pull-down                            |

|    | 11.12 | Voltage monitor                             |

|    | 11.13 | Thermal protection                          |

|    | 11.14 | Fault summary                               |

|    | 11.15 | Noisy immunity improvement                  |

| 12 | Packa | ge information                              |

|    | 12.1  | VQFN 5 x 5 x 0.9 40L package information    |

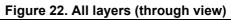

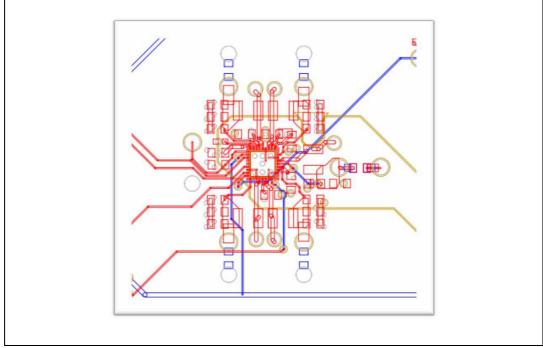

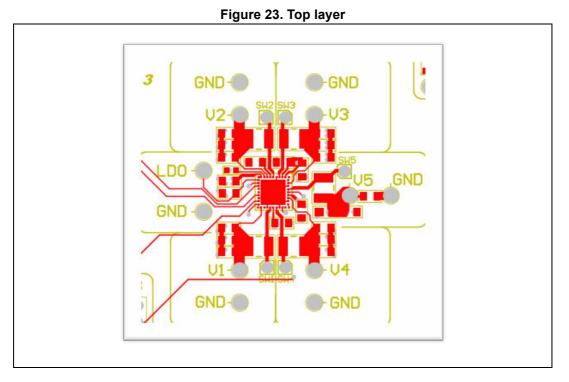

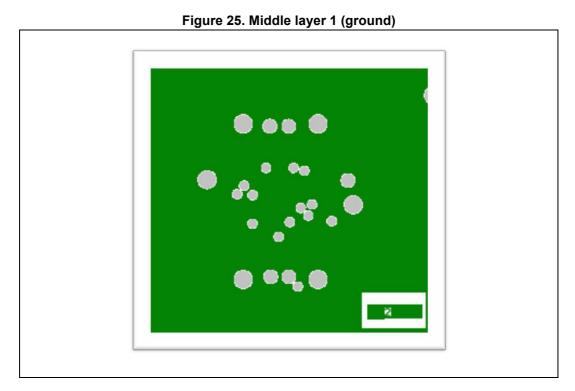

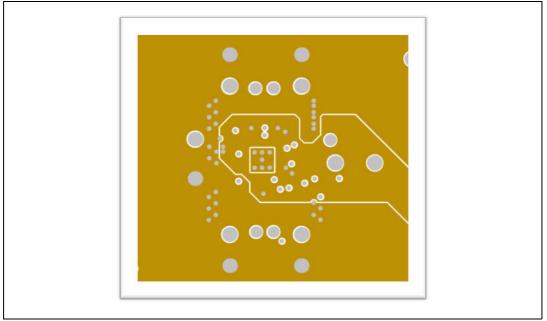

| 13 | PCB o | PCB design rules guideline   |  |  |  |

|----|-------|------------------------------|--|--|--|

|    | 13.1  | Basic principles             |  |  |  |

|    | 13.2  | Layout rules                 |  |  |  |

|    |       | 13.2.1 Supplies              |  |  |  |

|    |       | 13.2.2 Switch node           |  |  |  |

|    |       | 13.2.3 Feedback node         |  |  |  |

|    |       | 13.2.4 Output capacitors     |  |  |  |

|    | 13.3  | PCB layout recommendation 53 |  |  |  |

|    | 13.4  | General rules                |  |  |  |

|    | 13.5  | Thermal aspects              |  |  |  |

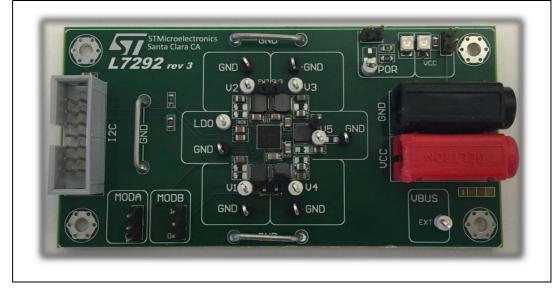

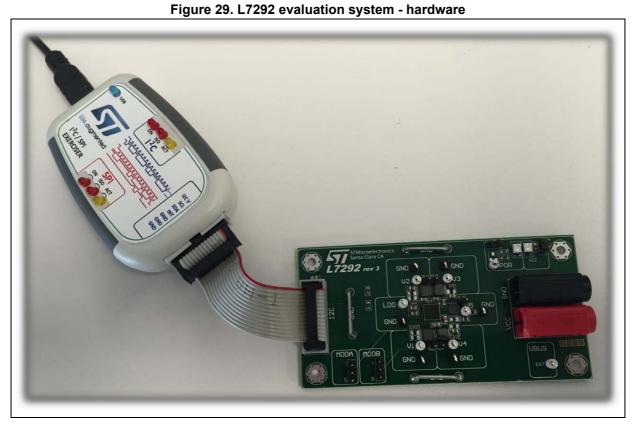

| 14 | Evalu | ation tool                   |  |  |  |

| 15 | Order | <sup>.</sup> codes           |  |  |  |

| 16 | Revis | ion history                  |  |  |  |

#### L7292

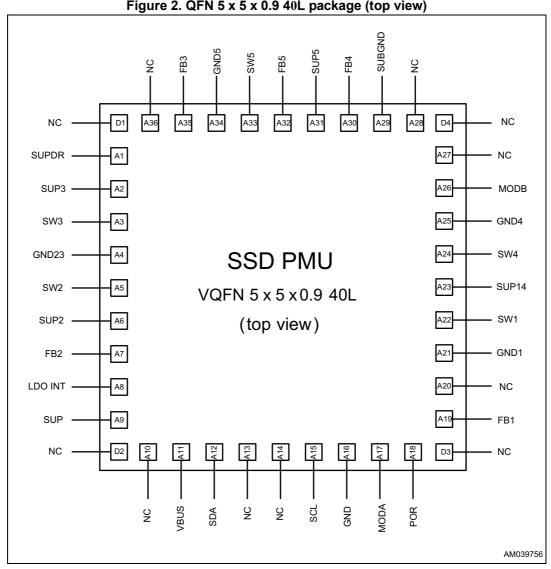

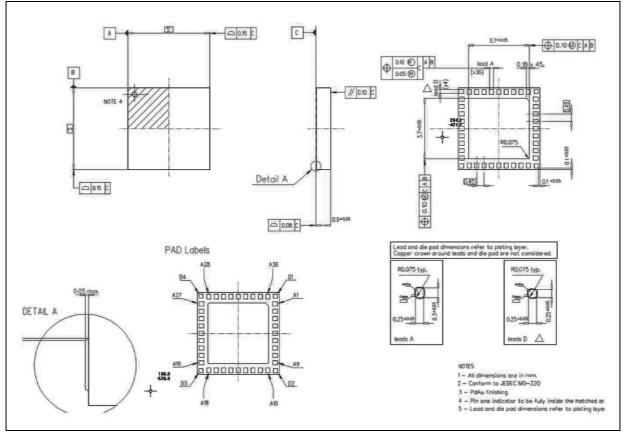

# 1 Package

### QFN 5 x 5 x 0.9 40L package

Figure 2. QFN 5 x 5 x 0.9 40L package (top view)

#### 2 **Pin description**

| Table 2. Pinout |          |      |                                             |  |  |

|-----------------|----------|------|---------------------------------------------|--|--|

| Pin no.         | Pin name | Туре | Description                                 |  |  |

| D1              | NC       |      |                                             |  |  |

| A1              | SUPDR    | Р    | Power supply                                |  |  |

| A2              | SUP3     | Р    | Power supply                                |  |  |

| A3              | SW3      | 0    | BUCK3 regulator switch node                 |  |  |

| A4              | GND23    | G    | BUCK2 and BUCK3 ground                      |  |  |

| A5              | SW2      | 0    | BUCK2 regulator switch node                 |  |  |

| A6              | SUP2     | Р    | BUCK2 power supply                          |  |  |

| A7              | FB2      | I    | BUCK2 regulator feedback                    |  |  |

| A8              | LDO INT  | I    | Supply voltage to internal circuits         |  |  |

| A9              | SUP      | Р    | Power supply                                |  |  |

| D2              | NC       |      |                                             |  |  |

| A10             | NC       |      |                                             |  |  |

| A11             | VBUS     | Р    | Serial port supply                          |  |  |

| A12             | SDA      | I/O  | I <sup>2</sup> C serial data line           |  |  |

| A13             | NC       |      |                                             |  |  |

| A14             | NC       |      |                                             |  |  |

| A15             | SCL      | I    | I <sup>2</sup> C serial clock line          |  |  |

| A16             | GND      | G    | Analog and digital ground                   |  |  |

| A17             | MODA     | Ι    | With MODB pin, SET A, B, C, and D selection |  |  |

| A18             | POR      | 0    | Power-on reset                              |  |  |

| D3              | NC       |      |                                             |  |  |

| A19             | FB1      | Ι    | BUCK1 regulator feedback                    |  |  |

| A20             | NC       |      |                                             |  |  |

| A21             | GND1     | G    | Ground                                      |  |  |

| A22             | SW1      | 0    | BUCK1 regulator switch node                 |  |  |

| A23             | SUP14    | Р    | BUCK1 and BUCK4 power supply                |  |  |

| A24             | SW4      | 0    | BUCK4 regulator switch node                 |  |  |

| A25             | GND4     | G    | BUCK4 ground                                |  |  |

| A26             | MODB     | Ι    | With MODA pin, SET A, B, C, and D selection |  |  |

| A27             | NC       |      |                                             |  |  |

| D4              | NC       |      |                                             |  |  |

| A28             | NC       |      |                                             |  |  |

Table 2 Pinout

| Pin no. | Pin name | Туре | Description                 |  |  |

|---------|----------|------|-----------------------------|--|--|

| A29     | SUBGND   | G    | Substrate ground            |  |  |

| A30     | FB4      | I    | BUCK4 regulator feedback    |  |  |

| A31     | SUP5     | Р    | BUCK5 power supply          |  |  |

| A32     | FB5      | I    | BUCK5 regulator feedback    |  |  |

| A33     | SW5      | 0    | BUCK5 regulator switch node |  |  |

| A34     | GND5     | G    | Ground                      |  |  |

| A35     | FB3      | I    | BUCK3 regulator feedback    |  |  |

| A36     | NC       |      |                             |  |  |

#### Table 2. Pinout (continued)

Note:

$\begin{array}{l} P \rightarrow power \ supply \\ G \rightarrow ground \\ O \rightarrow output \\ l/O \rightarrow input/output \\ l \rightarrow input. \end{array}$

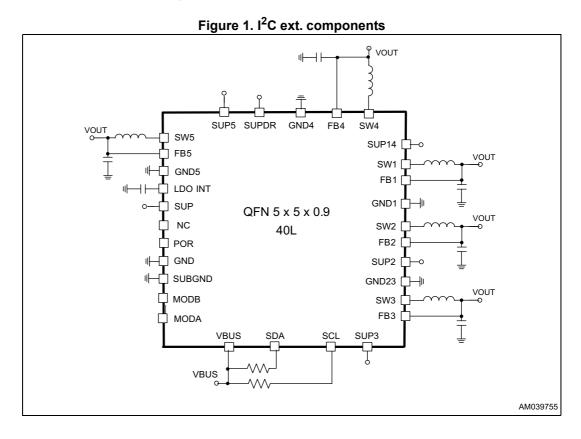

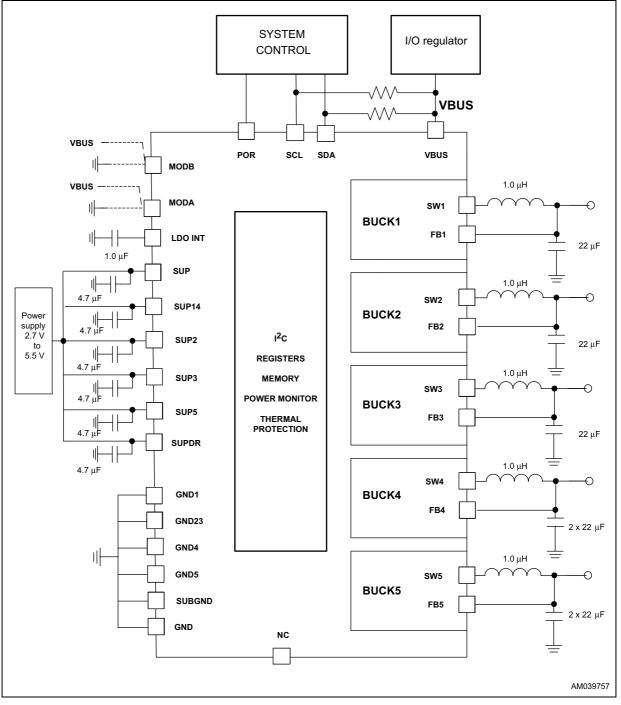

# **3** Typical application

# 4 Absolute maximum ratings

The absolute maximum rating is the maximum stress that can be applied to a device without causing permanent damage. However, extended exposure to maximum ratings may affect long-term device reliability.

| Parameter                               | Rating           |

|-----------------------------------------|------------------|

| SUP, SUP14 - 2 - 3 - 5, SUPDR           | -0.3 V - 7 V     |

| VBUS                                    | -0.3 V - 7 V     |

| SW 1 - 5                                | -0.3 V - 7 V     |

| FB 1 - 5                                | -0.3 V - 4 V     |

| SDA, SCL, POR, MODA, MODB               | -0.3 V - VBUS    |

| LDO INT                                 | -0.3 V - 2.5 V   |

| LDO                                     | -0.3 V - 7 V     |

| Operating ambient temperature           | -30 °C to 85 °C  |

| Operating virtual junction temperature  | 170 °C           |

| Thermal resistance, junction to ambient |                  |

| QFN 5 x 5 x 0.9 40L                     |                  |

| 30 °C/W                                 |                  |

| Storage temperature                     | -55 °C to 150 °C |

| Solder temperature - 10 s duration      | 250 °C           |

| <b>T</b> . I. I | ~ .  |          |         |         |

|-----------------|------|----------|---------|---------|

| lable           | 3. F | ADSOIUTE | maximum | ratings |

# 5 Electrical characteristics

All specifications are for -30 °C <  $T_A$  < 85°C, ALL SUPx = 5 V, VBUS = 3.3 V (≤ VSUP) unless otherwise noted.

## 5.1 Recommended operating conditions

Performance specifications do not apply when the device is operated outside the recommended conditions, unless otherwise indicated.

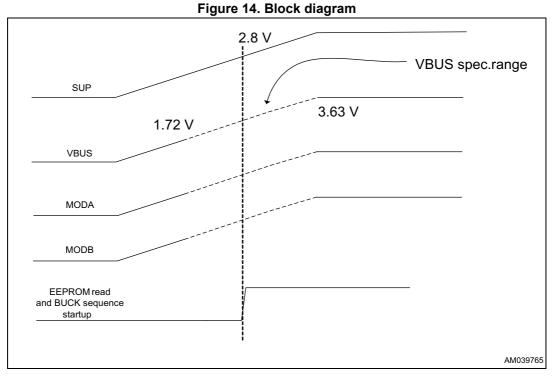

| Parameter                                                                                     | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------|------|------|------|------|

| SUP, SUP14 - 2 - 3 - 5, SUPDR voltage <sup>(1)</sup>                                          | 2.7  |      | 5.5  | V    |

| VBUS voltage                                                                                  | 1.72 |      | 3.63 |      |

| Ambient temperature, T <sub>A</sub>                                                           | -30  |      | 85   | °C   |

| Total power dissipation, with device appropriately mounted <sup>(2)</sup> QFN 5 x 5 x 0.9 40L |      |      | 2.2  | W    |

| Table 4. | Recommended | operating | conditions  |

|----------|-------------|-----------|-------------|

|          | Recommended | operating | contaitions |

1. The "min." value reported is referring to the typical value of undervoltage threshold distribution.

Device mounted on the multilayer PCB with appropriate thermal optimization. If multiple ratings are listed for the same parameter, all apply simultaneously.

### 5.2 Bias DC characteristics

#### Table 5. Bias DC characteristics

| Parameter                                | Conditions                                                                       | Min. | Тур. | Max. | Unit |

|------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| LDO INT output voltage                   | Cout = 1.0 $\mu$ F, Iload = 0                                                    |      | 1.8  |      | V    |

| Deep sleep mode quiescent supply current | VSUP = 5 V<br>REGCTRL bit 7 = 1 BUCK1<br>- 2 - 4 - 5 = OFF<br>BUCK3 = ON no load |      | 60   |      | μΑ   |

| Quiescent supply current                 | VSUP = 5 V<br>REGCTRL bit 7 = 0 BUCK1<br>- 2 - 3 - 4 - 5 = ON no load            |      | 175  |      | μA   |

## 5.3 Interface

# 5.3.1 I<sup>2</sup>C electrical specification

| Parameter                                          | Conditions                      | Min.       | Тур. | Max.       | Unit |

|----------------------------------------------------|---------------------------------|------------|------|------------|------|

| Digital high level input voltage, V <sub>IH</sub>  | SDA, SCL                        | 0.7 * VBUS |      | VBUS + 0.3 | V    |

| Digital low level input voltage, V <sub>IL</sub>   | SDA, SCL                        | -0.3       |      | 0.3 * VBUS | V    |

| Digital low level output voltage, V <sub>OL</sub>  | SDA<br>I <sub>LOAD</sub> = 1 mA | -0.3       |      | 0.3 * VBUS | V    |

| Digital high level output voltage, V <sub>OH</sub> | SDA<br>I <sub>LOAD</sub> = 1 mA | 0.7 * VBUS |      | VBUS + 0.3 | V    |

| Input bias current                                 | SDA, SCL = VBUS                 |            |      | 1          | μA   |

| Input bias current                                 | SDA, SCL = 0 V                  | -1         |      |            | μA   |

| Input capacitance                                  | SDA                             |            |      | 10         | pF   |

| Table 6. I <sup>2</sup> C | electrical | specification |

|---------------------------|------------|---------------|

|---------------------------|------------|---------------|

Note: For others parameters refer to  $I^2C$  bus specifications.

### 5.3.2 MODA, MODB

#### Table 7. MODA, MODB

| Parameter                                  | Conditions | Min.       | Тур. | Max.       | Unit |

|--------------------------------------------|------------|------------|------|------------|------|

| Digital high level input voltage, $V_{IH}$ | MODA, MODB | 0.7 * VBUS |      | VBUS + 0.3 | V    |

| Digital low level input voltage, $V_{IL}$  | MODA, MODB | -0.3       |      | 0.3 * VBUS | V    |

### 5.4 EEPROM

#### Table 8. EEPROM

| Parameter              | Conditions                               | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------------|------|------|------|------|

| Programming time       | 1 page = 8 bytes<br>parallel programming |      |      | 30   | ms   |

| Allowable write cycles |                                          |      |      | 1000 |      |

| Write voltage          |                                          | 2.9  |      |      | V    |

# 5.5 Voltage monitor and POR generator

| Table 9. Voltage monitor and POR generator        |                   |                                              |              |                                            |             |      |  |  |  |

|---------------------------------------------------|-------------------|----------------------------------------------|--------------|--------------------------------------------|-------------|------|--|--|--|

| Parameter                                         |                   | Conditions                                   | Min.         | Тур.                                       | Max.        | Unit |  |  |  |

| Undervoltage threshold rising                     | SUP               | Enable to regulators<br>softstart            | 2.75         | 2.8                                        | 2.9         | V    |  |  |  |

| Undervoltage threshold falling                    | SUP               | POR signal only                              | 2.65         | 2.7                                        | 2.8         |      |  |  |  |

| Undervoltage threshold<br>hysteresis              | SUP               |                                              | 0.05         | 0.1                                        | 0.2         | V    |  |  |  |

| Undervoltage threshold falling                    | BUCK1 ,2, 3, 4, 5 |                                              |              | Vout - 15% <sup>(1)</sup>                  |             |      |  |  |  |

| Regulators disable                                | BUCK1, 2, 3, 4, 5 |                                              | 2.45         | 2.5                                        | 2.6         | V    |  |  |  |

| DLY1<br>POR rising delay                          | PORZ              | 2 ms step<br>programmability                 | -10%         | 8 - 10 - 12 - 14 -16<br>- 18 - 20 -22 - 24 | +10%        | ms   |  |  |  |

| POR low level output<br>voltage, V <sub>OL</sub>  |                   | I <sub>OL</sub> = 1 mA                       |              |                                            | 0.3         | V    |  |  |  |

| POR pull-up                                       | 0007              | Internal pull-up to<br>VBUS -30 °C to 125 °C | 100          | 200                                        | 300         | kΩ   |  |  |  |

| POR high level output<br>voltage, V <sub>OH</sub> | - PORZ            |                                              | 80 %<br>VBUS |                                            |             | V    |  |  |  |

| POR low level output<br>voltage, V <sub>OL</sub>  |                   |                                              |              |                                            | 20%<br>VBUS | V    |  |  |  |

1. Valid before POR signal enable.

# 6 Voltage regulators

## 6.1 BUCK1 switching regulator

Unless otherwise noted, typical values at T<sub>A</sub> = 25 °C, Vin = 5.0 V.

The max. values are at Tj = 125 °C and the worst case process.

| Parameter                   | Conditions                                                                                            | Min.               | Тур.               | Max. | Unit |

|-----------------------------|-------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|------|

| DC bias current             | No load , PFM mode                                                                                    |                    | 20                 |      | μA   |

| Output DC voltage range     | Steady state, I <sub>LOAD</sub> < 1 A                                                                 | 0.9                |                    | 1.6  | V    |

| Output voltage step size    | Single step change                                                                                    |                    | 25                 |      | mV   |

| Load current                | Internal FET, steady state                                                                            |                    |                    | 1    | А    |

| Current limit threshold     | Integrated FET current                                                                                |                    | 2.5 <sup>(1)</sup> |      | А    |

| PFM current peak            | Programmable peak current                                                                             |                    | 0.8                |      | А    |

| DC line regulation          | 3.3 V < VSUP < 5 V, lout = 1 A                                                                        |                    | 0.4 <sup>(1)</sup> |      | %/V  |

| DC load regulation          | While in PWM<br>PSR1CFG bit 7 = 1                                                                     |                    | 0.2 <sup>(1)</sup> |      | %/A  |

| Switching frequency         | Programmable                                                                                          |                    | 1.3                |      | MHz  |

| Output voltage accuracy     | While In PWM                                                                                          | -2                 |                    | +2   | %    |

| Transient response          | Load transient time = 10 $\mu$ s. Referring to CCM,<br>Vout = 1.2 V, load current from 0 to 80% Imax. |                    | ±3 <sup>(1)</sup>  |      | %    |

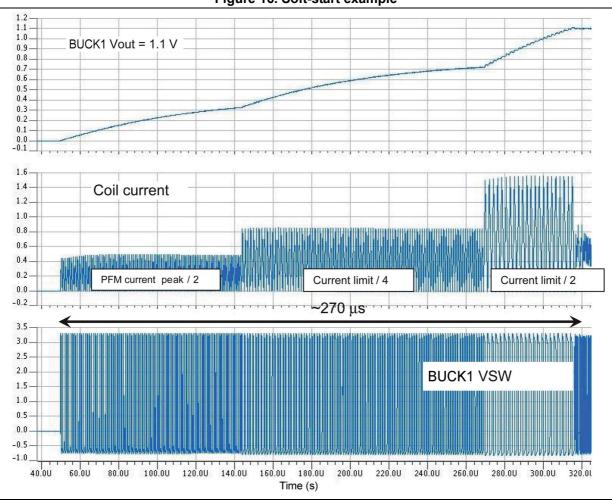

| Soft-start time             | Vin = 3.3 V, output voltage ramp from 0 to 95% of final Vout = 1.2 V, R load =1.4 $\Omega$ .          | 250 <sup>(1)</sup> | 360 <sup>(1)</sup> |      | μS   |

| Integrated high-side PFET   | Vin =5 V                                                                                              |                    | 109                |      |      |

| R <sub>DS</sub>             | Vin = 3.3 V                                                                                           |                    | 132                |      |      |

| Integrated low-side NFET    | Vin = 5 V                                                                                             |                    | 58                 |      | - mΩ |

| R <sub>DS</sub>             | Vin = 3.3 V                                                                                           |                    | 65                 |      | _    |

|                             | Vin = 5.0 V, Vout = 1.2 V, Iload = 1 mA                                                               |                    | 82 <sup>(2)</sup>  |      |      |

| Efficiency                  | Vin =3.3 V, Vout = 1.2 V, Iload = 1 mA                                                                |                    | 84 <sup>(2)</sup>  |      | %    |

| Efficiency                  | Vin = 5.0 V, Vout = 1.2 V, Iload = 1 A                                                                |                    | 81 <sup>(2)</sup>  |      | - 70 |

|                             | Vin = 3.3 V, Vout = 1.2 V, Iload = 1 A                                                                |                    | 82 <sup>(2)</sup>  |      | _    |

| FB input impedance          |                                                                                                       |                    | 0.2                |      | MΩ   |

| Input capacitor             |                                                                                                       |                    | 4.7                |      | μF   |

| Output filter capacitor     |                                                                                                       |                    | 22                 |      | μF   |

| Output filter capacitor ESR |                                                                                                       |                    |                    | 20   | mΩ   |

| Output filter inductance    |                                                                                                       |                    | 1.0                |      | μH   |

| Table 10. | BUCK1 | switching | regulator |

|-----------|-------|-----------|-----------|

|           | DOONI | Switching | regulator |

1. Guaranteed by design.

2. Efficiency measured between the SUP14 PIN and BUCK1 POUT and while the BUCK4 is off. L = 1  $\mu$ H, DC resistance max. = 0.036  $\Omega$ .

# 6.2 BUCK2 switching regulator

Unless otherwise noted, typical values at T<sub>A</sub> = 25 °C, Vin = 5.0 V.

The max. values are at Tj = 125 °C and the worst case process.

| Parameter                                 | Conditions                                                                                         | Min.               | Тур.               | Max. | Unit |

|-------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------|--------------------|------|------|

| DC bias current                           | No load , PFM mode                                                                                 |                    | 20                 |      | μΑ   |

| Output DC voltage range                   | Steady state, I <sub>LOAD</sub> < 0.8 A                                                            | 1.5                |                    | 2.1  | V    |

| Output voltage step size                  | Single step change                                                                                 |                    | 37.5               |      | mV   |

| Load current range                        | Internal FET, steady state                                                                         |                    |                    | 0.8  | А    |

| Current limit threshold                   | Integrated FET current                                                                             |                    | 2.5 <sup>(1)</sup> |      | Α    |

| PFM current peak                          | Programmable                                                                                       |                    | 0.8                |      | А    |

| DC line regulation                        | 3.3 V < VSUP < 5 V, lout = 0.8 A                                                                   |                    | 0.4 <sup>(1)</sup> |      | %/V  |

| DC load regulation                        | While in PWM PSR2CFG bit 7 = 1                                                                     |                    | 0.1 <sup>(1)</sup> |      | %/A  |

| Switching frequency                       | Programmable                                                                                       |                    | 1.3                |      | MHz  |

| Output voltage accuracy                   | While in PWM                                                                                       | -2                 |                    | +2   | %    |

| Transient response                        | Load transient time = 10 µs<br>Referring to CCM, Vout = 1.8 V, load current<br>from 0 to 80% Imax. |                    | ±3 <sup>(1)</sup>  |      | %    |

| Soft-start time                           | Vin = 3.3 V, output voltage ramp from 0 to 95% of final Vout = 1.8 V, max. load = $3.6 \Omega$ .   | 210 <sup>(1)</sup> | 245 <sup>(1)</sup> |      | μs   |

| Interneted birth side DEET D              | Vin = 5 V                                                                                          |                    | 172                |      |      |

| Integrated high-side PFET R <sub>DS</sub> | Vin = 3.3 V                                                                                        |                    | 216                |      |      |

| Integrated Jow side NEET D                | Vin = 5 V                                                                                          |                    | 88                 |      | mΩ   |

| Integrated low-side NFET R <sub>DS</sub>  | Vin = 3.3 V                                                                                        |                    | 106                |      | 1    |

|                                           | Vin = 5.0 V, Vout = 1.8 V, Iload = 1 mA                                                            |                    | 83 <sup>(2)</sup>  |      |      |

|                                           | Vin = 3.3 V, Vout = 1.8 V, Iload = 1 mA                                                            |                    | 85 <sup>(2)</sup>  |      | 0/   |

| Efficiency                                | Vin = 5.0 V, Vout = 1.8 V, Iload = 0.8 A                                                           |                    | 84 <sup>(2)</sup>  |      | - %  |

|                                           | Vin = 3.3 V, Vout = 1.8 V, Iload = 0.8 A                                                           |                    | 86 <sup>(2)</sup>  |      | 1    |

| FB input impedance                        |                                                                                                    |                    | 0.2                |      | MΩ   |

| Input capacitor                           |                                                                                                    |                    | 4.7                |      | μF   |

| Output filter capacitor                   |                                                                                                    |                    | 22                 |      | μF   |

| Output filter capacitor ESR               |                                                                                                    |                    |                    | 20   | mΩ   |

| Output filter inductance                  |                                                                                                    |                    | 1.0                |      | μH   |

1. Guaranteed by design.

2. Efficiency measured between the SUP2 PIN and BUCK2 POUT. L = 1  $\mu$ H, DC resistance max. = 0.036  $\Omega$ .

# 6.3 BUCK3 switching regulator

Unless otherwise noted, typical values at T\_A = 25 °C, Vin = 5.0 V.

The max. values are at Tj = 125 °C and the worst case process.

| DC bias currentPFM mode<br>Deep sleep mode no loadOutput DC voltage rangeSteady state, I <sub>LOAD</sub> < 1 AOutput voltage step sizeSingle step changeLoad current rangeInternal FET, steady stateCurrent limit thresholdIntegrated FET currentPFM current peakProgrammableDC line regulation3.3 V < VSUP < 5 V, lout = 0.5 ADC load regulationDC DE | 0.7                                 | 20<br>25<br>2.0 <sup>(1)</sup> | 1.3 | μA<br>V<br>mV |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------|-----|---------------|

| Output voltage step size   Single step change     Load current range   Internal FET, steady state     Current limit threshold   Integrated FET current     PFM current peak   Programmable     DC line regulation   3.3 V < VSUP < 5 V, lout = 0.5 A                                                                                                                                       | 0.7                                 |                                |     |               |

| Load current range   Internal FET, steady state     Current limit threshold   Integrated FET current     PFM current peak   Programmable     DC line regulation   3.3 V < VSUP < 5 V, lout = 0.5 A                                                                                                                                                                                         |                                     |                                | 0.5 | mV            |

| Current limit threshold   Integrated FET current     PFM current peak   Programmable     DC line regulation   3.3 V < VSUP < 5 V, lout = 0.5 A                                                                                                                                                                                                                                             |                                     | 2.0 <sup>(1)</sup>             | 0.5 |               |

| PFM current peak Programmable   DC line regulation 3.3 V < VSUP < 5 V, lout = 0.5 A                                                                                                                                                                                                                                                                                                        |                                     | 2.0 <sup>(1)</sup>             |     | Α             |

| DC line regulation 3.3 V < VSUP < 5 V, lout = 0.5 A                                                                                                                                                                                                                                                                                                                                        |                                     | 1                              |     | Α             |

| While in PWM                                                                                                                                                                                                                                                                                                                                                                               |                                     | 0.8                            |     | Α             |

| DC load regulation While in PWM                                                                                                                                                                                                                                                                                                                                                            |                                     | 0.4 <sup>(1)</sup>             |     | %/V           |

| PSR3CFG bit 7 = 1                                                                                                                                                                                                                                                                                                                                                                          |                                     | 0.1 <sup>(1)</sup>             |     | %/A           |

| Switching frequency Programmable                                                                                                                                                                                                                                                                                                                                                           |                                     | 1.3                            |     | MHz           |

| Output voltage accuracy While in PWM                                                                                                                                                                                                                                                                                                                                                       | -2                                  |                                | +2  | %             |

| Transient responseLoad transient time = 10 µs. Referring to C<br>Vout = 1.1 V, load current from 0 to 80% In                                                                                                                                                                                                                                                                               |                                     | ±3 <sup>(1)</sup>              |     | %             |

| Soft-start timeVin = 3.3 V, output voltage ramp from 0 to 95<br>final Vout = 1.1 V Rload = 3.0 Ω.                                                                                                                                                                                                                                                                                          | <sup>5% of</sup> 130 <sup>(1)</sup> | 160 <sup>(1)</sup>             |     | μs            |

| Vin = 5 V                                                                                                                                                                                                                                                                                                                                                                                  |                                     | 172                            |     |               |

| Integrated high-side PFET R <sub>DS</sub> Vin = 3.3 V                                                                                                                                                                                                                                                                                                                                      |                                     | 216                            |     | -             |

| Vin = 5 V                                                                                                                                                                                                                                                                                                                                                                                  |                                     | 88                             |     | mΩ            |

| Integrated low-side NFET R <sub>DS</sub> Vin = 3.3 V                                                                                                                                                                                                                                                                                                                                       |                                     | 106                            |     | 1             |

| Vin = 5.0 V, Vout = 1.1 V, Iload = 1 mA                                                                                                                                                                                                                                                                                                                                                    |                                     | 78 <sup>(2)</sup>              |     |               |

| Vin = 3.3 V, Vout = 1.1 V, Iload = 1 mA                                                                                                                                                                                                                                                                                                                                                    |                                     | 81 <sup>(2)</sup>              |     |               |

| Efficiency Vin = 5.0 V, Vout = 1.1 V, Iload = 0.5 A                                                                                                                                                                                                                                                                                                                                        |                                     | 80 <sup>(2)</sup>              |     | %             |

| Vin = 3.3 V, Vout= 1.1 V, Iload = 0.5 A                                                                                                                                                                                                                                                                                                                                                    |                                     | 81 <sup>(2)</sup>              |     | 1             |

| FB input impedance                                                                                                                                                                                                                                                                                                                                                                         |                                     | 0.2                            |     | MΩ            |

| Input capacitor                                                                                                                                                                                                                                                                                                                                                                            |                                     | 4.7                            |     | μF            |

| Output filter capacitor                                                                                                                                                                                                                                                                                                                                                                    |                                     | 22                             |     | μF            |

| Output filter capacitor ESR                                                                                                                                                                                                                                                                                                                                                                |                                     |                                | 20  | mΩ            |

| Output filter inductance                                                                                                                                                                                                                                                                                                                                                                   |                                     | 1.0                            |     | μH            |

| Table 12. | BUCK3  | switching | regulator |

|-----------|--------|-----------|-----------|

|           | 000100 | Switching | regulator |

1. Guaranteed by design.

2. Efficiency measured between the SUP3 PIN and BUCK3 POUT. L = 1  $\mu$ H, DC resistance max. = 0.036  $\Omega$ .

# 6.4 BUCK4 switching regulator

Unless otherwise noted, typical values at T<sub>A</sub> = 25 °C, Vin = 5.0 V.

The max. values are at Tj = 125 °C and the worst case process.

| Parameter                                | Conditions                                                                                          | Min. | Тур.               | Max. | Unit   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------|------|--------------------|------|--------|

| DC bias current                          | No load , PFM mode                                                                                  |      | 20                 |      | μA     |

| Output DC voltage range                  | Steady state, I <sub>LOAD</sub> < 1 A                                                               | 0.7  |                    | 1.3  | V      |

| Output voltage step size                 | Single step change                                                                                  |      | 25                 |      | mV     |

| Load current range                       | Internal FET, steady state                                                                          |      |                    | 1.0  | А      |

| Current limit threshold                  | Integrated FET current                                                                              |      | 3.0 <sup>(1)</sup> |      | А      |

| PFM current peak                         | Programmable                                                                                        |      | 0.8                |      | А      |

| DC line regulation                       | 3.3 V < VSUP < 5 V lout = 1 A                                                                       |      | 0.4 <sup>(1)</sup> |      | %/V    |

| DC load regulation                       | While in PWM PSR4CFG bit 7 = 1                                                                      |      | 0.2 <sup>(1)</sup> |      | %/A    |

| Switching frequency                      | Programmable                                                                                        |      | 1.3                |      | MHz    |

| Output voltage accuracy                  | While In PWM                                                                                        | -2   |                    | +2   | %      |

| Transient response                       | Load transient time = 10 µs.<br>Referring to CCM, Vout = 1.1 V, load current from 0 to<br>80% Imax. |      | ±3 <sup>(1)</sup>  |      | %      |

| Soft-start time                          | Vin = 3.3 V, output voltage ramp from 0 to 95% of final Vout = 1.1 V, Rload = 1.5 $\Omega$ .        |      | 360 <sup>(1)</sup> |      | μs     |

| Integrated high-side PFET RDS            | Vin = 5 V                                                                                           |      | 109                |      |        |

| Integrated high-side FFET RDS            | Vin = 3.3 V                                                                                         |      | 132                |      | mΩ     |

| Integrated low side NEET D               | Vin = 5 V                                                                                           |      | 58                 |      | 1115.2 |

| Integrated low-side NFET R <sub>DS</sub> | Vin = 3.3 V                                                                                         |      | 65                 |      |        |

|                                          | Vin = 5.0 V, Vout = 1.1 V, Iload = 1 mA                                                             |      | 82 <sup>(2)</sup>  |      |        |

| Efficiency                               | Vin = 3.3 V, Vout = 1.1 V, Iload = 1 mA                                                             |      | 83 <sup>(2)</sup>  |      | 0/     |

| Enciency                                 | Vin = 5.0 V, Vout = 1.1 V, Iload = 1 A                                                              |      | 81 <sup>(2)</sup>  | %    |        |

|                                          | Vin = 3.3 V, Vout = 1.1 V, Iload = 1 A                                                              |      | 82 <sup>(2)</sup>  |      |        |

| FB input impedance                       |                                                                                                     |      | 0.2                |      | MΩ     |

| Input capacitor                          |                                                                                                     |      | 4.7                |      | μF     |

| Output filter capacitor                  |                                                                                                     |      | 44                 |      | μF     |

| Output filter capacitor ESR              |                                                                                                     |      |                    | 20   | mΩ     |

| Output filter inductance                 |                                                                                                     |      | 1.0                |      | μH     |

1. Guaranteed by design.

2. Efficiency measured between the SUP14 PIN and BUCK4 POUT and while the BUCK1 is off. L= 1  $\mu$ H, DC resistance max = 0.036  $\Omega$ .

# 6.5 BUCK5 switching regulator

Unless otherwise noted, typical values at T\_A = 25 °C, Vin = 5.0 V.

The max. values are at Tj = 125 °C and the worst case process.

| Parameter                          | Conditions                                                                                       | Min. | Тур.               | Max. | Unit |  |

|------------------------------------|--------------------------------------------------------------------------------------------------|------|--------------------|------|------|--|

| DC bias current                    | No load , PFM mode                                                                               |      | 20                 |      | μA   |  |

| Output DC voltage range            | Steady state, I <sub>LOAD</sub> < 1.6 A                                                          | 0.7  |                    | 1.3  | V    |  |

| Output voltage step size           | Single step change                                                                               |      | 25                 |      | mV   |  |

| Load current range                 | Internal FET, steady state                                                                       |      |                    | 1.6  | Α    |  |

| Current limit threshold            | Integrated FET current                                                                           |      | 4.0 <sup>(1)</sup> |      | Α    |  |

| PFM current peak                   | Programmable                                                                                     |      | 0.8 <sup>(1)</sup> |      | Α    |  |

| DC line regulation                 | 3.3 V < VSUP < 5 V, Iload = 1.6 A                                                                |      | 0.5 <sup>(1)</sup> |      | %/V  |  |

| DC load regulation                 | While in PWM<br>PSR5CFG bit 7 = 1                                                                |      | 0.1 <sup>(1)</sup> |      | %/A  |  |

| Switching frequency                | Programmable                                                                                     |      | 1.3                |      | MHz  |  |

| Output voltage accuracy            | While in PWM                                                                                     | -2   |                    | +2   | %    |  |

| Transient response                 | Load transient time = 10 µs. Referring to CCM,<br>Vout = 1.1 V, load current from 0 to 80% Imax. |      | ±3 <sup>(1)</sup>  |      | %    |  |

|                                    | Vin = 5 V                                                                                        |      | 89                 |      |      |  |

| Integrated high-side PFET $R_{DS}$ | Vin = 3.3 V                                                                                      |      | 105                |      |      |  |

| Integrated low side NEET D         | Vin = 5 V                                                                                        |      | 58                 |      | mΩ   |  |

| Integrated low-side NFET $R_{DS}$  | Vin = 3.3 V                                                                                      |      | 65                 |      | 1    |  |

|                                    | Vin = 5.0 V, Vout = 1.1 V, Iload = 1 mA                                                          |      | 82 <sup>(2)</sup>  |      |      |  |

| Fficiency                          | Vin = 3.3 V, Vout = 1.1 V, Iload = 1 mA                                                          |      | 84 <sup>(2)</sup>  |      | 0/   |  |

| Efficiency                         | Vin = 5.0 V, Vout = 1.1 V, Iload = 1.6 A                                                         |      | 78 <sup>(2)</sup>  |      | %    |  |

|                                    | Vin = 3.3 V, Vout = 1.1 V, Iload = 1.6 A                                                         |      | 78 <sup>(2)</sup>  |      | 1    |  |

| FB input impedance                 |                                                                                                  |      | 0.2                |      | MΩ   |  |

| Input capacitor                    |                                                                                                  | 1    | 4.7                |      | μF   |  |

| Output filter capacitor            |                                                                                                  |      | 44                 |      | μF   |  |

| Output filter capacitor ESR        |                                                                                                  |      |                    | 20   | mΩ   |  |

| Output filter inductance           |                                                                                                  |      | 1.0                |      | μH   |  |

Table 14. BUCK5 switching regulator

1. Guaranteed by design.

2. Efficiency measured between the SUP5 PIN and BUCK5 POUT. L = 1  $\mu$ H, DC resistance max. = 0.036  $\Omega$ .

# 6.6 Thermal shutdown

Table 15. Thermal shutdown

| Parameter                      | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------|------------|------|------|------|------|

| Thermal shutdown temp. rising  |            | 150  | 160  | 170  | °C   |

| Thermal shutdown temp. falling |            | 120  | 130  | 140  |      |

L7292

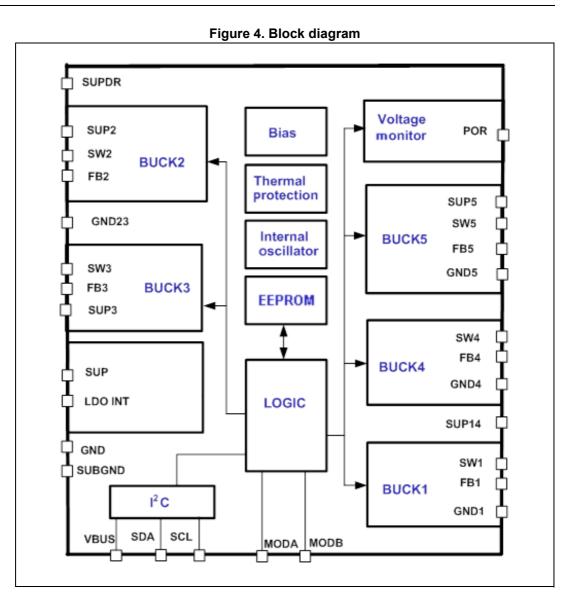

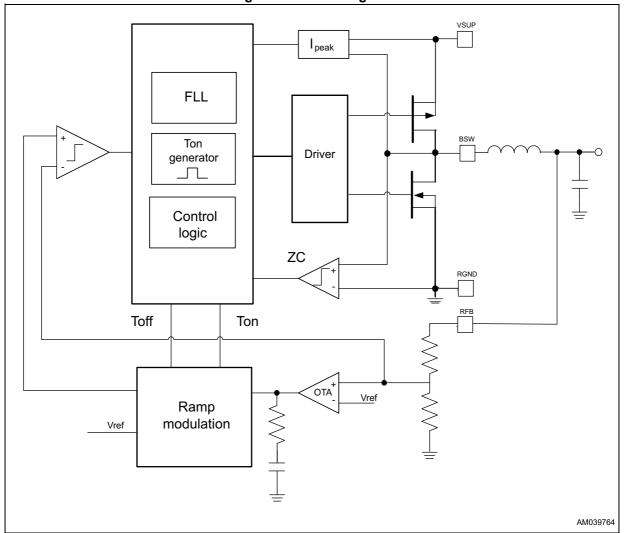

# 7 General description

The PMU is an integrated circuit designed to supply the  $\mu$ Controller and memory in applications supplied by a battery or 5 V. Each regulator is independent from the others and can be enabled or disabled by the I<sup>2</sup>C serial port.

A 128-bit EEPROM is embedded in the device to store the default conditions used in each power up:

- The order in which the PSRs start during a power up sequence

- The programmable delay at the beginning and at the end of the power up sequence

- The programmable delay between each regulator start-up

- Excluding from the power up sequence any number of regulators

- The undervoltage mask and digital deglitch programmability for all regulators and for external and internal supplies

- Switching node slew rate programmability, disabling of synchronous rectification, PFM disabling for all switching regulators.

All regulators employ synchronous rectification and have an automatic transition between PWM and PFM. A voltage monitor and thermal protection are present for a better control of system functionality.

# 8 I<sup>2</sup>C interface

### 8.1 Description

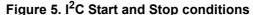

This device features an I<sup>2</sup>C interface and can be operated from a VDD power supply. The I<sup>2</sup>C uses a two-wire serial interface, comprising a bidirectional data line and a clock line. The devices carry a built-in 7-bit device type identifier code in accordance with the I<sup>2</sup>C bus definition. The device behaves as a slave in the I<sup>2</sup>C protocol, with all operations synchronized by the serial clock. Read and Write operations are initiated by a Start condition, generated by the bus master. The Start condition is followed by a device select code and a Read/Write bit (RW), terminated by an acknowledge bit. When writing data to the device, the device inserts an acknowledge bit during the 9<sup>th</sup> bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an ACK for Write and after a NoACK for Read.

### 8.2 Signal description

#### 8.2.1 Serial clock (SCL)

This input signal is used to strobe all data in and out of the device. In applications where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor must be connected from the serial clock (SCL) to VDD. In most applications, though, this method of synchronization is not employed, and so the pull-up resistor is not necessary, provided that the bus master has a push-pull (rather than open drain) output.

#### 8.2.2 Serial data (SDA)

This bidirectional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus.

A pull-up resistor must be connected from serial data (SDA) to VDD.

## 8.3 I<sup>2</sup>C device operation

The device supports the I<sup>2</sup>C protocol. Any device that sends data on to the bus is defined to be a transmitter, and any device that reads the data to be a receiver. The device that controls the data transfer is known as the bus master, and the other as the slave device. A data transfer can only be initiated by the bus master, which will also provide the serial clock for synchronization. The device is always a slave in all communications.

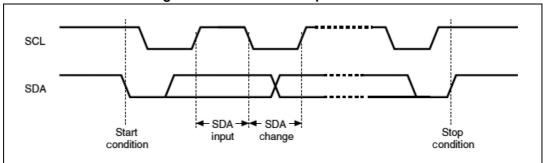

#### 8.3.1 Start condition

The start is identified by a falling edge of Serial Data (SDA) while the Serial Clock (SCL) is stable in the high state. A Start condition must precede any data transfer command. The device continuously monitors (except during a write cycle) Serial Data (SDA) and the Serial Clock (SCL) for a Start condition, and will not respond unless one is given.

#### 8.3.2 Stop condition

The Stop is identified by a rising edge of Serial Data (SDA) while the Serial Clock (SCL) is stable and driven high. A Stop condition terminates communication between the device and the bus master. A Read command that is followed by NoACK can be followed by a Stop condition.

The Stop condition can be substituted by a repeated Start condition. In this case the bus remains busy and another communication can start immediately.

#### 8.3.3 Acknowledge bit (ACK)

The acknowledge bit is used to indicate a successful byte transfer. The bus transmitter, whether it is the bus master or slave device, releases Serial Data (SDA) after sending eight bits of data. During the 9<sup>th</sup> clock pulse period, the receiver pulls Serial Data (SDA) low to acknowledge the receipt of the eight data bits.

#### 8.3.4 Data input

During data input, the device samples Serial Data (SDA) on the rising edge of the Serial Clock (SCL). For the correct device operation, Serial Data (SDA) must be stable during the rising edge of the Serial Clock (SCL), and the Serial Data (SDA) signal must change only when the Serial Clock (SCL) is driven low.

### 8.3.5 Register bank addressing

To start communication between the bus master and the slave device, the bus master must initiate a Start condition. Following this, the bus master sends the device select code (on Serial Data (SDA), the most significant bit first). The device select code consists of a 7-bit device type identifier which for the L7292 device is 0x7C.

The 8<sup>th</sup> bit is the Read/Write bit (RW). This bit is set to 1 for Read and 0 for Write operations. If a match occurs on the device select code, the corresponding device gives an acknowledgment on Serial Data (SDA) during the 9<sup>th</sup> bit time. If the device does not match the device select code, it deselects itself from the bus.

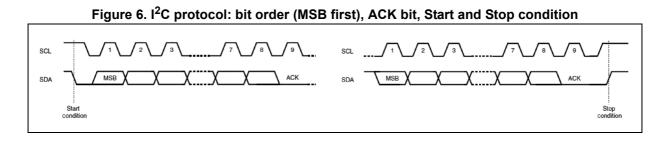

### 8.3.6 Write operations

Following a Start condition the bus master sends a device select code with the Read/Write bit (RW) reset to 0. The device acknowledges this and waits for one address bytes. The device responds to the address byte with an acknowledge bit, and then waits for the data byte.

A Write instruction issued on a Read Only or a reserved address does not modify the register contents.

### 8.3.7 Byte Write

After the device selects the code and the address byte, the bus master sends one data byte. After the data byte the device responds with an ACK bit, also if the address is read only or reserved. The bus master terminates the transfer by generating a Stop condition or a repeated Start condition.

### 8.3.8 Sequential Write

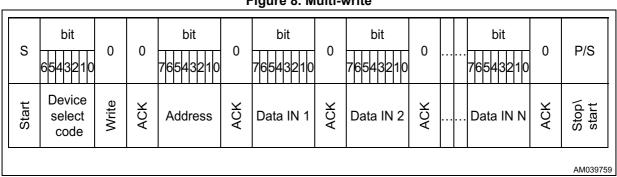

The Sequential Write mode allows up to all bytes to be written in a single Write cycle. After each byte is transferred, the internal byte address counter is incremented. The transfer is terminated by the bus master generating a Stop condition.

Figure 7. Byte Write

Figure 8. Multi-write

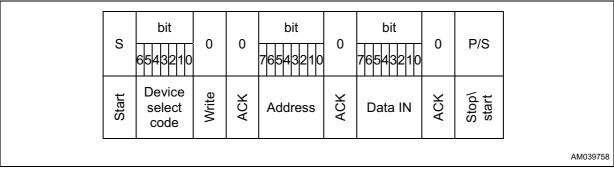

#### 8.3.9 Read operations

Following a Start condition the bus master sends a device select code with the Read/Write bit (RW) set to 1. After the successful completion of a Read operation, the device's internal address counter is incremented by one, to point to the next register address.

#### 8.3.10 Random Address Read

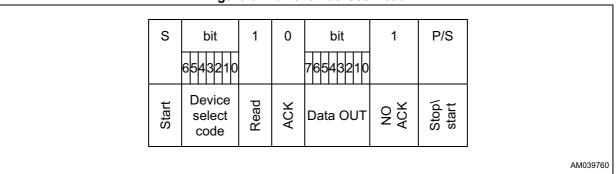

A dummy Write is first performed to load the address into this address counter but without sending a Stop condition. Then, the bus master sends another Start condition, and repeats the device select code, with the Read/Write bit (RW) set to 1. The device acknowledges this, and outputs the contents of the addressed byte. The bus master must not acknowledge the byte, and terminates the transfer with a Stop condition or a repeated Start condition.

#### 8.3.11 **Current Address Read**

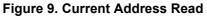

For the Current Address Read operation, following a Start condition, the bus master only sends a device select code with the Read/Write bit (RW) set to 1. The device acknowledges this, and outputs the byte addressed by the internal address counter. The counter is then incremented. The bus master terminates the transfer with a Stop condition or a repeated Start condition, without acknowledging the byte.

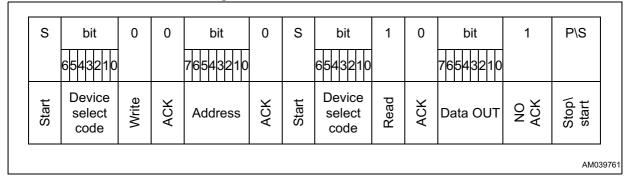

#### 8.3.12 Sequential Read

This operation can be used after a Current Address Read or a Random Address Read. The bus master does acknowledge the data byte output, and sends additional clock pulses so that the device continues to output the next byte in sequence. To terminate the stream of bytes, the bus master must not acknowledge the last byte, and must generate a Stop condition or a repeated Start condition. The output data comes from consecutive addresses, with the internal address counter automatically incremented after each byte output.

After the last memory address, the address counter "rolls-over", and the device continues to output data from the memory address 00h.

#### 8.3.13 Acknowledge in Read mode

For all Read commands, the device waits, after each byte read, for an acknowledgment during the 9<sup>th</sup> bit time. If the bus master does not drive Serial Data (SDA) low during this time, the device terminates the data transfer.

Figure 10. Random Address Read

Figure 11. Sequential Current Address Read

| S     | bit<br>6 5 4 3 2 1 0     | 1    | 0   | bit<br>76543210 | 0   | bit<br>76543210 | 0   | <br>bit<br>76543210 | 0         | P\S            |      |

|-------|--------------------------|------|-----|-----------------|-----|-----------------|-----|---------------------|-----------|----------------|------|

| Start | Device<br>select<br>code | Read | ACK | Data<br>OUT 1   | ACK | Data<br>OUT 2   | ACK | <br>Data<br>OUT N   | NO<br>ACK | Stop\<br>start |      |

|       |                          |      |     |                 |     |                 |     |                     |           | AM03           | 9762 |

#### Figure 12. Sequential Random Address Read

| s     | bit                      | 0     | 0   | bit      | 0   | S     | bit                      | 1    | 0   | bit           | 0   | <br>. bit         | 1         | P\S            |

|-------|--------------------------|-------|-----|----------|-----|-------|--------------------------|------|-----|---------------|-----|-------------------|-----------|----------------|

|       | 6543210                  |       |     | 76543210 |     |       | 6543210                  |      |     | 76543210      |     | 76543210          |           |                |

| Start | Device<br>select<br>code | Write | ACK | Address  | ACK | Start | Device<br>select<br>code | Read | ACK | Data<br>OUT 1 | ACK | <br>Data<br>OUT N | NO<br>ACK | Stop\<br>start |

|       |                          |       |     |          |     |       |                          |      |     |               |     |                   |           | AM039763       |

The device supports the I<sup>2</sup>C high speed mode to operate up to 3.4 Mbit/s. If the bus master wants to operate in the HS-mode a proper initial sequence in the fast-mode (max. 400 kbit/s) should be sent as described in the I<sup>2</sup>C bus specification:

- 1. Start condition (S)

- 2. 8-bit master code (00001XXX)

- 3. Not acknowledge bit (A)

After this sequence the bus switches into the high speed mode until first Stop condition.

# 9 Register map

An internal register bank can be accessed by the  $I^2C$  interface. The size of the address space is 64 (address word length = 6 bits). Not every register bit can be accessed in the read/write mode; there are also the read only and reserved bit. A read only bit can be only read and a write operation has no effect. A reserved bit returns '0' when read and a write operation has no effect.

### 9.1 General overview

| Address | dress Name Descriptio |                                                  | Bit<br>Name<br>Read/write<br>Reset value                                                                           |                         |                         |                   |                                               |                                             |                     |                   |  |

|---------|-----------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------|-----------------------------------------------|---------------------------------------------|---------------------|-------------------|--|

|         |                       |                                                  | 7                                                                                                                  | 6                       | 5                       | 4                 | 3                                             | 2                                           | 1                   | 0                 |  |

| 0x01    | PSR1VL                | Power switching<br>regulator 1<br>voltage level  | PSR1VLEN PSR1OCDI<br>R/W SR/W Reserved<br>0x0 0x0                                                                  |                         |                         | De                | fault de                                      | VL[4:0<br>R/W<br>fined b                    | )]<br>y MOD p       | ins               |  |

| 0x02    | PSR3VL                | Power switching<br>regulator 3<br>voltage level  | PSR3VLEN<br>R/W<br>0x0                                                                                             | PSR3OCDI<br>SR/W<br>0x0 | Reserved                | De                | fault de                                      | VL[4:0]<br>R/W<br>fault defined by MOD pins |                     |                   |  |

| 0x03    | PSR2VL                | Power switching<br>regulator 2<br>voltage level  | PSR2VLEN<br>R/W<br>0x0                                                                                             | R/W SR/W Reserved       |                         |                   | VL[4:0]<br>R/W<br>Default defined by MOD pins |                                             |                     |                   |  |

| 0x04    | PSR4VL                | Power switching<br>regulator 4<br>voltage level  | PSR4VLEN<br>R/W<br>0x0                                                                                             | R/W SR/W Reserved       |                         |                   | fault de                                      | L[4:0]<br>R/W<br>fined by MOD pins          |                     |                   |  |

| 0x05    | PSR5VL                | Power switching<br>regulator 5<br>voltage level  | PSR5VLEN<br>R/W<br>0x0                                                                                             | PSR5OCDI<br>SR/W<br>0x0 | Reserved                | De                | VL[4:0]<br>R/W<br>Default defined by MOD pins |                                             |                     |                   |  |

| 0x07    | PSR1CFG               | Power switching<br>regulator 1<br>configuration  | PFMDIS<br>R/W<br>0x0                                                                                               | OF                      | RDER[2:0]<br>R/W<br>0x2 |                   | SLEV<br>R/<br>0>                              | Ŵ                                           | LSDIS<br>R/W<br>0x0 | UVM<br>R/W<br>0x0 |  |

| 0x08    | PSR3CFG               | Power switching<br>regulator 3<br>configuration  | PFMDIS<br>R/W<br>0x0                                                                                               | OF                      | RDER[2:0]<br>R/W<br>0x0 |                   | RSLE<br>R/<br>0>                              | W                                           | LSDIS<br>R/W<br>0x0 | UVM<br>R/W<br>0x0 |  |

| 0x09    | PSR2CFG               | Power switching<br>regulator 2<br>configuration  | PFMDIS<br>R/W<br>0x0                                                                                               | R/W R/W R               |                         | RSLE<br>R/<br>0>  | W                                             | LSDIS<br>R/W<br>0x0                         | UVM<br>R/W<br>0x0   |                   |  |

| 0x0A    | PSR4CFG               | Power switching<br>regulator 4<br>configura-tion | PFMDIS     ORDER[2:0]     RSLEW[1:0]     LSDIS       R/W     R/W     R/W     R/W       0x0     0x0     0x3     0x0 |                         |                         | UVM<br>R/W<br>0x0 |                                               |                                             |                     |                   |  |

| 0x0B    | PSR5CFG               | Power switching<br>regulator 5<br>configura-tion | PFMDIS     ORDER[2:0]       R/W     R/W       0x0     0x1                                                          |                         |                         | RSLE<br>R/<br>0>  | W                                             | LSDIS<br>R/W<br>0x0                         | UVM<br>R/W<br>0x0   |                   |  |

#### Table 16. Register map overview

DocID028601 Rev 2

|              | Table 17. Register map overview (continued) |                                                        |                                  |                                |                       |                       |                       |                       |                       |                      |

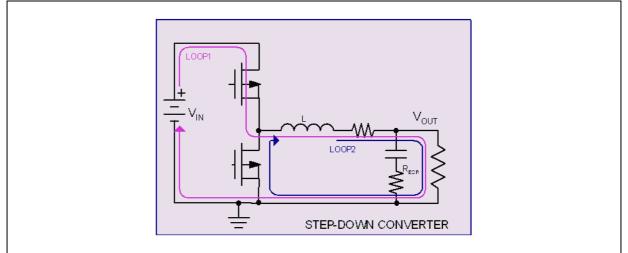

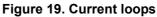

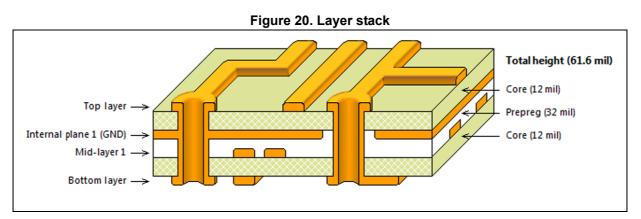

|--------------|---------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|