XTR305

ZHCSHO6-FEBRUARY 2018

# XTR305 工业模拟电流或电压输出驱动器

# 1 特性

- 用户可选: 电流或电压输出

- V<sub>OUT</sub>: ±10V (电源电压为 ±20V 时高达 ±17.5V)

- I<sub>OUT</sub>: ±20mA (线性电流高达 ±24mA)

- 40V 电源电压

- 诊断 特性:

- 短路或开路故障指示灯引脚

- 热保护

- 过流保护

- 无需电流分流

- 适用于单输入模式的输出禁用

- 独立驱动器和接收器通道

- 专为可测试性而设计

# 2 应用

- 电机驱动器模式输出:电流为 4-20mA,电压为 ±10V

- PLC 输出可编程驱动器

- 工业交叉连接器

- 工业高电压 I/O

- 3 线传感器电流或电压输出

- ±10V 2 线和 4 线电压输出 美国专利号7,427,898、7,425,848 和 7,449,873

# 3 说明

XTR305 是一个完整的输出驱动器,适用于成本敏感型工业和过程控制 应用供电的绝佳器件。数字 I/V 选择引脚可将输出配置为电流或电压。无需外部分流电阻器。只需要外部增益设置电阻器和环路补偿电容器。

独立的驱动器和接收器通道可提供灵活性。仪表放大器 (IA) 可用于远程电压传感或用作高电压、高阻抗测量通道。在电压输出模式下,提供输出电流的副本,允许计算负载电阻。

利用数字输出选择功能、错误标志以及监控器引脚,可进行远程配置和故障排除。输出和 IA 输入的故障条件以及过热情况由错误标志指示。监控引脚提供有关负载功率或阻抗的持续反馈。为了获得额外的保护,最大输出电流是受限的,并提供过热保护。

XTR305 具有 -40°C 至 +85°C 的额定工业温度范围,电源电压最高可达 40V,并可在 -55°C 至 +125°C 的扩展温度范围内正常运行。

### **哭**件信息(1)

| HH I I I I I I I I I I I I I I I I I I |           |                 |  |  |  |  |

|----------------------------------------|-----------|-----------------|--|--|--|--|

| 器件型号                                   | 封装        | 封装尺寸 (标称值)      |  |  |  |  |

| XTR305                                 | VQFN (20) | 5.00mm × 5.00mm |  |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

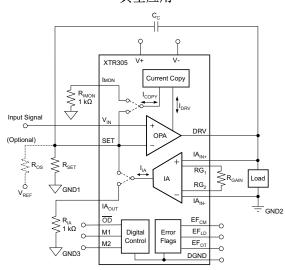

# 典型应用

Copyright © 2017, Texas Instruments Incorporated

# 目录

| 1 | 特性1                                                       |    | 7.2 Functional Block Diagrams      | 16              |

|---|-----------------------------------------------------------|----|------------------------------------|-----------------|

| 2 | 应用 1                                                      |    | 7.3 Feature Description            | 18              |

| 3 | 说明 1                                                      |    | 7.4 Device Functional Modes        | <mark>20</mark> |

| 4 | 修订历史记录 2                                                  | 8  | Application and Implementation     | 21              |

| 5 | Pin Configuration and Functions3                          |    | 8.1 Application Information        | 21              |

| 6 | Specifications4                                           |    | 8.2 Typical Application            | 21              |

| • | 6.1 Absolute Maximum Ratings 4                            | 9  | Power Supply Recommendations       | <u>29</u>       |

|   | 6.2 ESD Ratings                                           | 10 | Layout                             | 30              |

|   | 6.3 Recommended Operating Conditions                      |    | 10.1 Layout Guidelines             | 30              |

|   | 6.4 Thermal Information                                   |    | 10.2 Layout Example                | 30              |

|   | 6.5 Electrical Characteristics: Voltage Output Mode 5     |    | 10.3 VQFN Package and Heat Sinking | 31              |

|   | 6.6 Electrical Characteristics: Current Output Mode 6     |    | 10.4 Power Dissipation             | 32              |

|   | 6.7 Electrical Characteristics: Operational Amplifier     | 11 | 器件和文档支持                            | 33              |

|   | (OPA)                                                     |    | 11.1 文档支持                          | 33              |

|   | 6.8 Electrical Characteristics: Instrumentation Amplifier |    | 11.2 接收文档更新通知                      | <mark>33</mark> |

|   | (IA) 8                                                    |    | 11.3 社区资源                          | 33              |

|   | 6.9 Electrical Characteristics: Current Monitor 9         |    | 11.4 商标                            | 33              |

|   | 6.10 Electrical Characteristics: Power and Digital 9      |    | 11.5 静电放电警告                        | 33              |

|   | 6.11 Typical Characteristics10                            |    | 11.6 Glossary                      | 33              |

| 7 | Detailed Description 16                                   | 12 | 机械、封装和可订购信息                        | 33              |

|   | 7.1 Overview                                              |    |                                    |                 |

|   |                                                           |    |                                    |                 |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期      | 修订版本 | 说明    |

|---------|------|-------|

| 2018年2月 | *    | 初始发行版 |

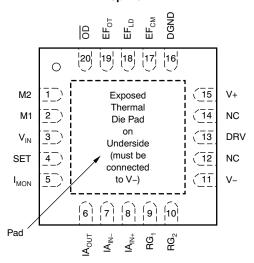

# 5 Pin Configuration and Functions

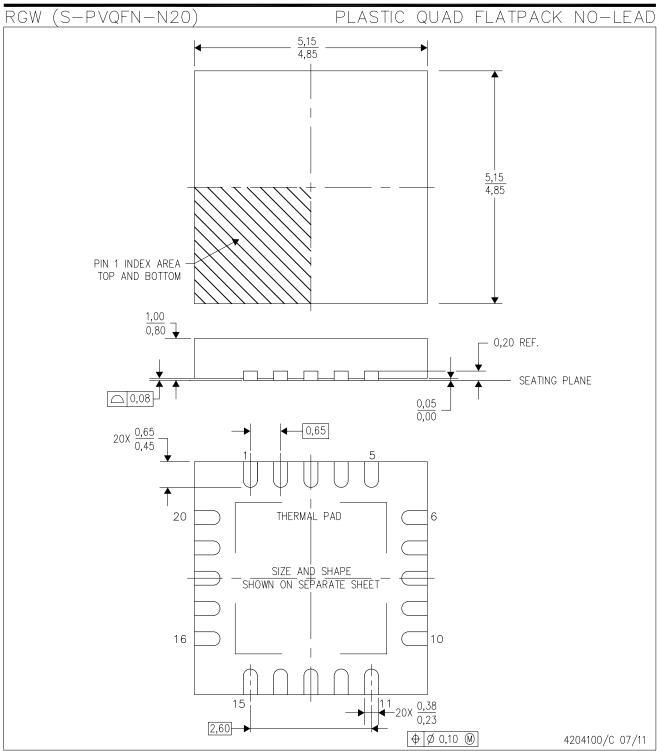

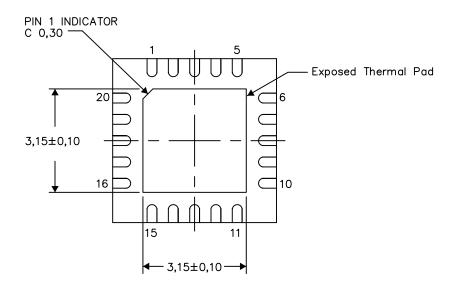

### RGW Package 20-Pin VQFN With Thermal Pad Top View

### **Pin Functions**

|     | PIN               | 1/0 | DECORPTION                                        |

|-----|-------------------|-----|---------------------------------------------------|

| NO. | NAME              | I/O | DESCRIPTION                                       |

| 1   | M2                | I   | Mode input                                        |

| 2   | M1                | ļ   | Mode input                                        |

| 3   | V <sub>IN</sub>   | I   | Noninverting signal input                         |

| 4   | SET               | I   | Input for gain setting; inverting input           |

| 5   | I <sub>MON</sub>  | 0   | Current monitor output                            |

| 6   | IA <sub>OUT</sub> | 0   | Instrumentation amplifier signal output           |

| 7   | IA <sub>IN</sub>  | I   | Instrumentation amplifier inverting input         |

| 8   | IA <sub>IN+</sub> | ļ   | Instrumentation amplifier noninverting input      |

| 9   | RG1               | I   | Instrumentation amplifier gain resistor           |

| 10  | RG2               | I   | Instrumentation amplifier gain resistor           |

| 11  | V-                | -   | Negative power supply                             |

| 12  | NC                | =   | No internal connection                            |

| 13  | DRV               | 0   | Operational amplifier output                      |

| 14  | NC                | -   | No internal connection                            |

| 15  | V+                | -   | Positive power supply                             |

| 16  | DGND              | -   | Ground for digital I/O                            |

| 17  | EF <sub>CM</sub>  | 0   | Error flag for common mode over range, active low |

| 18  | EF <sub>LD</sub>  | 0   | Error flag for load error, active low             |

| 19  | EF <sub>OT</sub>  | 0   | Error flag for over temperature, active low       |

| 20  | ŌD                | 1   | Output disable, disabled low                      |

| Pad | Exposed Pad       | -   | Exposed thermal pad must be connected to V-       |

# TEXAS INSTRUMENTS

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                  |                        | MIN         | MAX             | UNIT |

|----------------------------------|------------------------|-------------|-----------------|------|

| Supply voltage, V <sub>VSP</sub> |                        |             | +44             | V    |

| Cianal input tarminals           | Voltage <sup>(2)</sup> | (V-) - 0.5  | (V+) + 0.5      | V    |

| Signal input terminals           | Current <sup>(2)</sup> |             | ±25             | mA   |

| DGND                             |                        |             | ±25             | mA   |

| Output short circuit (3)         |                        | Conti       | nuous           |      |

| Operating temperature            |                        | <b>-</b> 55 | 125             | °C   |

| Junction temperature             |                        |             | 150             | °C   |

| Storage temperature, 7           | -<br>stg               | <b>-</b> 55 | <b>-</b> 55 125 |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            |                                                                                |                                                        | VALUE | UNIT |

|--------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|-------|------|

| V                                          | Floatroototic discharge                                                        | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000                                                  | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                             | MIN         | NOM MAX            | UNIT |

|-----------------------------|-------------|--------------------|------|

| Specified temperature range | -40         | 85                 | °C   |

| Operating temperature range | <b>-</b> 55 | 125 <sup>(1)</sup> | °C   |

<sup>(1)</sup>  $EF_{OT}$  not connected with  $\overline{OD}$ .

# 6.4 Thermal Information

|                      |                                              | XTR305     |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGW (VQFN) | UNIT |

|                      |                                              | 20 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 32.9       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 25.1       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 12.6       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 12.6       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.1        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5 V beyond the supply rails must be current limited. DRV pin allows a peak current of 50 mA. See the Output Protection section in Application and Implementation.

<sup>(3)</sup> See Driver Output Disable in Application and Implementation for thermal protection.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics: Voltage Output Mode

All specifications at  $T_A$  = 25°C,  $V_S$  = ±20 V,  $R_{LOAD}$  = 800  $\Omega$ ,  $R_{SET}$  = 2 k $\Omega$ ,  $R_{OS}$  = 2 k $\Omega$ ,  $V_{REF}$  = 4 V,  $R_{GAIN}$  = 10 k $\Omega$ , input signal span 0 V to 4 V, and  $C_C$  = 100 pF, unless otherwise noted.

|                      | PARAMETER                                                  | TEST CONDITIONS                                                                | MIN      | TYP   | MAX      | UNIT               |

|----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-------|----------|--------------------|

| OFFSET V             | OLTAGE                                                     |                                                                                |          |       | •        |                    |

| Vos                  | Offset voltage, RTI                                        |                                                                                |          | ±0.4  | ±2.5     | mV                 |

| dV <sub>OS</sub> /dT | Offset voltage vs temperature                              | $T_A = -40$ °C to 85°C                                                         |          | ±1.6  | ±10      | μV/°C              |

| PSRR                 | Offset voltage vs power supply                             | V <sub>S</sub> = ±5 V to ±22 V                                                 |          | ±0.2  | ±10      | μV/V               |

| INPUT VO             | LTAGE RANGE                                                |                                                                                |          |       |          |                    |

|                      | Nominal setup for ±10-V output                             | See Figure 35                                                                  |          |       |          |                    |

|                      | Input voltage for linear operation                         |                                                                                | (V-) + 3 |       | (V+) - 3 | V                  |

| NOISE                |                                                            |                                                                                |          |       | <u> </u> |                    |

|                      | Voltage noise, f = 0.1 Hz to 10 Hz, RTI                    |                                                                                |          | 3     |          | $\mu V_{PP}$       |

| e <sub>n</sub>       | Voltage noise density, f = 1 kHz, RTI                      |                                                                                |          | 40    |          | nV/√ <del>Hz</del> |

| OUTPUT               |                                                            |                                                                                |          |       | <u> </u> |                    |

|                      | Voltage output swing from rail                             | $I_{DRV} \le 15 \text{ mA}, T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$  | (V-) +3  |       | (V+) - 3 | V                  |

|                      | Gain nonlinearity                                          |                                                                                |          | ±0.01 | ±0.2     | %FS                |

|                      | Gain nonlinearity vs temperature                           | $T_A = -40$ °C to 85°C                                                         |          | ±0.1  | ±1       | ppm/°C             |

| I <sub>B</sub>       | Gain error                                                 |                                                                                |          | ±0.04 | ±0.2     | %FS                |

|                      | Gain error vs temperature                                  | $T_A = -40$ °C to 85°C                                                         |          | ±0.2  | ±1       | ppm/°C             |

|                      | Output impedance, dV <sub>DRV</sub> /dI <sub>DRV</sub>     |                                                                                |          | 7     |          | mΩ                 |

|                      | Output leakage current while output disabled               | $\overline{\text{OD}}$ pin = L <sup>(1)</sup> , T <sub>A</sub> = -40°C to 85°C |          | 30    |          | nA                 |

| I <sub>SC</sub>      | Short-circuit current                                      | $T_A = -40$ °C to 85°C                                                         | ±15      | ±20   | ±24      | mA                 |

| C <sub>LOAD</sub>    | Capacitive load drive                                      | $C_C = 10 \text{ nF}, R_C = 15^{(2)}$                                          |          | 1     |          | μF                 |

|                      | Rejection of voltage difference between GND1 and GND2, RTO |                                                                                |          | 130   |          | dB                 |

| FREQUEN              | ICY RESPONSE                                               |                                                                                |          |       | <u> </u> |                    |

|                      | Bandwidth <sup>(3)</sup>                                   | −3 dB, G = 5                                                                   |          | 300   |          | kHz                |

| CD                   | Slew rate <sup>(2)</sup>                                   |                                                                                |          | 1     |          | 1//                |

| SR                   | Siew rate —                                                | $C_C = 10 \text{ nF}, C_{LOAD} = 1 \mu\text{F}, R_C = 15 \Omega$               |          | 0.015 |          | V/μs               |

|                      | Settling time <sup>(2)(4)</sup> , 0.1%, small signal       | V <sub>DRV</sub> = ±1 V                                                        |          | 8     |          | μS                 |

|                      | Overload recovery time                                     | 50% overdrive                                                                  |          | 12    |          | μS                 |

<sup>(1)</sup> Output leakage includes input bias current of INA.

<sup>(2)</sup> Refer to Driving Capacitive Loads and Loop Compensation section in Application and Implementation.

<sup>(3)</sup> Small signal with no capacitive load.

<sup>(4) 8</sup> μs plus number of chopping periods. See Application and Implementation, Internal Current Sources, Switching Noise, and Settling Time section.

# 6.6 Electrical Characteristics: Current Output Mode

All specifications at T<sub>A</sub> = 25°C, V<sub>S</sub> =  $\pm 20$  V, R<sub>LOAD</sub> = 800  $\Omega$ , R<sub>SET</sub> = 2 k $\Omega$ , R<sub>OS</sub> = 2 k $\Omega$ , V<sub>REF</sub> = 4 V, input signal span 0 V to 4 V, and C<sub>C</sub> = 100 pF, unless otherwise noted.

|                      | PARAMETER                                                  | TEST CONDITIONS                                             | MIN      | TYP   | MAX      | UNIT               |

|----------------------|------------------------------------------------------------|-------------------------------------------------------------|----------|-------|----------|--------------------|

| OFFSET V             | OLTAGE                                                     |                                                             |          |       |          |                    |

| Vos                  | Input offset voltage                                       | Output current < 1 μA                                       |          | ±0.4  | ±2.5     | mV                 |

| dV <sub>OS</sub> /dT | Input offset voltage vs temperature                        |                                                             |          | ±1.5  | ±10      | μV/°C              |

| PSRR                 | Input offset voltage vs power supply                       | $V_S = \pm 5 \text{ V to } \pm 22 \text{ V}$                |          | ±0.2  | ±10      | μV/V               |

| INPUT VO             | LTAGE RANGE                                                |                                                             |          |       |          |                    |

|                      | Nominal setup for ±20-mA output                            | See Figure 36                                               |          |       |          |                    |

|                      | Maximum input voltage for linear operation                 |                                                             | (V-) + 3 |       | (V+) - 3 | V                  |

| NOISE                |                                                            |                                                             |          |       |          |                    |

|                      | Voltage noise, f = 0.1Hz to 10Hz, RTI                      |                                                             |          | 3     |          | $\mu V_{PP}$       |

| e <sub>n</sub>       | Voltage noise density, f = 1kHz, RTI                       |                                                             |          | 33    |          | nV/√ <del>Hz</del> |

| OUTPUT               |                                                            |                                                             |          |       |          |                    |

|                      | Compliance voltage swing from rail                         | I <sub>DRV</sub> = ±24 mA                                   | (V-) +3  |       | (V+) - 3 | V                  |

|                      | Output conductance (dl <sub>DRV</sub> /dV <sub>DRV</sub> ) | $dV_{DRV} = \pm 15 \text{ V}, dI_{DRV} = \pm 24 \text{ mA}$ |          | 0.7   |          | μ <b>A</b> /V      |

|                      | Transconductance                                           | See transfer function in Figure 36                          |          |       |          |                    |

|                      | Gain error                                                 | $I_{DRV} = \pm 24 \text{ mA}$                               |          | ±0.04 | ±0.2     | %FS                |

|                      | Gain error vs temperature                                  | $I_{DRV} = \pm 24 \text{ mA}$                               |          | ±3.6  | ±10      | ppm/°C             |

| I <sub>B</sub>       | Linearity error                                            | $I_{DRV} = \pm 24 \text{ mA}$                               |          | ±0.01 | ±0.2     | %FS                |

|                      | Linearity error vs temperature                             | $I_{DRV} = \pm 24 \text{ mA}$                               |          | ±1.5  | ±10      | ppm/°C             |

|                      | Output leakage current while output disabled               | OD pin = L                                                  |          | 0.6   |          | nA                 |

| I <sub>SC</sub>      | Short-circuit current                                      |                                                             | ±24.5    | ±32   | ±38.5    | mA                 |

| C <sub>LOAD</sub>    | Capacitive load drive <sup>(1)(2)</sup>                    |                                                             |          | 1     |          | μF                 |

| FREQUEN              | CY RESPONSE                                                |                                                             |          |       |          |                    |

|                      | Bandwidth                                                  | -3 dB                                                       |          | 160   |          | kHz                |

| SR                   | Slew rate (2)                                              | rate <sup>(2)</sup> 1.3                                     | mA/μs    |       |          |                    |

|                      | Settling time <sup>(2)(3)</sup> , 0.1%, Small Signal       | I <sub>DRV</sub> = ±2 mA                                    |          | 8     |          | μS                 |

|                      | Overload recovery time                                     | C <sub>LOAD</sub> = 0, 50% overdrive                        |          | 1     |          | μS                 |

<sup>(1)</sup> Refer to Driving Capacitive Loads and Loop Compensation section in Application and Implementation.

<sup>(2)</sup> With capacitive load, the slew rate can be limited by the short circuit current and the load error flag can trigger during slewing.

<sup>(3) 8</sup> μs plus number of chopping periods. See Application and Implementation, Internal Current Sources, Switching Noise, and Settling Time section.

# 6.7 Electrical Characteristics: Operational Amplifier (OPA)

All specifications at T<sub>A</sub> = 25°C, V<sub>S</sub> =  $\pm 20$  V, and R<sub>LOAD</sub> = 800  $\Omega$ , unless otherwise noted.

|                       | PARAMETER                                    | TEST CONDITIONS                                                       | MIN      | TYP                  | MAX      | UNIT    |

|-----------------------|----------------------------------------------|-----------------------------------------------------------------------|----------|----------------------|----------|---------|

| OFFSET V              | OLTAGE                                       |                                                                       |          |                      | <u> </u> |         |

| Vos                   | Offset voltage, RTI                          | I <sub>DRV</sub> = 0 A                                                |          | ±0.4                 | ±2.5     | mV      |

| dV <sub>OS</sub> /dT  | Offset voltage drift                         | $T_A = -40$ °C to 85°C                                                |          | ±1.5                 |          | μV/°C   |

| PSRR                  | Offset voltage vs power supply               | V <sub>S</sub> = ±5 V to ±22 V                                        |          | ±0.2                 | ±10      | μV/V    |

| INPUT VO              | LTAGE RANGE                                  |                                                                       |          |                      | <u> </u> |         |

| V <sub>CM</sub>       | Common-mode voltage range                    |                                                                       | (V-) + 3 |                      | (V+) - 3 | V       |

| CMRR                  | Common-mode rejection ratio                  | (V-) + 3 V < V <sub>CM</sub> < (V+) - 3 V                             | 95       | 126                  |          | dB      |

| INPUT BIA             | S CURRENT                                    |                                                                       |          |                      | <u> </u> |         |

| I <sub>B</sub>        | Input bias current                           |                                                                       |          | ±20                  | ±35      | nA      |

| Ios                   | Input offset current                         |                                                                       |          | ±0.3                 | ±10      | nA      |

| INPUT IME             | PEDANCE                                      |                                                                       |          |                      | <u> </u> |         |

|                       | Differential                                 |                                                                       |          | 10 <sup>8</sup>    5 |          | Ω    pF |

|                       | Common-mode                                  |                                                                       |          | 10 <sup>8</sup>    5 |          | Ω    pF |

| OPEN-LO               | OP GAIN                                      |                                                                       |          |                      | <u> </u> |         |

| A <sub>OL</sub>       | Open-loop voltage gain                       | $(V-) + 3 V < V_{DRV} < (V+) - 3 V,$<br>$I_{DRV} = \pm 24 \text{ mA}$ | 95       | 126                  |          | dB      |

| OUTPUT                |                                              |                                                                       |          |                      | <u> </u> |         |

|                       | Voltage output swing from rail               | $I_{DRV} = \pm 24 \text{ mA}$                                         | (V-) + 3 |                      | (V+) - 3 | V       |

| I <sub>LIMIT</sub>    | Short-circuit current                        | M2 = high                                                             | ±25.5    | ±32                  | ±38.5    | mA      |

| I <sub>LIMIT</sub>    |                                              | M2 = low                                                              | ±16      | ±20                  | ±24      | mA      |

| I <sub>LEAK_DRV</sub> | Output leakage current while output disabled | <u>OD</u> pin = L                                                     |          | 10                   |          | pA      |

| FREQUEN               | CY RESPONSE                                  |                                                                       |          |                      |          |         |

| GBW                   | Gain-bandwidth product                       | G = 1                                                                 |          | 2                    |          | MHz     |

| SR                    | Slew rate                                    |                                                                       |          | 1                    |          | V/μs    |

# STRUMENTS

# 6.8 Electrical Characteristics: Instrumentation Amplifier (IA)

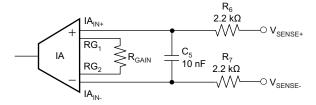

All specifications at  $T_A$  = 25°C,  $V_S$  = ±20 V,  $R_{IA}$  = 2 k $\Omega$ , and  $R_{GAIN}$  = 2 k $\Omega$ , unless otherwise noted. See Figure 37.

|                      | PARAMETER                                     | TEST CONDITIONS                                                                                                               | MIN      | TYP                  | MAX      | UNIT    |

|----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|----------|---------|

| OFFSET V             | /OLTAGE                                       |                                                                                                                               |          |                      | <u>'</u> |         |

| Vos                  | Offset voltage, RTI                           | I <sub>DRV</sub> = 0 A                                                                                                        |          | ±0.7                 | ±2.7     | mV      |

| dV <sub>OS</sub> /dT | Offset voltage vs temperature                 | $T_A = -40$ °C to 85°C                                                                                                        |          | ±2.4                 | ±10      | μV/°C   |

| PSRR                 | Offset voltage vs power supply                | $V_S = \pm 5 \text{ V to } \pm 22 \text{ V}$                                                                                  |          | ±0.8                 | ±10      | μV/V    |

| INPUT VO             | LTAGE RANGE                                   |                                                                                                                               |          |                      | 1        |         |

| $V_{CM}$             | Input voltage range                           |                                                                                                                               | (V-) + 3 |                      | (V+) - 3 | V       |

| CMRR                 | Common-mode rejection ratio                   | RTI                                                                                                                           | 100      | 130                  |          | dB      |

| INPUT BIA            | AS CURRENT                                    |                                                                                                                               |          |                      | 1        |         |

| I <sub>B</sub>       | Input bias current                            |                                                                                                                               |          | ±20                  | ±35      | nA      |

| Ios                  | Input offset current                          |                                                                                                                               |          | ±1                   | ±10      | nA      |

| INPUT IMI            | PEDANCE                                       |                                                                                                                               |          |                      |          |         |

|                      | Differential                                  |                                                                                                                               |          | 10 <sup>5</sup>    5 |          | Ω    pF |

|                      | Common-mode                                   |                                                                                                                               |          | 10 <sup>5</sup>    5 |          | Ω    pF |

| TRANSCO              | ONDUCTANCE (Gain) <sup>(1)</sup>              |                                                                                                                               |          |                      | 1        |         |

|                      | Transconductance error                        | IA <sub>OUT</sub> = ±2.4 mA, (V-) + 3 V <<br>V <sub>IAOUT</sub> < (V+) - 3 V                                                  |          | ±0.04                | ±0.1     | %FS     |

|                      | Transconductance error vs temperature         | $T_A = -40$ °C to 85°C                                                                                                        |          | ±0.2                 |          | ppm/°C  |

|                      | Linearity error                               | $(V-) + 3 V < V_{IAOUT} < (V+) - 3 V$                                                                                         |          | ±0.01                | ±0.1     | %FS     |

|                      | Input bias current to G1, G2                  |                                                                                                                               |          | ±20                  |          | nA      |

|                      | Input offset current to G1, G2 <sup>(2)</sup> |                                                                                                                               |          | ±1                   |          | nA      |

| OUTPUT               |                                               |                                                                                                                               |          |                      |          |         |

|                      | Output swing to the rail                      | $IA_{OUT} = \pm 2.4 \text{ mA}$                                                                                               | (V-) + 3 |                      | (V+) - 3 | V       |

|                      | Output impedance                              | $IA_{OUT} = \pm 2.4 \text{ mA}$                                                                                               |          | 600                  |          | mΩ      |

| _                    | Chart aireuit aurrent                         | M2 = High                                                                                                                     |          | ±7.2                 |          | mA      |

| I <sub>LIMIT</sub>   | Short-circuit current                         | M2 = Low                                                                                                                      |          | ±4.5                 |          | mA      |

| FREQUEN              | ICY RESPONSE                                  |                                                                                                                               |          |                      |          |         |

| GBW                  | Gain-bandwidth product                        | $G = 1$ , $R_{GAIN} = 10$ kΩ, $R_{IA} = 5$ kΩ                                                                                 |          | 1                    |          | MHz     |

| SR                   | Slew rate                                     | $G = 1$ , $R_{GAIN} = 10$ kΩ, $R_{IA} = 5$ kΩ                                                                                 |          | 1                    |          | V/μs    |

|                      | Settling time <sup>(3)</sup> , 0.1%           | $\begin{split} IA_{OUT} &= \pm 40~\mu\text{A},~R_{GAIN} = 10~k\Omega,\\ R_{IA} &= 5~k\Omega,~C_L = 100~p\text{F} \end{split}$ |          | 6                    |          | μS      |

|                      | Overload recovery time, 50%                   | $R_{GAIN} = 10 \text{ k}\Omega, R_{IA} = 15 \text{ k}\Omega,$<br>$C_L = 100 \text{ pF}$                                       |          | 10                   |          | μS      |

<sup>(1)</sup> Use equation: IA<sub>OUT</sub> = 2 (IA<sub>IN+</sub> - IA<sub>IN-</sub>) / R<sub>GAIN</sub>

(2) See typical characteristics curve (Figure 3).

(3) 6 μs plus number of chopping periods. See *Application and Implementation, Internal Current Sources, Switching Noise, and Settling* Time.

# 6.9 Electrical Characteristics: Current Monitor

All specifications at  $T_A = 25^{\circ}\text{C}$  and  $V_S = \pm 20 \text{ V}$ , unless otherwise noted. See Figure 37.

|                      | PARAMETER                         | TEST CONDITIONS                                                                 | MIN      | TYP   | MAX      | UNIT   |

|----------------------|-----------------------------------|---------------------------------------------------------------------------------|----------|-------|----------|--------|

| OUTPUT               |                                   |                                                                                 |          |       | ,        |        |

| Ios                  | Offset current                    | I <sub>DRV</sub> = 0 A                                                          |          | ±30   | ±100     | nA     |

| dl <sub>OS</sub> /dT | Offset current drift              | $T_A = -40$ °C to 85°C                                                          |          | ±0.05 |          | nA/°C  |

| PSRR                 | Offset current vs power supply    | $V_S = \pm 5 \text{ V to } \pm 22 \text{ V}$                                    |          | ±0.1  | ±10      | nA/V   |

|                      | Monitor output swing to the rail  | $I_{MON} = \pm 2.4 \text{ mA}$                                                  | (V-) + 3 |       | (V+) - 3 | V      |

|                      | Monitor output impedance          | $I_{MON} = \pm 2.4 \text{ mA}$                                                  |          | 200   |          | ΜΩ     |

| MONITOR              | R CURRENT GAIN <sup>(1)</sup>     |                                                                                 |          |       |          |        |

|                      | Current gain error                | I <sub>DRV</sub> = ±24 mA                                                       |          | ±0.04 | ±0.12    | %FS    |

|                      | Current gain error vs temperature | $I_{DRV} = \pm 24 \text{ mA}, T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ |          | ±3.6  |          | ppm/°C |

|                      | Linearity error                   | I <sub>DRV</sub> = ±24 mA                                                       |          | ±0.01 | ±0.1     | %FS    |

|                      | Linearity error vs temperature    | $I_{DRV} = \pm 24 \text{ mA}, T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ |          | ±1.5  |          | ppm/°C |

<sup>(1)</sup> Use equation:  $I_{MON} = I_{DRV} / 10$

# 6.10 Electrical Characteristics: Power and Digital

All specifications at  $T_A = 25$ °C and  $V_S = \pm 20$  V, unless otherwise noted. See Figure 37.

|        | PARAMETER                                                            | TEST CONDITIONS                                         | MIN | TYP   | MAX | UNIT |

|--------|----------------------------------------------------------------------|---------------------------------------------------------|-----|-------|-----|------|

| POWE   | R SUPPLY                                                             |                                                         | II. |       |     |      |

| Vs     | Specified voltage range                                              |                                                         | ±5  |       | ±20 | V    |

|        | Operating voltage range                                              |                                                         | ±5  |       | ±22 | V    |

| IQ     | Quiescent current                                                    | $I_{DRV} = IA_{OUT} = 0 A$                              |     | 1.8   | 2.3 | mA   |

|        | Quiescent current over temperature                                   | $T_A = -40$ °C to 85°C                                  |     |       | 2.8 | mA   |

| THERM  | MAL FLAG (EF <sub>OT</sub> ) OUTPUT                                  |                                                         |     |       |     |      |

|        | Alarm (EF <sub>OT</sub> pin LOW)                                     |                                                         |     | 140   |     | °C   |

|        | Return to normal operation (EF <sub>OT</sub> pin HIGH)               |                                                         |     | 125   |     | °C   |

| DIGITA | AL INPUTS (M1, M2, OD)                                               |                                                         |     |       | •   |      |

|        | V <sub>IL</sub> low-level input voltage                              |                                                         |     | ≤ 0.8 |     | V    |

|        | V <sub>IH</sub> high-level input voltage                             |                                                         |     | > 1.4 |     | V    |

|        | Input current                                                        |                                                         |     | ±1    |     | μΑ   |

| DIGITA | AL OUTPUTS (EF <sub>LD</sub> , EF <sub>CM</sub> , EF <sub>OT</sub> ) |                                                         |     |       |     |      |

|        | I <sub>OH</sub> high-level leakage current (opendrain)               |                                                         |     | -1.2  |     | μΑ   |

|        | V <sub>OL</sub> low-level output voltage                             | I <sub>OL</sub> = 5 mA                                  |     | 0.8   |     | V    |

|        | V <sub>OL</sub> low-level output voltage                             | I <sub>OL</sub> = 2.8 mA 0.4                            |     |       | V   |      |

| DIGITA | AL GROUND PIN <sup>(1)</sup>                                         |                                                         |     |       | ·   |      |

|        | Current input                                                        | M1 = M2 = L, $\overline{OD}$ = H, all digital outputs H |     | -25   |     | μА   |

<sup>(1)</sup> Use equation:  $(V-) \le DGND \le (V+) - 7 V$

# TEXAS INSTRUMENTS

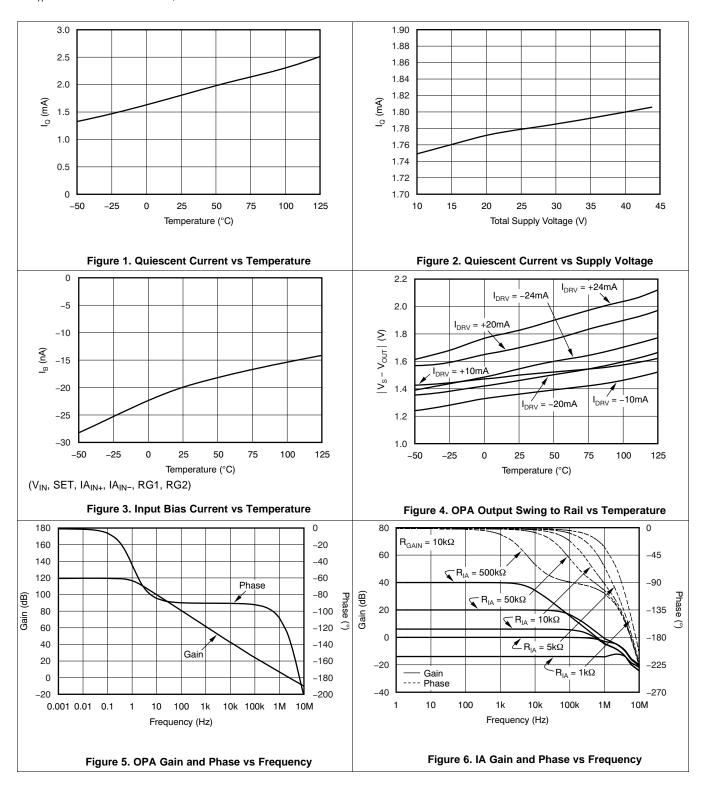

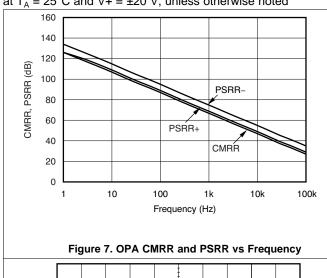

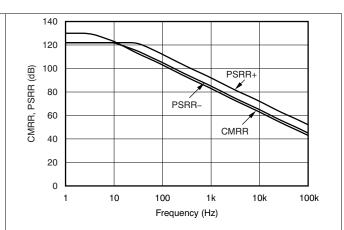

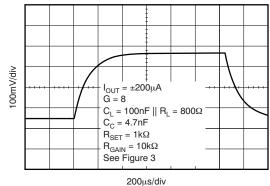

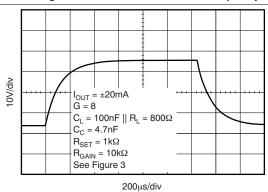

# 6.11 Typical Characteristics

at  $T_A = 25$ °C and V+ =  $\pm 20$  V, unless otherwise noted

# Typical Characteristics (continued)

Figure 8. IA CMRR and PSRR vs Frequency

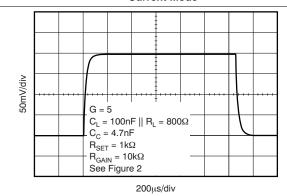

Figure 9. Small-Signal Step Response Current Mode

Figure 10. Large-Signal Step Response Current Mode

Figure 11. Small-Signal Step Response Voltage Mode

Figure 12. Large-Signal Step Response Voltage Mode

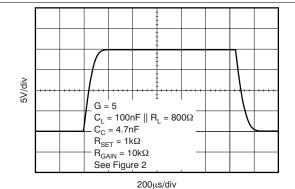

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and V+ =  $\pm 20$  V, unless otherwise noted

Figure 17. IA Input-Referred Noise Spectrum

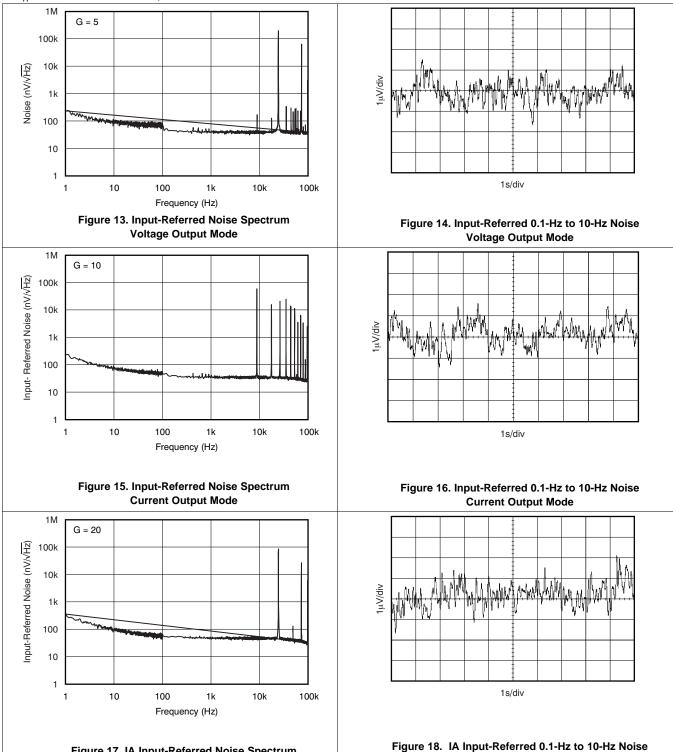

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and V+ =  $\pm 20$  V, unless otherwise noted

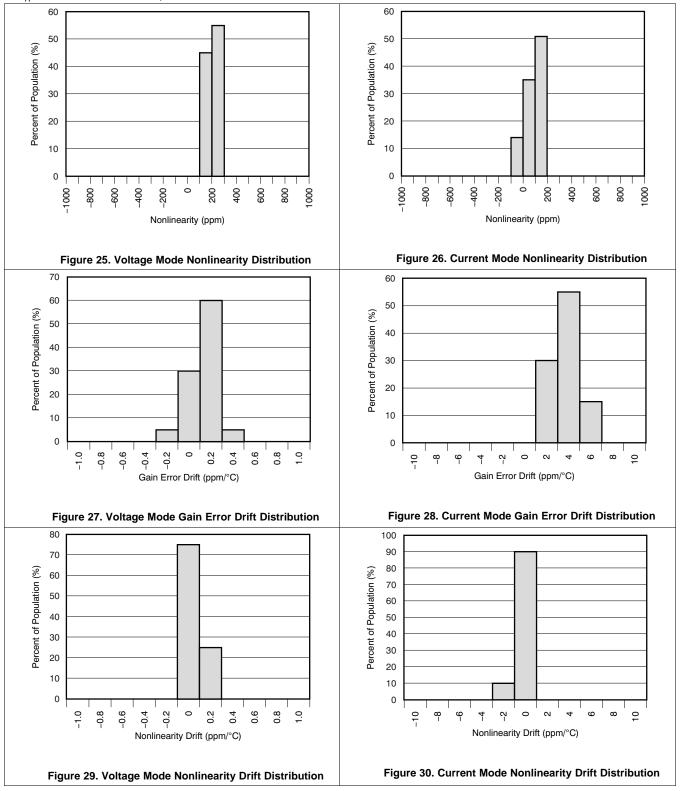

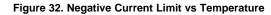

Figure 23. Voltage Mode Gain Error Distribution

Figure 24. Current Mode Gain Error Distribution

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and V+ =  $\pm 20$  V, unless otherwise noted

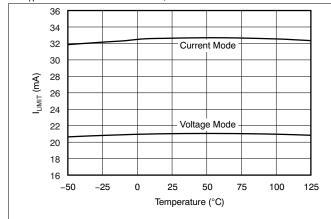

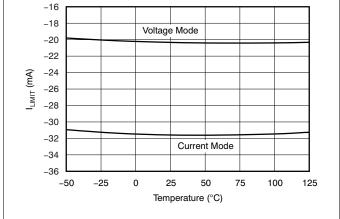

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and V+ =  $\pm 20$  V, unless otherwise noted

Figure 31. Positive Current Limit vs Temperature

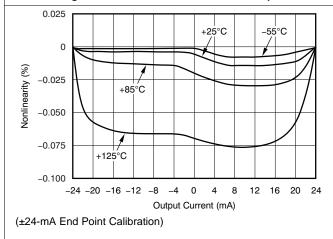

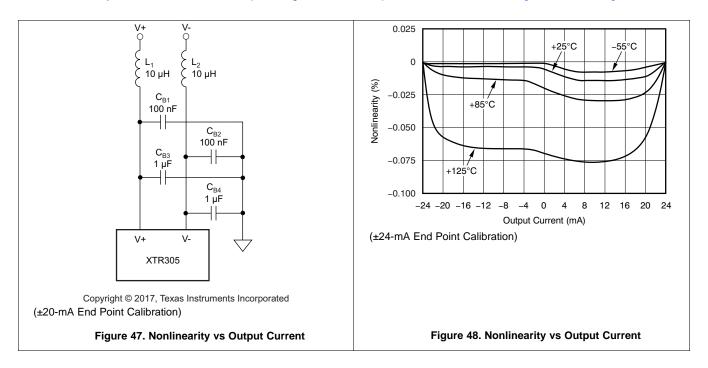

Figure 33. Nonlinearity vs Output Current

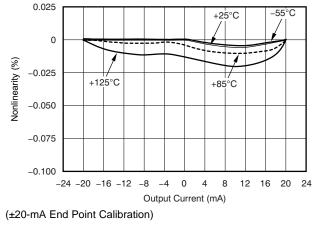

Figure 34. Nonlinearity vs Output Current

# TEXAS INSTRUMENTS

# 7 Detailed Description

# 7.1 Overview

Built on a robust high-voltage BiCMOS process, the XTR305 is designed to interface the 5-V or 3-V supply domain used for processors, signal converters, and amplifiers to the high-voltage and high-current industrial signal environment. The device is specified for up to  $\pm 20$ -V supply, but can also be powered asymmetrically (for example,  $\pm 24$  V and  $\pm 5$  V). It is designed to allow insertion of external circuit protection elements and drive large capacitive loads.

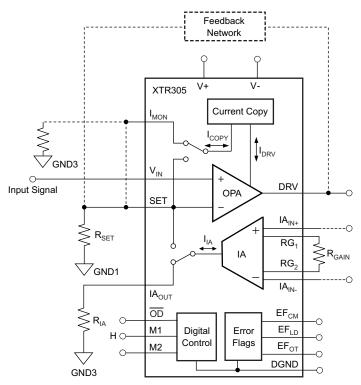

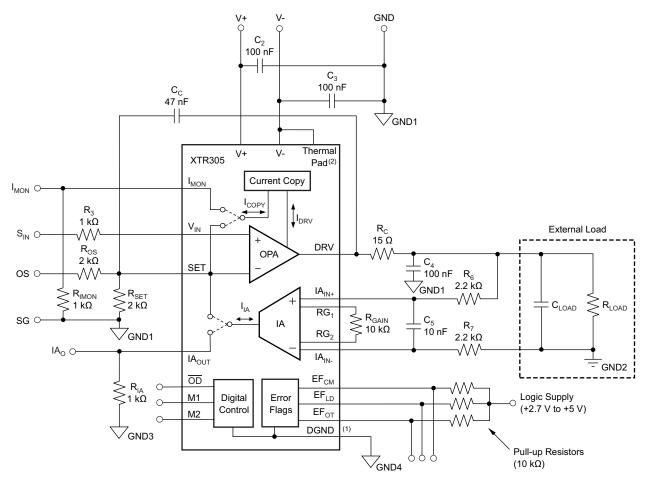

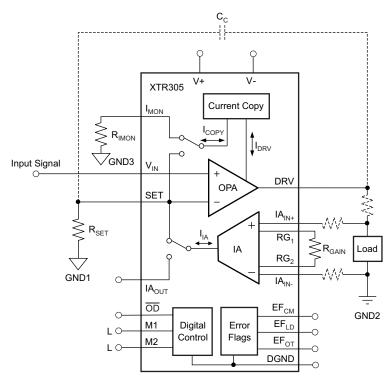

# 7.2 Functional Block Diagrams

Copyright © 2017, Texas Instruments Incorporated

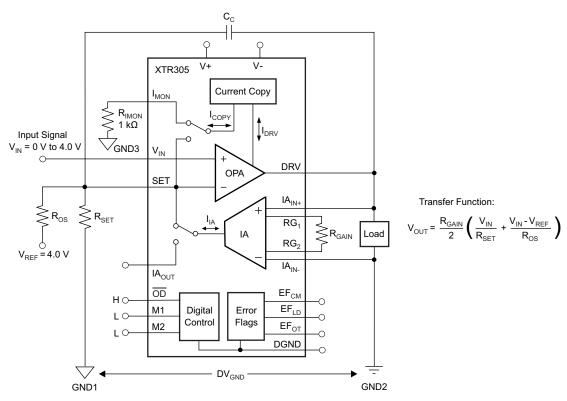

Figure 35. Standard Circuit for Voltage Output Mode

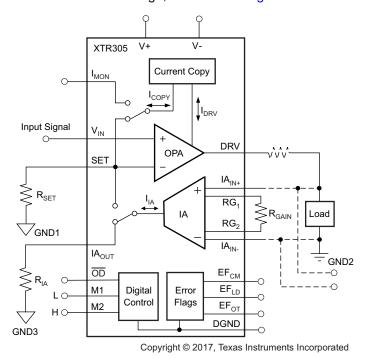

# **Functional Block Diagrams (continued)**

Copyright © 2017, Texas Instruments Incorporated

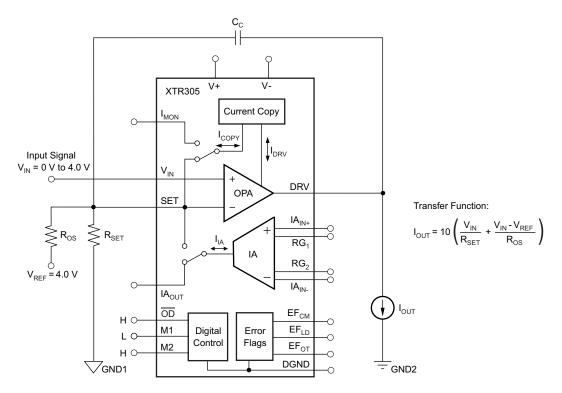

Figure 36. Standard Circuit for Current Output Mode

# TEXAS INSTRUMENTS

# **Functional Block Diagrams (continued)**

Copyright © 2017, Texas Instruments Incorporated

Figure 37. Standard Circuit for Externally Configured Mode

# 7.3 Feature Description

### 7.3.1 Functional Features

The XTR305 provides two basic functional blocks: an instrumentation amplifier (IA) and a driver that is a unique operational amplifier (OPA) for current or voltage output. This combination represents an analog output stage which can be digitally configured to provide either current or voltage output to the same terminal pin. Alternatively, it can be configured for independent measurement channels.

Three open collector error signals are provided to indicate output related errors such as overcurrent or open-load ( $EF_{LD}$ ) or exceeding the common-mode input range at the IA inputs ( $EF_{CM}$ ). An overtemperature flag ( $EF_{OT}$ ) can be used to control output disable to protect the circuit. The monitor outputs ( $I_{MON}$  and  $IA_{OUT}$ ) and the error flags offer optimal testability during operation and configuration. The  $I_{MON}$  output represents the current flowing into the load in voltage output mode, while the  $IA_{OUT}$  represents the voltage across the connectors in current output mode. Both monitor outputs can be connected together when used in current or voltage output mode because the monitor signals are multiplexed accordingly.

### 7.3.2 Current Monitor

In current output mode (M2 = high), the XTR305 provides high output impedance. A precision current mirror generates an exact 1/10th copy of the output current and this current is either routed to the summing junction of the OPA to close the feedback loop (in the current output mode) or to the  $I_{MON}$  pin for output current monitoring in other operating modes.

The high accuracy and stability of this current split results from a cycling chopper technique. This design eliminates the need for a precise shunt resistor or a precise shunt voltage measurement, which would require high common-mode rejection performance.

www.ti.com.cn ZHCSHO6 – FEBRUARY 2018

# **Feature Description (continued)**

During a saturation condition of the DRV output (the error flag is active), the monitor output  $(I_{MON})$  shows a current peak because the loop opens. Glitches from the current mirror chopper appear during this time in the monitor signal. This part of the signal cannot be used for measurement.

### 7.3.3 Error Flags

The XTR305 is designed for testability of its proper function and allows observation of the conditions at the load connection without disrupting service.

If the output signal is not in accordance to the transfer function, an error flag is activated (limited by the dynamic response capabilities). These error flags are in addition to the monitor outputs, I<sub>MON</sub> and IA<sub>OUT</sub>, which allow the momentary output current (in voltage mode) or output voltage (in current mode) to be read back.

This combination of error flag and monitor signal allows easy observation of the XTR305 for function and working condition, providing the basis for not only remote control, but also for remote diagnosis.

All error flags of the XTR305 have open collector outputs with a weak pullup of approximately 1  $\mu$ A to an internal 5 V. External pullup resistors to the logic voltage are required when driving 3-V or 5-V logic.

The output sink current should not exceed 5 mA. This is just enough to directly drive optical-couplers, but a current-limiting resistor is required.

There are three error flags:

- 1. IA Common-Mode Over Range (EF<sub>CM</sub>): goes low as soon as the inputs of the IA reach the limits of the linear operation for the input voltage. This flag shows noise from the saturated current mirrors which can be filtered with a capacitor to GND.

- Load Error (EF<sub>LD</sub>): indicates fault conditions driving voltage or current into the load. In voltage output mode

it monitors the voltage limits of the output swing and the current limit condition caused from short or low load

resistance. In current output mode it indicates a saturation into the supply rails from a high load resistance or

open load.

- 3. Overtemperature Flag (EF<sub>OT</sub>): a digital output that goes low if the chip temperature reaches a temperature of 140°C and resets as soon as it cools down to 125°C. It does not automatically shut down the output; it allows the user system to take action on the situation. If desired, this output can be connected to output disable (OD) which disables the output and therefore removes the source of power. This connection acts like an automatic shut down, but requires a 2.2-kΩ external pullup resistor to safely override the internal current sources. The IA channel is not affected, which allows continuous observation of the voltage at the output.

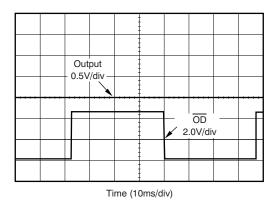

#### 7.3.4 Power On/Off Glitch

When power is turned on or off, most analog amplifiers generate some glitching of the output because of internal circuit thresholds and capacitive charges. Characteristics of the supply voltage, as well as its rise and fall time, directly influence output glitches. Load resistance and capacitive load also affect the amplitude.

The output disable control  $(\overline{OD})$  cannot fully suppress glitches during power-on and power-off, but reduces the energy significantly. The glitch consists of a small amount of current and capacitive charge (voltage) that reacts with the resistive and capacitive load. The bias current of the IA inputs that are normally connected to the output also generate a voltage across the load.

# **Feature Description (continued)**

Figure 38 indicates no glitches when transitioning between disable and enable. This measurement is made with a load resistance of 1 k $\Omega$  and tested in the circuit configuration of Figure 40.

Figure 38. Output Signal During Toggle of OD

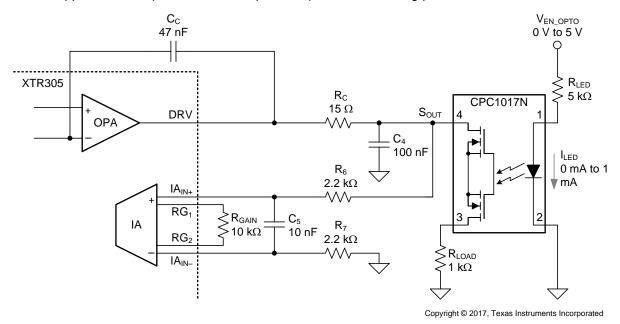

When the power is off or with low supply, the output is diode clamped to the momentary supply voltage, but can float while output disabled within those limits unless terminated. Only an external switch (relays or opto-relays) can isolate the output under such conditions. Refer to Figure 39 for an illustration of this configuration. The same consideration applies if low impedance zero output is required, even during power off.

Figure 39. Example for Opto-Relay Output Isolation

### 7.4 Device Functional Modes

The XTR305 has a three functional modes: voltage output mode as shown in Figure 35, current output mode as shown in Figure 36, and externally configured mode as shown in Figure 37.

ZHCSHO6-FEBRUARY 2018 www.ti.com.cn

# **Application and Implementation**

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The following sections provide details regarding the typical application of the XTR305 using three different functional modes: voltage output mode as shown in Figure 35, current output mode as shown in Figure 36, and externally configured mode as shown in Figure 37.

# 8.2 Typical Application

Copyright © 2017, Texas Instruments Incorporated

- (1) See the Electrical Characteristics: Power and Digital and Digital I/O and Ground Considerations section for operating limits of DGND.

- Connect thermal pad to V-.

Figure 40. Standard Circuit Configuration

# TEXAS INSTRUMENTS

### 8.2.1 Design Requirements

Consider the following information during XTR305 circuit configuration:

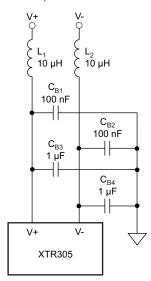

- Recommended bypassing: 100 nF or more for supply bypassing at each supply.

- $R_{IMON}$  can be in the  $k\Omega$  range or short-circuited if not used. Do not leave this current output unconnected it would saturate the internal current source. The current at this  $I_{MON}$  output is  $I_{DRV}$  / 10. Therefore,  $V_{IMON} = R_{IMON}$  ( $I_{DRV}$  /1 0).

- R<sub>3</sub> is not required but can match R<sub>SET</sub> (or R<sub>SET</sub>||R<sub>OS</sub>) to compensate for the bias current.

- $R_{IA}$  can be short-circuited if not used. Do not leave this current output unconnected.  $R_{GAIN}$  is selected to 10  $k\Omega$  to match the output of 10 V with 20 mA for the equal input signal.

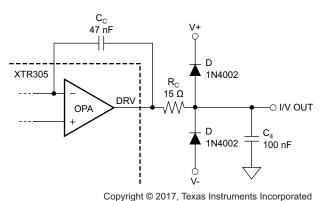

- R<sub>C</sub> ensures stability for unknown load conditions and limits the current into the internal protection diodes. C<sub>4</sub> helps protect the device. Overvoltage clamp diodes (standard 1N4002) might be necessary to protect the output.

- R<sub>6</sub>, R<sub>7</sub>, and C<sub>5</sub> protect the IA.

- R<sub>LOAD</sub> and C<sub>LOAD</sub> represent the load resistance and load capacitance.

- R<sub>SET</sub> defines the transfer gain. It can be split to allow a signal offset and, therefore, allow a 5-V single-supply digital-to-analog converter (DAC) to control a ±10-V or ±20-mA output signal.

The XTR305 can be used with asymmetric supply voltages; however, the minimum negative supply voltage must be equal to or more negative than -3 V (typically -5 V). This supply value ensures proper control of 0 V and 0 mA with wire resistance, ground offsets, and noise added to the output. For positive output signals, the current requirement from this negative voltage source is less than 5 mA.

GND1 through GND4 must be selected to fulfill specified operating ranges. DGND must be in the range of  $(V-) \le DGND \le (V+) -7 \ V$ .

### 8.2.2 Detailed Design Procedure

### 8.2.2.1 Voltage Output Mode

In voltage output mode (M1 and M2 are connected low or left unconnected), the feedback loop through the IA provides high impedance remote sensing of the voltage at the destination, compensating the resistance of a protection circuit, switches, wiring, and connector resistance. The output of the IA is a current that is proportional to the input voltage. This current is internally routed to the OPA summing junction through a multiplexer, as shown in Figure 41.

A 1:10 copy of the output current of the OPA can be monitored at the  $I_{MON}$  pin. This output current and the known output voltage can be used to calculate the load resistance or load power.

During an output short-circuit or an overcurrent condition the XTR305 output current is limited and  $EF_{LD}$  (load error, active low) flag is activated.

Copyright © 2017, Texas Instruments Incorporated

Figure 41. Simplified Voltage Output Mode Configuration

Applications not requiring the remote sense feature can use the OPA in stand-alone operation (M1 = high). In this case, the IA is available as a separate input channel.

The IA gain can be set by two resistors,  $R_{GAIN}$  and  $R_{SET}$  (Equation 1):

$$V_{OUT} = \frac{R_{GAIN}}{2R_{SET}} V_{IN}$$

(1)

or when adding an offset, V<sub>REF</sub>, to get bidirectional output with a single-ended input shown in Equation 2:

$$V_{OUT} = \frac{R_{GAIN}}{2} \left( \frac{V_{IN}}{R_{SET}} + \frac{V_{IN} - V_{REF}}{R_{OS}} \right)$$

(2)

The  $R_{SET}$  resistor is also used in current output mode. Therefore, it is useful to define  $R_{SET}$  for the current mode, then set the ratio between current and voltage span with  $R_{GAIN}$ .

### 8.2.2.2 Current Output Mode

The XTR305 does not require a shunt resistor for current control because it uses a precise current mirror arrangement.

In current output mode (M1 connected low, or left unconnected and M2 connected high), a precise copy of 1/10th of the output is internally routed back to the summing junction of the OPA through a multiplexer, closing the control loop for the output current.

The OPA driver can deliver more than ±24 mA within a wide output voltage range. An open-output condition or high-impedance load that prevents the flow of the required current activates the EF<sub>LD</sub> flag and the IA can become overloaded and draw greater than 7-mA saturation current.

While in current output mode, a current ( $I_{IA}$ ) that is proportional to the voltage at the IA input is routed to  $IA_{OUT}$  and can be used to monitor the load voltage. A resistor converts this current into voltage. This arrangement makes level shifting easy.

Alternatively, the IA can be used as an independent monitoring channel. If this output is not used, connect it to GND to maintain proper function of the monitor stage, as shown in Figure 42.

Figure 42. Simplified Current Output Mode Configuration

The transconductance (gain) can be set by the resistor, R<sub>SET</sub>, according to Equation 3:

$$I_{OUT} = \frac{10}{R_{SET}} V_{IN}$$

(3)

or when adding an offset V<sub>REF</sub> to get bidirectional output with a single-ended input shown in Equation 4:

$$I_{OUT} = 10 \left( \frac{V_{IN}}{R_{SET}} + \frac{V_{IN} - V_{REF}}{R_{OS}} \right)$$

(4)

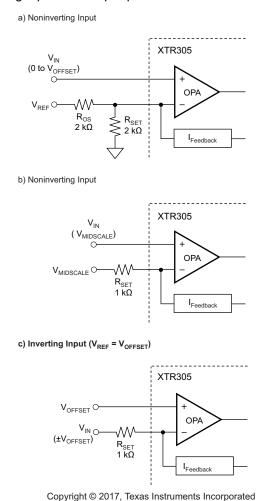

# 8.2.2.3 Input Signal Connection

It is possible to drive the XTR305 with a unidirectional input signal and still get a bidirectional output by adding an additional resistor,  $R_{OS}$ , and an offset voltage signal,  $V_{REF}$ . It can be a mid-point voltage or a signal to shift the output voltage to a desired value.

This design is illustrated in Figure 43a, Figure 43b, and Figure 43c. As with a normal operational amplifier, there are several options for offset-shift circuits. The input can be connected for inverting or noninverting gain. Unlike many op amp input circuits, however, this configuration uses current feedback, which removes the voltage relationship between the noninverting input and output potential because there is no feedback resistor.

Figure 43. Circuit Options for Op Amp Output Level Shifting

The input bias current effect on the offset voltage can be reduced by connecting a resistor in series with the positive input that matches the approximate resistance at the negative input. This resistor placed close to the input pin acts as a damping element and makes the design less sensitive to RF noise. See R<sub>3</sub> in Figure 40.

### 8.2.2.4 Externally-Configured Mode: OPA and IA

It is possible to use the precision of the operational amplifier (OPA) and instrumentation amplifier (IA) independently from each other by configuring the digital control pins (M1 high). In this mode, the IA output current is routed to  $I_{MON}$ , as shown in Figure 37.

This mode allows external configuration of the analog signal routing and feedback loop.

The current output IA has high input impedance, low offset voltage and drift, and very high common-mode rejection ratio. An external resistor ( $R_{IA}$ ) can be used to convert the output current of the IA ( $I_{IA}$ ) to an output voltage. The gain is given by Equation 5:

$$I_{IA} = \frac{2}{R_{GAIN}} V_{IN} \text{ or } V_{IA} = \frac{2R_{IA}}{R_{GAIN}} V_{IN}$$

(5)

The OPA provides low drift and high voltage output swing that can be used like a common operational amplifier by connecting a feedback network around it. In this mode, the copy of the output current is available at the I<sub>MON</sub> pin (it includes the current into the feedback network). It provides an output current limit for protection, which can be set between two ranges by M2. The error flag indicates an overcurrent condition, as well as indicating driving the output into the supply rails.

Alternatively, the feedback can be closed through the I<sub>MON</sub> pin to create a precise voltage-to-current converter.

### 8.2.2.5 Driver Output Disable

The OPA output (DRV) can be switched to a high-impedance mode by driving the  $\overline{\text{OD}}$  control pin low. This input can be connected to the overtemperature flag,  $\text{EF}_{\text{OT}}$ , and a pullup resistor to protect the IC from overtemperature by disconnecting the load.

The output disable mode can be used to sense and measure the voltage at the IA input pins without loading from the DRV output. This mode allows testing of any voltage present at the I/O connector. However, consider the bias current of the IA input pins.

The digital control inputs, M1 and M2, set the four operation modes of the XTR305 as shown in Table 1. When M1 is asserted low, M2 determines voltage or current mode and the corresponding appropriate current limit ( $I_{SC}$ ) setting. When M1 is high, the internal feedback connections are opened;  $IA_{OUT}$  and  $I_{MON}$  are both connected to the output pins; and M2 only determines the current limit ( $I_{SC}$ ) setting.

M1 and M2 are pulled low internally with 1  $\mu$ A. Terminate these two pins to avoid noise coupling. Output disable  $(\overline{OD})$  is internally pulled high with approximately 1  $\mu$ A. When connecting  $\overline{OD}$  to EF<sub>OT</sub>, a 2.2-kΩ pullup resistor is recommended.

| M1 | M2 | MODE             | DESCRIPTION                                                      |

|----|----|------------------|------------------------------------------------------------------|

| L  | L  | $V_{OUT}$        | Voltage output mode, I <sub>SC</sub> = 20 mA                     |

| L  | Н  | I <sub>OUT</sub> | Current output mode, I <sub>SC</sub> = 32 mA                     |

| Н  | L  | Ext              | IA and I <sub>MON</sub> on external pins, I <sub>SC</sub> = 20 A |

| Н  | Н  | Ext              | IA and $I_{MON}$ on external pins, $I_{SC} = 32$ mA              |

Table 1. Summary of Configuration Modes<sup>(1)</sup>

# 8.2.2.6 Driving Capacitive Loads and Loop Compensation

For normal operation, the driver OPA and the IA are connected in a closed loop for voltage output. In current output mode, the current copy closes the loop directly.

In current output mode, loop compensation is not critical, even for large capacitive loads. However, in voltage output mode, the capacitive load, together with the source impedance and the impedance of the protection circuit, generates additional phase lag. The IA input might also be protected by a low-pass filter that influences phase in the closed loop.

The loop compensation low-pass filter consists of  $C_C$  and the parallel resistance of  $R_{OS}$  and  $R_{SET}$ . For loop stability with large capacitive load, the external phase shift has to be added to the OPA phase. With  $C_C$ , the voltage gain of the OPA has to approach zero at the frequency where the total phase approaches 180° + 135°.

The best stability for large capacitive loads is provided by adding a small resistor,  $R_C$  (15  $\Omega$ ). See the *Output Protection* section.

An empirical method of evaluation is using a square wave input signal and observing the settling after transients. Use small signal amplitudes only—steep signal edges cause excessive current to flow into the capacitive load and may activate the current limit, which hides or prevents oscillation. A small-signal oscillation can be hidden from large capacitive loads, but observing the  $I_{MON}$  output on an appropriate resistor (use a similar value like  $R_{SET}||R_{OS}||$ ) would indicate stability issues. Note that noise pulses at  $I_{MON}$  during overload (EF<sub>LD</sub> active) are normal and are caused by cycling of the current mirror.

<sup>(1)</sup>  $\overline{OD}$  is a control pin independent of M1 or M2.

The voltage output mode includes the IA in the loop. An additional low-pass filter in the input reverses the phase and therefore increases the signal bandwidth of the loop, but also increases the delay. Again, loop stability has to be observed. Overloading the IA disconnects the closed loop and the output voltage rails.

### 8.2.2.7 Internal Current Sources, Switching Noise, and Settling Time

The accuracy of the current output mode and the DC performance of the IA rely on dynamically-matched current mirrors.

Identical current sources are rotated to average out mismatch errors. It can take several clock cycles of the internal 100-kHz oscillator (or a submultiple of that frequency) to reach full accuracy. This may dominate the settling time to the 0.1% accuracy level and can be as much as 100 µs in current output mode or 40 µs in voltage output mode.

A small portion of the switching glitches appear at the DRV output, and also at the I<sub>MON</sub> and IA<sub>MON</sub> outputs. The standard circuit configuration, with R<sub>C</sub>, C<sub>4</sub>, and C<sub>C</sub>, which are required for loop compensation and output protection, also helps reduce the noise to negligible levels at the signal output. If necessary, the monitor outputs can be filtered with a shunt capacitor.

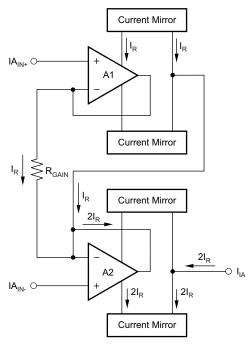

### 8.2.2.8 IA Structure, Voltage Monitor

The instrumentation amplifier has high-impedance NPN transistor inputs that do not load the output signal, which is especially important in current output mode. The output signal is a controlled current that is multiplexed either to the SET pin (to close the voltage output loop) or to IA<sub>OUT</sub> (for external access).

The principal circuit is shown in Figure 44. The two input buffer amplifiers reproduce the input difference voltage across R<sub>GAIN</sub>. The resulting current through this resistor is bidirectionally mirrored to the output. That mirroring results in the transfer function of Equation 6:

$$I_{IA} = IA_{OUT} = 2 \frac{(IA_{IN+} - IA_{IN-})}{R_{GAIN}}$$

(6)

The accuracy and drift of R<sub>GAIN</sub> defines the accuracy of the voltage to current conversion. The high accuracy and stability of the current mirrors result from a cycling chopper technique.

Copyright © 2017, Texas Instruments Incorporated

Figure 44. IA Block Diagram

ZHCSH06 – FEBRUARY 2018 www.ti.com.cn

The output current, IA<sub>OUT</sub>, of the instrumentation amplifier is limited to protect the internal circuitry. This current limit has two settings controlled by the state of M2 (see *Electrical Characteristics: Instrumentation Amplifier (IA)*, Short-Circuit Current specification).

### **NOTE**

If R<sub>SET</sub> is too small, the current output limitation of the instrumentation amplifier can disrupt the closed loop of the XTR305 in voltage output mode.

With M2 = low, the nominal  $R_{GAIN}$  of 10  $k\Omega$  allows an input voltage of 20  $V_{PP}$ , which produces an output current of 4  $mA_{PP}$ . When using lower resistors for  $R_{GAIN}$  that can allow higher currents, the IA output current limitation must be taken into account.

# 8.2.2.9 Digital I/O and Ground Considerations

The XTR305 offers voltage output mode, current output mode, external configuration, and instrumentation mode (voltage input). In addition, the internal feedback mode can be disconnected and external loop connections can be made. These modes are controlled by M1 and M2 (see Table 1). The OD input pin controls enable or disable of the output stage (OD is active low).

The digital I/O is referenced to DGND and signals on this pin must remain within 5 V of the DGND potential. This DGND pin carries the output low-current (sink current) of the logic outputs. DGND can be connected to a potential within the supply voltage but needs to be 8 V below the positive supply. Proper connection avoids current from the digital outputs flowing into the analog ground.

#### CAUTION

The DGND has normally reverse-biased diodes connected to the supply. Therefore, high and destructive currents could flow if DGND is driven beyond the supply rails by more than a diode forward voltage. Avoid this condition during power on and power off.

# 8.2.2.10 Output Protection

The XTR305 is intended to operate in a harsh industrial environment. Therefore, a robust semiconductor process was chosen for this design. However, some external protection is still required.

The instrumentation amplifier inputs can be protected by external resistors that limit current into the protection cell behind the IC pins, as shown in Figure 45. This cell conducts to the power-supply connection through a diode as soon as the input voltage exceeds the supply voltage. The circuit configuration example shows how to arrange these two external resistors.

The bias current is best cancelled if both resistors are equal. The additional capacitor reduces RF noise in the input signal to the IA.

Figure 45. Current-Limiting Resistors

The load connection to the DRV output must be low impedance; therefore, external protection diodes may be necessary to handle excessive currents, as shown in Figure 46. The internal protection diodes start to conduct earlier than a normal external PN-type diode because they are affected by the higher die temperature. Therefore, either Schottky diodes are required, or an additional resistor ( $R_C$ ) can be placed in series with the input. An example of this protection is shown in Figure 46. Assuming the standard diodes limit the voltage to 1.4 V and the internal diodes clamp at 0.7 V, this resistor can limit the current into the internal protection diodes to 50 mA shown in Equation 7:

$$\frac{(1.4V - 0.7V)}{15\Omega} = 47\text{mA} \tag{7}$$

R<sub>C</sub> is also part of the recommended loop compensation. C<sub>4</sub> helps protect the output against RFI and high-voltage spikes.

Copyright @ 2017, Texas instruments incorporated

Figure 46. Example for DRV Output Protection

# 8.2.3 Application Curves

The nonlinearity of the XTR305 when operating in current output mode is shown in Figure 47 and Figure 48.

# 9 Power Supply Recommendations

Built on a robust high-voltage BiCMOS process, the XTR305 is designed to interface the 5-V or 3-V supply domain used for processors, signal converters, and amplifiers to the high-voltage and high-current industrial signal environment. The device is specified for up to ±20-V supply, but can also be powered asymmetrically (for example, +24 V and -5 V). XTR305 is designed to allow insertion of external circuit protection elements and drive large capacitive loads.

# TEXAS INSTRUMENTS

# 10 Layout

# 10.1 Layout Guidelines

Supply bypass capacitors must be close to the package and connected with low-impedance conductors. Avoid noise coupled into  $R_{GAIN}$ , and observe wiring resistance. For thermal management, see the VQFN Package and Heat Sinking section.

Layout for the XTR305 is not critical; however, its internal current chopping works best with good (low dynamic impedance) supply decoupling. Therefore, avoid through-hole contacts in the connection to the bypass capacitors or use multiple through-hole contacts. Switching noise from power supplies should be filtered enough to reduce influence on the circuit. Small resistors ( $2-\Omega$ , for example) or damping inductors in series with the supply connection (between the DC-DC converter and the XTR circuit) act as a decoupling filter together with the bypass capacitor as shown in Figure 49.

Resistors connected close to the input pins help dampen environmental noise coupled into conductor traces. Therefore, place the OPA input- and IA input-related resistors close to the package. Also, avoid additional wire resistance in series to  $R_{SET}$ ,  $R_{OS}$ , and  $R_{GAIN}$  (observe the reliability of the through-hole contacts), because this resistance could produce gain and offset error as well as drift; 1  $\Omega$  is already 0.1% of the 1-k $\Omega$  resistor.

The exposed lead-frame die pad on the bottom of the package must be connected to V-, pin 11 (see the VQFN Package and Heat Sinking section for more details).

Copyright © 2017, Texas Instruments Incorporated

Figure 49. Suggested Supply Decoupling for Noisy Chopper-Type Supplies

# 10.2 Layout Example

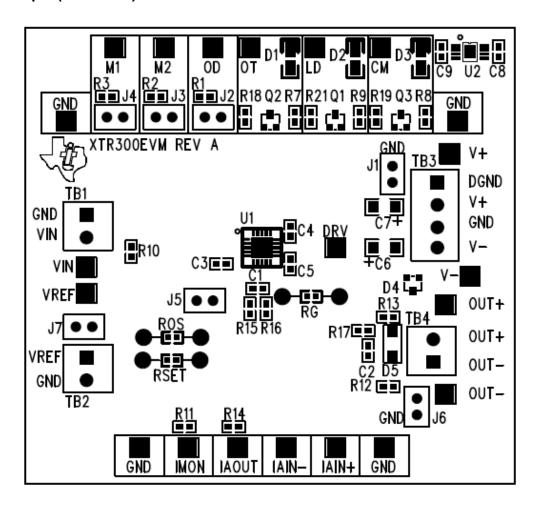

A detailed layout example can be found in the technical document *XTR300EVM*. This document is available for download at www.ti.com. The example layout is also shown in Figure 50.

# **Layout Example (continued)**

Figure 50. Layout Example

# 10.3 VQFN Package and Heat Sinking

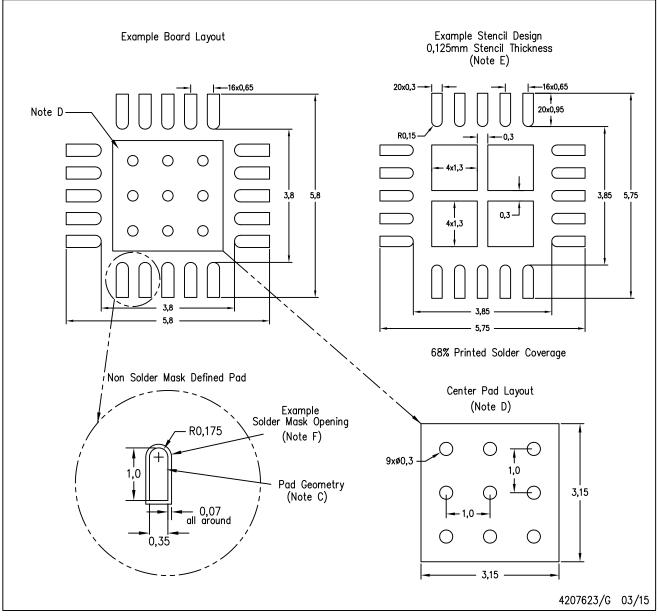

The XTR305 is available in a VQFN package. This leadless, near-chip-scale package maximizes board space and enhances thermal and electrical characteristics of the device through an exposed thermal pad.

Packages with an exposed thermal pad are specifically designed to provide excellent power dissipation, but printed circuit board (PCB) layout greatly influences overall heat dissipation. The thermal resistance from junction-to-ambient ( $\theta_{JA}$ ) is specified for the packages with the exposed thermal pad soldered to a normalized PCB, as described in the technical brief *PowerPAD<sup>TM</sup> Thermally-Enhanced Package*. See also *EIA/JEDEC Specifications JESD51-0 to 7, VQFN/SON PCB Attachment*, and *Quad Flatpack No-Lead Logic Packages*. These documents are available for download at www.ti.com.

### NOTE

All thermal models have an accuracy variation of ±20%.

Component population, layout of traces, layers, and air flow strongly influence heat dissipation. Worst-case load conditions should be tested in the real environment to ensure proper thermal conditions. Minimize thermal stress for proper long-term operation with a junction temperature well below +125°C.

The exposed lead-frame die pad on the bottom of the package must be connected to the V-pin.

# TEXAS INSTRUMENTS

### 10.4 Power Dissipation

Power dissipation depends on power supply, signal, and load conditions. It is dominated by the power dissipation of the output transistors of the OPA. For DC signals, power dissipation is equal to the product of output current,  $I_{OUT}$  and the output voltage across the conducting output transistor ( $V_S - V_{OUT}$ ).

It is very important to note that the temperature protection does not shut the device down in overtemperature conditions, unless the  $EF_{OT}$  pin is connected to the output enable pin  $\overline{OD}$ ; see the *Driver Output Disable* section.

The power that can be safely dissipated in the package is related to the ambient temperature and the heat sink design and conditions. The VQFN package with an exposed thermal pad is specifically designed to provide excellent power dissipation, but board layout greatly influences the heat dissipation.

To appropriately determine the required heat sink area, calculate required power dissipation; also consider the relationship between power dissipation and thermal resistance to minimize overheat conditions and allow for reliable long-term operation.

The heat-sinking efficiency can be tested using the  $EF_{OT}$  output signal. This output goes low at nominally 140°C junction temperature (assume 6% tolerance). With full power dissipation (for example, maximum current into a 0- load), the ambient temperature can be slowly raised until the OT flag goes low. This flag would indicate the minimum heat sinking for the usable operation condition.

The recommended landing pattern for the VQFN package is shown at the end of this data sheet.

# 11 器件和文档支持

# 11.1 文档支持

www.ti.com.cn

#### 11.1.1 相关文档

如需相关文档, 请参阅:

- 《PowerPAD™ 散热增强型封装》

- EIA/JEDEC 规范 JESD51-0 至 7、《VQFN/SON PCB 连接》

- 《四方扁平无引线逻辑器件封装》

# 11.2 接收文档更新通知

要接收文档更新通知,请导航至 Tl.com.cn 上的器件产品文件夹。请单击右上角的提醒我 进行注册,即可每周接收产品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。