LDC2112, LDC2114

ZHCSGN4B - DECEMBER 2016 - REVISED APRIL 2017

# 适合低功耗 HMI 按钮应用的 LDC2112/LDC2114 电感应触控解决 方案

### 1 特性

- 低功耗:

- 一个按钮: 6µA (速率为 0.625SPS 时)

- 两个按钮: 72µA (速率为 20SPS 时)

- 可配置按钮扫描频率:

- 0.625SPS 至 80SPS

- 触摸按钮的应力水平测量

- 独立通道运算:

- 适用于 LDC2112 的双通道

- 适用于 LDC2114 的四通道

- 集成算法,可支持:

- 调节每个按钮的力阈值

- 环境变化补偿

- 同步按钮按压检测

- 支持独立运算, 无需 MCU

- 强大的 EMI 性能:

- 支持 CISPR 22 和 CISPR 24 合规性

- 工作电压范围: 1.8V ± 5%

- 温度范围: -40°C 至 +85°C

- 接口:

- I<sup>2</sup>C

- 每个通道的专用逻辑输出

### 2 应用

以下产品的触控按钮及其所用不同材料(包括金属、塑料和玻璃材料)的应力水平测量:

- 消费类电子产品:

- 智能手机

- 智能手表及其他可穿戴设备

- 智能扬声器

- 平板电脑/PC

- 虚拟现实耳机

- 条形音箱

- 工业 应用:

- 电视

- 手持设备

- 家用电器

- HMI 面板和键盘

### 3 说明

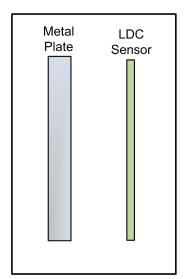

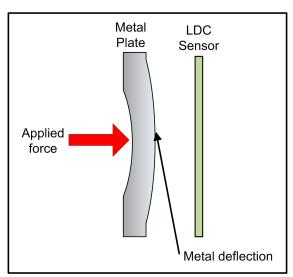

借助电感式传感技术,设计人员可以测量导电目标的小幅偏移,从而在金属、玻璃、塑料和木材等各种材料上实现人机界面 (HMI) 的触控按钮设计。电感应触控系统的传感器是一款可在小型 PCB 上实现的线圈,该PCB 位于面板后方,以免受外界环境影响。电感式传感解决方案不受湿度或油污和灰尘等非导电污染物的干扰。它能够自动更正导电目标出现的任何变形。

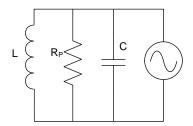

LDC2112/LDC2114 是一款多通道、低噪声电感数字转换器,采用集成算法,可实现电感应触控 应用。该器件采用创新型 LC 谐振器,可高度抑制噪音和干扰。即使材料偏移不足 200nm,LDC2112/LDC2114 也能够可靠地检测出来。

LDC2112/LDC2114 还提供了超低功耗模式,专供电池供电类应用中的开通/关断按钮 使用。

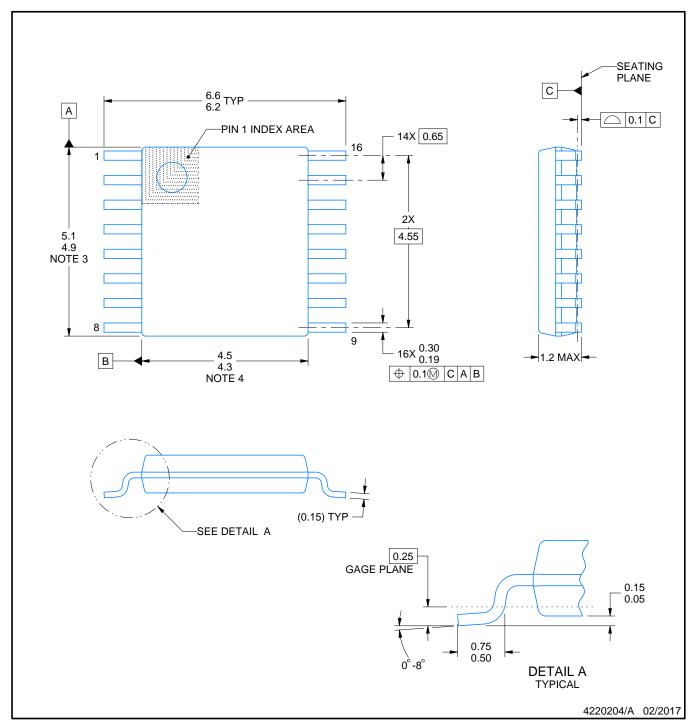

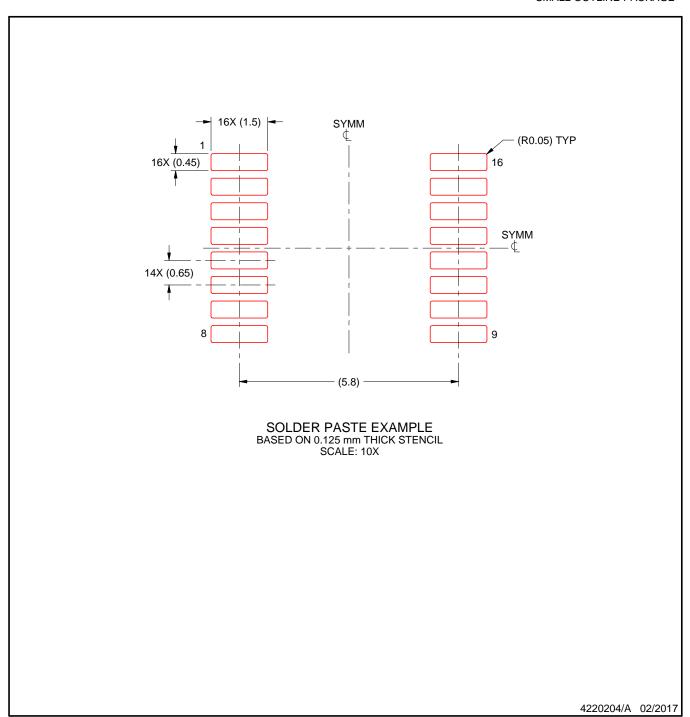

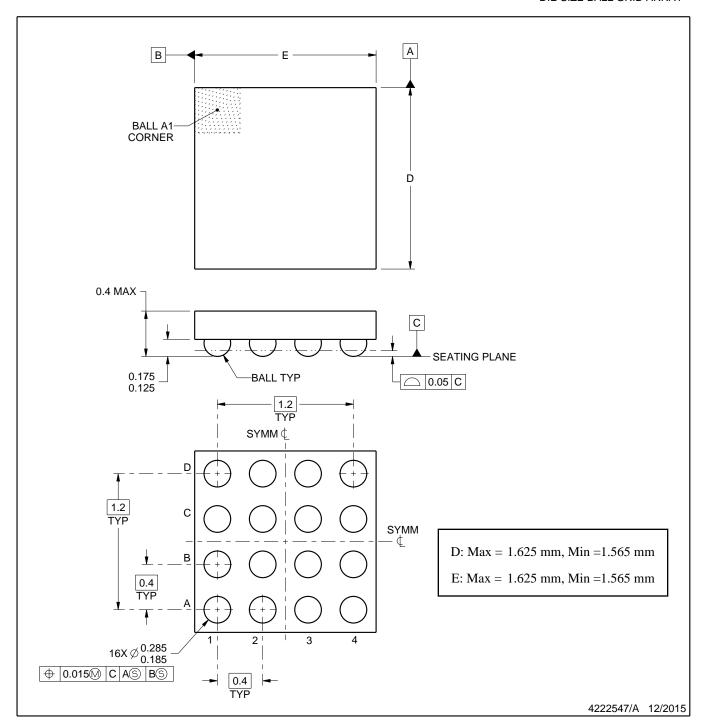

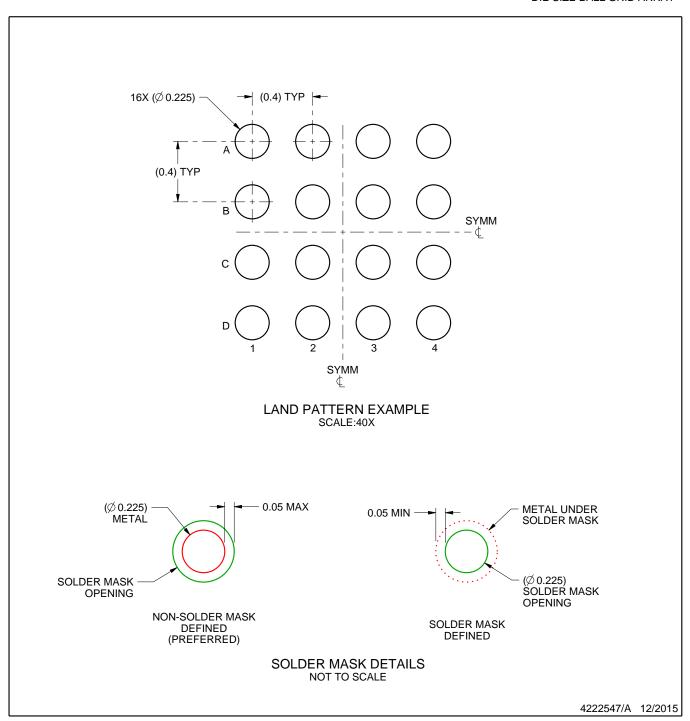

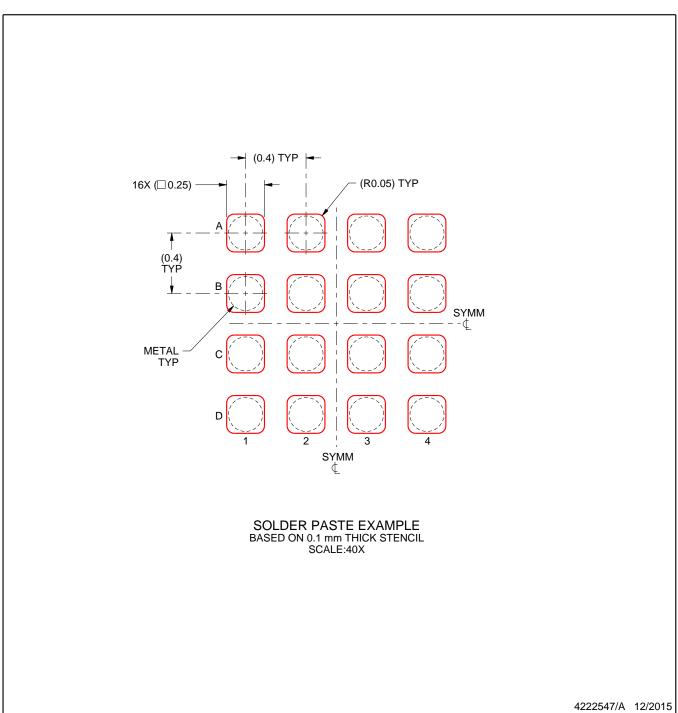

LDC2112/LDC2114 采用 16 引脚 DSBGA 或 TSSOP 封装。DSBGA 封装(间距为 0.4mm)的标称封装尺寸非常小,仅为 1.6 × 1.6mm,其最大高度为 0.4mm。TSSOP 封装(间距为 0.65mm)的标称封装尺寸为 5.0 × 4.4mm,其最大高度为 1.2mm。

#### 器件信息(1)

| 器件型号            | 封装         | 封装尺寸 (标称值)    |

|-----------------|------------|---------------|

| LDC2112/LDC2114 | DSBGA (16) | 1.6mm x 1.6mm |

| LDC2112/LDC2114 | TSSOP (16) | 5.0mm × 4.4mm |

(1) 如需了解所有可用封装,请参阅产品说明书末尾的可订购产品 附录。

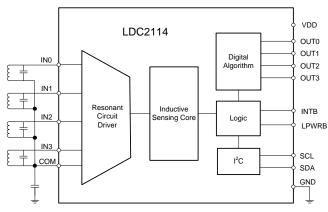

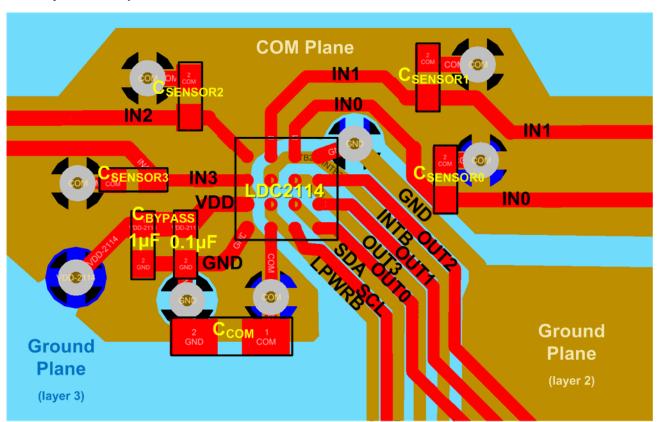

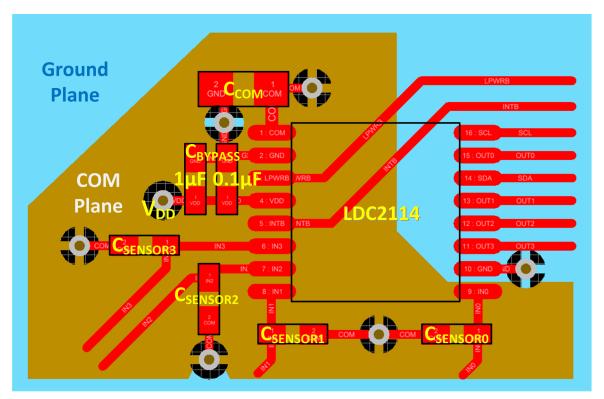

#### 简化原理图

Copyright © 2016, Texas Instruments Incorporated

|   |                                      | 目录 |    |                                |    |

|---|--------------------------------------|----|----|--------------------------------|----|

| 1 | 特性                                   | 1  |    | 7.5 Register Maps              | 15 |

| 2 | 应用                                   | 1  | 8  | Application and Implementation | 28 |

| 3 | 说明                                   | 1  |    | 8.1 Application Information    | 28 |

| 4 | 修订历史记录                               |    |    | 8.2 Typical Application        | 38 |

| 5 | Pin Configuration and Functions      |    | 9  | Power Supply Recommendations   | 40 |

| 6 | Specifications                       |    | 10 | Layout                         | 40 |

| • | 6.1 Absolute Maximum Ratings         |    |    | 10.1 Layout Guidelines         | 40 |

|   | 6.2 ESD Ratings                      |    |    | 10.2 Layout Example            | 40 |

|   | 6.3 Recommended Operating Conditions |    |    | 10.3 DSBGA Light Sensitivity   | 41 |

|   | 6.4 Thermal Information              |    | 11 | 器件和文档支持                        | 42 |

|   | 6.5 Electrical Characteristics       |    |    | 11.1 文档支持                      | 42 |

|   | 6.6 Digital Interface                | 7  |    | 11.2 相关链接                      | 42 |

|   | 6.7 I <sup>2</sup> C Interface       |    |    | 11.3 接收文档更新通知                  | 42 |

|   | 6.8 Typical Characteristics          | 8  |    | 11.4 社区资源                      | 42 |

| 7 | Detailed Description 1               | 0  |    | 11.5 商标                        | 42 |

| - | 7.1 Overview                         |    |    | 11.6 静电放电警告                    | 42 |

|   | 7.2 Functional Block Diagram         |    |    | 11.7 出口管制提示                    | 42 |

|   | 7.3 Feature Description              |    |    | 11.8 Glossary                  | 42 |

|   | 7.4 Device Functional Modes          |    | 12 | 机械、封装和可订购信息                    | 42 |

# 4 修订历史记录

| Changes from Revision A (January 2017) to Revision B  | Page |

|-------------------------------------------------------|------|

| Changed unit of Data set-up time from µs to ns (typo) | 7    |

| • 已更改 Multi-Channel and Single-Channel Operation      | 11   |

| • 己添加 LDC2112 to Register EN – Address 0x0C Table     | 19   |

| Changes from Original (December 2016) to Revision A   | Page |

| • 已更改 将"高级信息"更改成了"生产数据发布"                             | 1    |

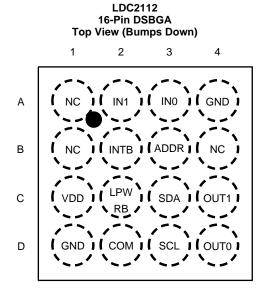

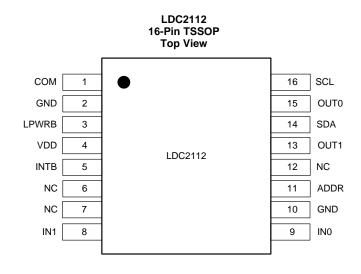

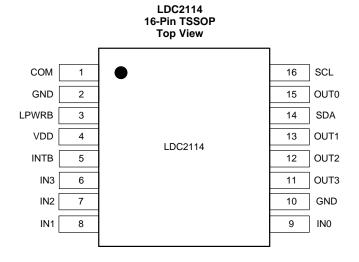

# 5 Pin Configuration and Functions

### Pin Functions - LDC2112

|       | PIN       |           | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                       |  |  |

|-------|-----------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | DSBGA NO. | TSSOP NO. | 1/0(")             | DESCRIPTION                                                                                                                                       |  |  |

| VDD   | C1        | 4         | Р                  | Power supply                                                                                                                                      |  |  |

| GND   | D1        | 2         | G                  | Ground <sup>(2)</sup>                                                                                                                             |  |  |

| GND   | A4        | 10        | G                  | Ground                                                                                                                                            |  |  |

| INTB  | B2        | 5         | 0                  | Interrupt output Polarity can be configured in Register 0x11.                                                                                     |  |  |

| LPWRB | C2        | 3         | 1                  | Normal / Low Power Mode select Set LPWRB to $V_{\rm DD}$ for Normal Power Mode or ground for Low Power Mode.                                      |  |  |

| СОМ   | D2        | 1         | А                  | Common return current path for all LC resonator sensors A capacitor should be connected from this pin to GND. Refer to Setting COM Pin Capacitor. |  |  |

| IN0   | А3        | 9         | Α                  | Channel 0 LC sensor input                                                                                                                         |  |  |

| IN1   | A2        | 8         | А                  | Channel 1 LC sensor input                                                                                                                         |  |  |

| OUT0  | D4        | 15        | 0                  | Channel 0 logic output Polarity can be configured in Register 0x1C.                                                                               |  |  |

| OUT1  | C4        | 13        | 0                  | Channel 1 logic output Polarity can be configured in Register 0x1C.                                                                               |  |  |

| ADDR  | В3        | 11        | I                  | $I^2C$ address When ADDR = Ground, $I^2C$ address = 0x2A. When ADDR = $V_{DD}$ , $I^2C$ address = 0x2B.                                           |  |  |

| SCL   | D3        | 16        | I                  | I <sup>2</sup> C clock                                                                                                                            |  |  |

| SDA   | C3        | 14        | I/O                | I <sup>2</sup> C data                                                                                                                             |  |  |

|       | A1        | 7         |                    |                                                                                                                                                   |  |  |

| NC    | B1        | 6         | _                  | No connect Leave them floating.                                                                                                                   |  |  |

|       | B4 12     |           |                    | Leave trieffi floating.                                                                                                                           |  |  |

- (1) I = Input, O = Output, P=Power, G=Ground, A=Analog

(2) Both pins should be connected to the system ground on the PCB.

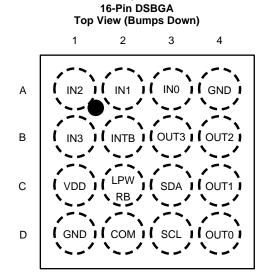

LDC2114

#### Pin Functions - LDC2114

| PIN   |           |           | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                       |  |  |

|-------|-----------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | DSBGA NO. | TSSOP NO. | 1/0(*)             | DESCRIPTION                                                                                                                                       |  |  |

| VDD   | C1        | 4         | Р                  | Power supply                                                                                                                                      |  |  |

| GND   | D1        | 2         | G                  | Ground <sup>(2)</sup>                                                                                                                             |  |  |

| GND   | A4        | 10        | 9                  | Glodila                                                                                                                                           |  |  |

| INTB  | B2        | 5         | 0                  | Interrupt output Polarity can be configured in Register 0x11.                                                                                     |  |  |

| LPWRB | C2        | 3         | I                  | Normal / Low Power Mode select<br>Set LPWRB to V <sub>DD</sub> for Normal Power Mode or ground for Low Power Mode.                                |  |  |

| СОМ   | D2        | 1         | А                  | Common return current path for all LC resonator sensors A capacitor should be connected from this pin to GND. Refer to Setting COM Pin Capacitor. |  |  |

| IN0   | А3        | 9         | Α                  | Channel 0 LC sensor input                                                                                                                         |  |  |

| IN1   | A2        | 8         | Α                  | Channel 1 LC sensor input                                                                                                                         |  |  |

| IN2   | A1        | 7         | Α                  | Channel 2 LC sensor input                                                                                                                         |  |  |

| IN3   | B1        | 6         | Α                  | Channel 3 LC sensor input                                                                                                                         |  |  |

| OUT0  | D4        | 15        | 0                  | Channel 0 logic output Polarity can be configured in Register 0x1C.                                                                               |  |  |

| OUT1  | C4        | 13        | 0                  | Channel 1 logic output Polarity can be configured in Register 0x1C.                                                                               |  |  |

| OUT2  | B4        | 12        | 0                  | Channel 2 logic output Polarity can be configured in Register 0x1C.                                                                               |  |  |

| OUT3  | В3        | 11        | 0                  | Channel 3 logic output Polarity can be configured in Register 0x1C.                                                                               |  |  |

| SCL   | D3        | 16        | I                  | I <sup>2</sup> C clock                                                                                                                            |  |  |

| SDA   | C3        | 14        | I/O                | $I^2C$ data $I^2C$ address = 0x2A.                                                                                                                |  |  |

<sup>(1)</sup> I = Input, O = Output, P=Power, G=Ground, A=Analog

<sup>(2)</sup> Both pins should be connected to the system ground on the PCB.

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

Over operating temperature range unless otherwise noted. (1)

|                  |                          | MIN  | MAX                | UNIT |

|------------------|--------------------------|------|--------------------|------|

| $V_{DD}$         | Supply voltage           |      | 2.2                | V    |

| V                | Voltage on SCL, SDA      | -0.3 | 3.6                | V    |

| VI               | Voltage on any other pin | -0.3 | 2.2 <sup>(2)</sup> | V    |

| TJ               | Junction temperature     | -40  | 85                 | °C   |

| T <sub>STG</sub> | Storage temperature      | -65  | 125                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                            |                                                                                | VALUE | UNIT |

|--------------------|----------------------------|--------------------------------------------------------------------------------|-------|------|

|                    | Flacture et et in          | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating temperature range unless otherwise noted.

|          |                      | MIN  | NOM | MAX  | UNIT |

|----------|----------------------|------|-----|------|------|

| $V_{DD}$ | Supply voltage       | 1.71 |     | 1.89 | V    |

| $T_J$    | Junction temperature | -40  |     | 85   | °C   |

#### 6.4 Thermal Information

|                      |                                              | LDC2112 | 2/LDC2114 |      |

|----------------------|----------------------------------------------|---------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DSBGA   | TSSOP     | UNIT |

|                      |                                              | 16 PINS | 16 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 81.8    | 105.1     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.4     | 40.3      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 18.2    | 50.2      | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.3     | 3.6       | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 18      | 49.6      | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Maximum voltage across any two pins (not including SCL or SDA) is  $V_{DD}$  + 0.3 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.5 Electrical Characteristics

Over operating temperature range unless otherwise noted.  $V_{DD} = 1.8 \text{ V}$ ,  $T_{J} = 25 \text{ °C}$ .

|                          | PARAMETER                                                        | TEST CONDITIONS                                                                                 | MIN   | TYP   | MAX   | UNIT |

|--------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| POWER                    |                                                                  |                                                                                                 |       |       |       |      |

| $V_{DD}$                 | Supply voltage                                                   |                                                                                                 | 1.71  | 1.8   | 1.89  | V    |

| I <sub>DDNP</sub>        | Normal power mode supply current (4 channels) (1)(2)(3)          | 4 channels, 40 SPS per channel,<br>1 ms sampling window per channel,<br>LPWRB = V <sub>DD</sub> |       | 0.49  |       | mA   |

| I <sub>DDNP</sub>        | Normal power mode supply current (2 channels) <sup>(1)</sup> (2) | 2 channels, 40 SPS per channel,<br>1 ms sampling window per channel,<br>LPWRB = V <sub>DD</sub> |       | 0.26  |       | mA   |

| I <sub>DDLP</sub>        | Low power mode supply current <sup>(1)</sup> (2)                 | 1 channel, 1.25 SPS per channel,<br>1 ms sampling window per channel,<br>LPWRB = Ground         |       | 9     |       | μΑ   |

| I <sub>DDSB</sub>        | Standby supply current                                           | No button active (EN = 0x00)                                                                    |       | 5     | 7     | μΑ   |

| SENSOR                   |                                                                  |                                                                                                 |       |       |       |      |

| I <sub>SENSOR, MAX</sub> | Sensor maximum current drive                                     | Registers SENSOR $n$ _CONFIG: RP $n$ = 0 (4)                                                    |       | 2.5   |       | mA   |

| R <sub>P, MIN</sub>      | Sensor minimum parallel resonant impedance                       |                                                                                                 |       | 350   |       | Ω    |

| R <sub>P, MAX</sub>      | Sensor maximum parallel resonant impedance                       |                                                                                                 |       | 10    |       | kΩ   |

| f <sub>SENSOR</sub>      | Sensor resonant frequency                                        |                                                                                                 | 1     |       | 30    | MHz  |

| Q <sub>SENSOR, MIN</sub> | Sensor minimum quality factor                                    |                                                                                                 |       | 5     |       |      |

| Q <sub>SENSOR, MAX</sub> | Sensor maximum quality factor                                    |                                                                                                 |       | 30    |       |      |

| V <sub>SENSOR, PP</sub>  | Sensor oscillation peak-to-peak voltage                          | Measured on the $INn^{(4)}$ pins with reference to COM.                                         |       | 0.9   |       | V    |

| C <sub>IN</sub>          | Sensor input pin capacitance                                     |                                                                                                 |       | 17    |       | pF   |

| CONVERTER                |                                                                  |                                                                                                 |       |       |       |      |

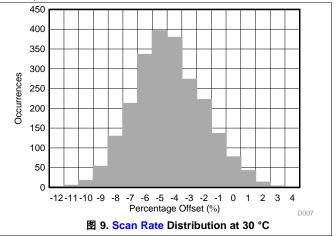

| SR <sub>NP, MIN</sub>    | Minimum normal power mode scan rate (5)                          | LPWRB = V <sub>DD</sub>                                                                         | 7     | 10    | 13    | SPS  |

| SR <sub>NP, MAX</sub>    | Maximum normal power mode scan rate <sup>(5)</sup>               | LPWRB = V <sub>DD</sub>                                                                         | 56    | 80    | 104   | SPS  |

| SR <sub>LP, MIN</sub>    | Minimum low power mode scan rate <sup>(5)</sup>                  | LPWRB = Ground                                                                                  | 0.438 | 0.625 | 0.813 | SPS  |

| SR <sub>LP, MAX</sub>    | Maximum low power mode scan rate <sup>(5)</sup>                  | LPWRB = Ground                                                                                  | 3.5   | 5     | 6.5   | SPS  |

| Resolution               | Data code width                                                  |                                                                                                 |       | 12    |       | Bits |

Sensor configuration:  $L_{SENSOR}=0.85~\mu\text{H}$ ,  $C_{SENSOR}=58~\text{pF}$ ,  $Q_{SENSOR}=11$ ,  $R_P=0.7~\text{k}\Omega$ .  $I^2\text{C}$  communication and pull-up resistors current is not included. Four-channel supply current is applicable to LDC2114 only. The italic n is the channel index, i.e., n=0 or 1 for LDC2112; n=0, 1, 2, or 3 for LDC2114. For typical distribution of the scan rates, refer to  $\boxed{8}$  9.

### 6.6 Digital Interface

Over operating temperature range unless otherwise noted.  $V_{DD}$  = 1.8 V,  $T_J$  = 25 °C. Pins: LPWRB, INTB, OUT0, OUT1, OUT2, OUT3, and ADDR.

|                 | PARAMETER                     | TEST CONDITIONS              | MIN                 | TYP MAX             | UNIT |

|-----------------|-------------------------------|------------------------------|---------------------|---------------------|------|

| VOLTAG          | E LEVELS                      |                              |                     |                     |      |

| $V_{IH}$        | Input high voltage            |                              | $0.8 \times V_{DD}$ |                     | V    |

| $V_{IL}$        | Input low voltage             |                              |                     | $0.2 \times V_{DD}$ | V    |

| V <sub>OH</sub> | Output high voltage           | I <sub>SOURCE</sub> = 400 μA | $0.8 \times V_{DD}$ |                     | V    |

| V <sub>OL</sub> | Output low voltage            | $I_{SINK} = 400 \mu A$       |                     | $0.2 \times V_{DD}$ | V    |

| IL              | Digital input leakage current |                              | -500                | 500                 | nA   |

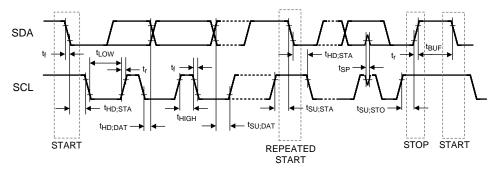

### 6.7 I<sup>2</sup>C Interface

|                         |                                                                                  |                                                        | MIN                    | TYP MAX               | UNIT |

|-------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|-----------------------|------|

| VOLTAGE                 | LEVELS                                                                           |                                                        |                        |                       |      |

| V <sub>IH</sub>         | Input high voltage                                                               |                                                        | $0.7 \times V_{DD}$    |                       | V    |

| V <sub>IL</sub>         | Input low voltage                                                                |                                                        |                        | 0.3 × V <sub>DD</sub> | V    |

| V <sub>OL</sub>         | Output low voltage                                                               | 3 mA sink current                                      |                        | $0.2 \times V_{DD}$   | V    |

| HYS                     | Hysteresis <sup>(1)</sup>                                                        |                                                        | 0.05 × V <sub>DD</sub> |                       | V    |

| I <sup>2</sup> C TIMINO | G CHARACTERISTICS                                                                |                                                        |                        | <u>.</u>              |      |

| f <sub>SCL</sub>        | Clock frequency                                                                  |                                                        |                        | 400                   | kHz  |

| t <sub>LOW</sub>        | Clock low time                                                                   |                                                        | 1.3                    |                       | μs   |

| t <sub>HIGH</sub>       | Clock high time                                                                  |                                                        | 0.6                    |                       | μs   |

| t <sub>HD;STA</sub>     | Hold time repeated START condition                                               | After this period, the first clock pulse is generated. | 0.6                    |                       | μs   |

| t <sub>SU;STA</sub>     | Set-up time for a repeated START condition                                       |                                                        | 0.6                    |                       | μs   |

| t <sub>HD;DAT</sub>     | Data hold time                                                                   |                                                        | 0                      |                       | μs   |

| t <sub>SU;DAT</sub>     | Data set-up time                                                                 |                                                        | 100                    |                       | ns   |

| t <sub>SU;STO</sub>     | Set-up time for STOP condition                                                   |                                                        | 0.6                    |                       | μs   |

| t <sub>BUF</sub>        | Bus free time between a STOP and START condition                                 |                                                        | 1.3                    |                       | μs   |

| t <sub>VD;DAT</sub>     | Data valid time                                                                  |                                                        |                        | 0.9                   | μs   |

| t <sub>VD;ACK</sub>     | Data valid acknowledge time                                                      |                                                        |                        | 0.9                   | μs   |

| t <sub>SP</sub>         | Pulse width of spikes that must be suppressed by the input filter <sup>(1)</sup> |                                                        |                        | 50                    | ns   |

(1) This parameter is specified by design and/or characterization and is not tested in production.

图 1. I<sup>2</sup>C Timing Diagram

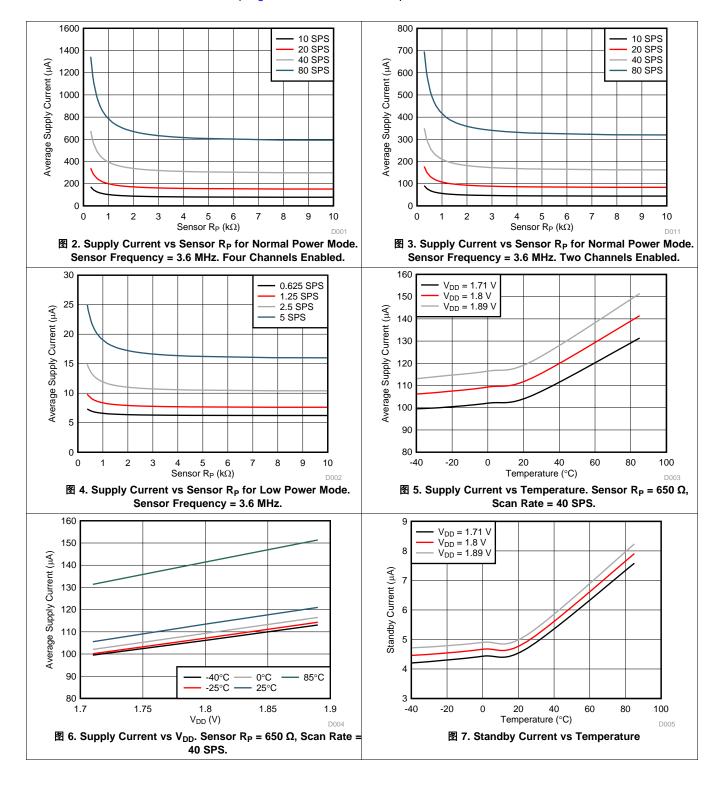

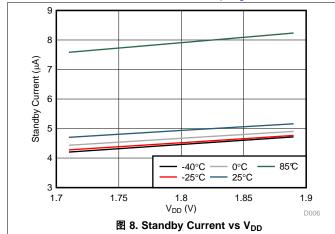

### 6.8 Typical Characteristics

Over recommended operating conditions unless specified otherwise.  $V_{DD}$  = 1.8 V,  $T_{J}$  = 25 °C.

One channel enabled with a button sampling window of 1 ms unless specified otherwise.

# Typical Characteristics (接下页)

One channel enabled with a button sampling window of 1 ms unless specified otherwise.

### 7 Detailed Description

#### 7.1 Overview

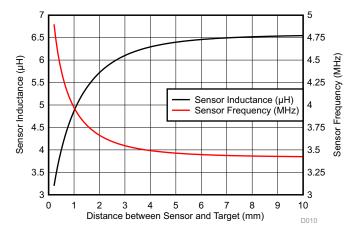

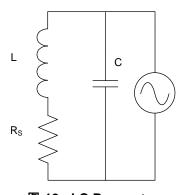

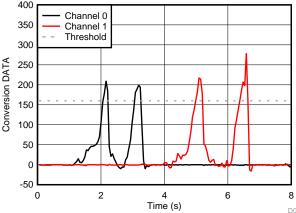

The LDC2112/LDC2114 is a multi-channel, low-noise, high-resolution inductance to digital converter (LDC) optimized for inductive touch applications. Button presses form micro-deflections in the conductive targets which cause frequency shifts in the resonant sensors. The LDC2112/LDC2114 can measure such frequency shifts and determine when button presses have occurred. With adjustable sensitivity per input channel, the LDC2112/LDC2114 can reliably operate with a wide range of physical button structures and materials. The high resolution measurement enables the implementation of force level buttons. The LDC2112/LDC2114 incorporates customizable post-processing algorithms for enhanced robustness.

The LDC2112/LDC2114 can operate in an ultra-low power mode for optimal battery life, or can be toggled into a higher scan rate for more responsive button press detection for game play or other low latency applications. The LDC2112/LDC2114 is operational from -40 °C to +85 °C with a 1.8 V  $\pm$  5% power supply voltage.

The LDC2112/LDC2114 is configured through 400 kHz I<sup>2</sup>C. Button presses can be reported through the I<sup>2</sup>C interface or with configurable polarity dedicated push-pull outputs. Besides the LC resonant sensors, the only external components necessary for operation are supply bypassing capacitors and a COM pin capacitor to ground.

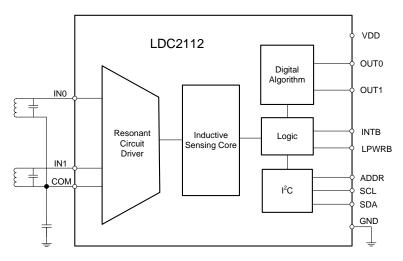

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

图 10. Block Diagram of LDC2112

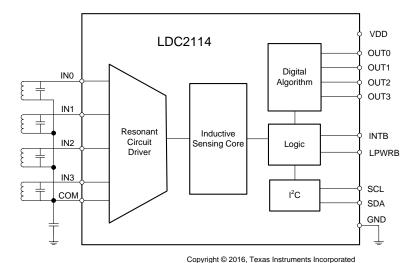

# Functional Block Diagram (接下页)

图 11. Block Diagram of LDC2114

### 7.3 Feature Description

### 7.3.1 Multi-Channel and Single-Channel Operation

The LDC2112 provides two independent sensing channels; the LDC2114 provides four independent sensing channels. In the following sections, some parameters, such as DATAn and SENSORn\_CONFIG, contain a channel index n. In those instances, n = 0 or 1 for LDC2112, and n = 0, 1, 2, or 3 for LDC2114.

The LDC2112's two available channels are always enabled in Normal Power Mode. The LDC2112 sequentially samples both channels at the configured scan rate. Either channel can be independently enabled in Low Power Mode by setting the LPENn (n = 0 or 1) bit fields in Register EN (Address 0x0C).

Any of the LDC2114's four available channels can be independently enabled by setting the ENn and LPENn (n = 0, 1, 2, or 3) bit fields in *Register EN (Address 0x0C)*. The low-power-enable bit LPENn only takes effect if the corresponding ENn bit is also set. If only one channel is set active, the LDC2114 periodically samples the single active channel at the configured scan rate. When several channels are set active, the LDC2114 operates in multi-channel mode, and it sequentially samples the active channels at the configured scan rate. Each channel of the LDC2114 can be independently enabled in Low Power Mode and Normal Power Mode.

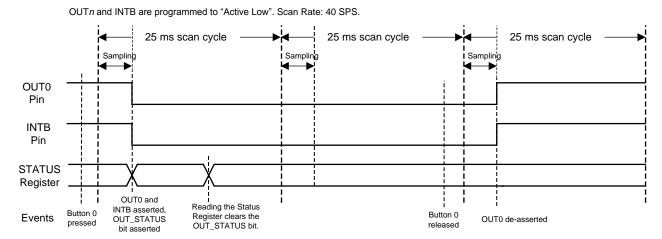

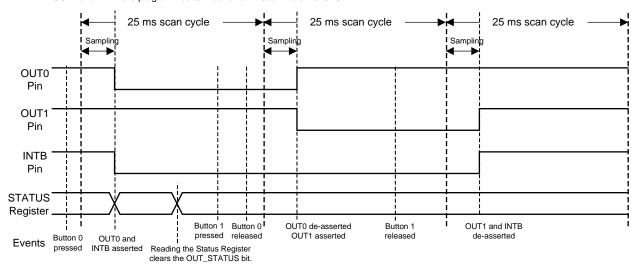

### 7.3.2 Button Output Interfaces

Button events may be reported by using two methods. The first method is to monitor the OUTn pins (n = 0, 1, 2, or 3), which are push-pull outputs and can be used as interrupts to a micro-controller. The polarities of these pins are programmable through  $Register\ OPOL\_DPOL\ (Address\ Ox1C)$ . Any button press or error condition is also reported by the push-pull interrupt pin, INTB. Its polarity is configurable through  $Register\ INTPOL\ (Address\ Ox11)$ . Any assertion of INTB is cleared upon reading  $Register\ STATUS\ (Address\ Ox00)$ . Each push-pull output must be assigned to a dedicated general-purpose input pin on the micro-controller to avoid potential current fights.

The second method is by use of the LDC2112/LDC2114's  $I^2C$  interface. The *Register OUT (Address 0x01)* contains the fields OUT0, OUT1, OUT2, and OUT3, which indicate when a button press has been detected. For more advanced button press measurements, the output DATAn registers (n = 0, 1, 2, or 3, Addresses 0x02 through 0x09), which are 12-bit two's complements, can be retrieved for all active buttons, and processed on a micro-controller. A valid button push is represented by a positive value. The polarity is configurable in *Register OPOL\_DPOL (Address 0x1C)*. The DATAn values can be used to implement multi-level buttons, where the data value is correlated to the amount of force applied to the button.

#### 7.3.3 Programmable Button Sensitivity

The GAIN*n* registers (Addresses *0x0E*, *0x10*, *0x12*, and *0x14*) enable sensitivity enhancement of individual buttons to ensure consistent behavior of different mechanical structures. The sensitivity has a 64-level gain factor for a normalized gain between 1 and 232. Each gain step increases the gain by an average of 9%.

The gain required for an application is primarily determined by the mechanical rigidity of each individual button. The individual gain steps are listed in the *Gain Table*.

### 7.3.4 Baseline Tracking

The LDC2112/LDC2114 incorporates a baseline tracking algorithm to automatically compensate for any slow change in the sensor output caused by environmental variations, such as temperature drift. The baseline tracking is configured independently for Normal Power Mode and Low Power Mode. For more information, refer to *Tracking Baseline*.

#### 7.3.5 Integrated Button Algorithms

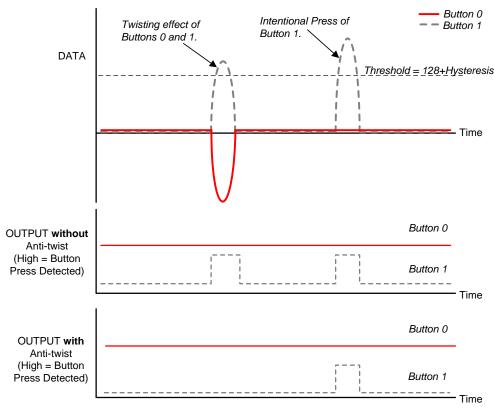

The LDC2112/LDC2114 features several algorithms that can mitigate false button detections due to mechanical non-idealities. The algorithms look for correlated button responses, for example, similar or opposite responses between two neighboring buttons, to determine if there is any undesirable mechanical crosstalk. For more information, refer to *Mitigating False Button Detections*.

#### 7.3.6 I<sup>2</sup>C Interface

The LDC2112/LDC2114 features an  $I^2C$  Interface that can be used to program the internal registers and read channel data. Before reading the OUT (Address 0x01) or channel DATAn (n = 0, 1, 2 or 3, Addresses 0x02 through 0x05) registers, the user should always read *Register STATUS* (*Address 0x00*) first to lock the data. The LDC2112/LDC2114 supports burst mode with auto-incrementing register addresses.

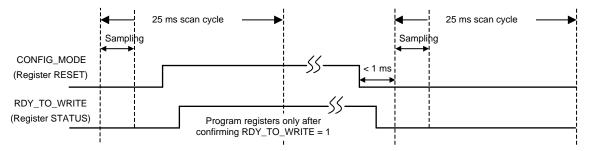

For the write sequence, there is a special handshake process that has to take place to ensure data integrity. The sequence of register write is illustrated as follows:

- Set CONFIG\_MODE (Register RESET, Address 0x0A) bit = 1 to start the register write session

- Poll for RDY\_TO\_WRITE (Register STATUS, Address 0x00) bit = 1

- I<sup>2</sup>C write to configure registers

- Set CONFIG\_MODE (Register RESET, Address 0x0A) bit = 0 to terminate the register write session

After CONFIG\_MODE is de-asserted, the new scan cycle will start in less than 1 ms. The waveform of the above process is shown in 🗵 12.

图 12. Timing Diagram Representing the States of the CONFIG\_MODE and RDY\_TO\_WRITE Bits for an I<sup>2</sup>C Write Handshake

#### 7.3.6.1 Selectable PC Address (LDC2112 Only)

The LDC2112 provides an  $I^2C$  address select pin, ADDR. Connecting this pin to ground will set the LDC2112  $I^2C$  address to 0x2A. Connecting ADDR to  $V_{DD}$  will set the LDC2112  $I^2C$  address to 0x2B.

The LDC2114 has a fixed I<sup>2</sup>C address of 0x2A.

### 7.3.6.2 PC Interface Specifications

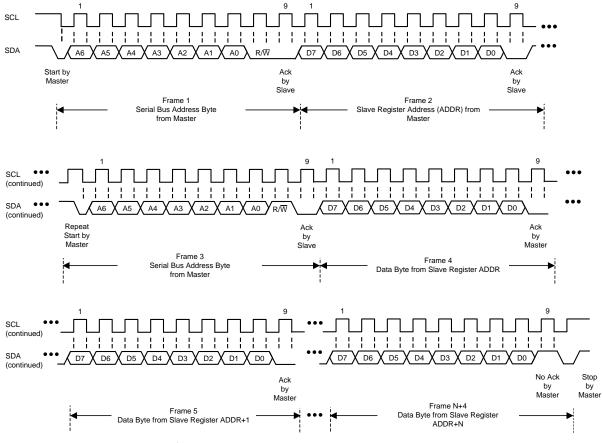

The maximum speed of the I<sup>2</sup>C interface is 400 kHz. This sequence uses the standard I<sup>2</sup>C 7-bit slave address followed by an 8-bit pointer to set the register address. For both write and read, the address pointer will autoincrement as long as the master acknowledges.

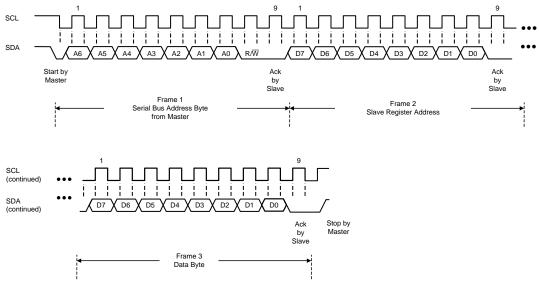

图 13. I<sup>2</sup>C Sequence of Writing a Single Register

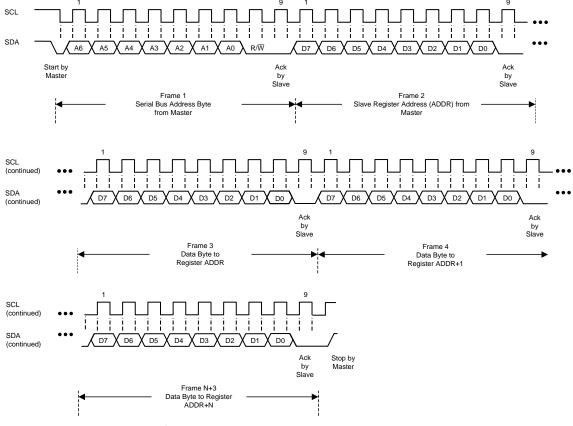

图 14. I<sup>2</sup>C Sequence of Writing Consecutive Registers

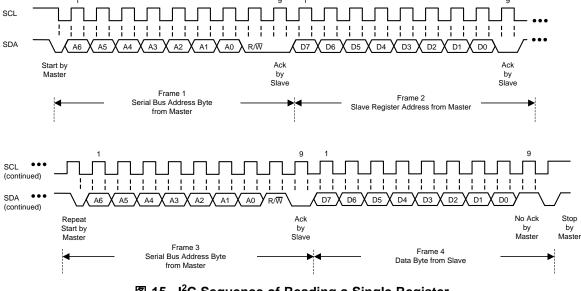

图 15. I<sup>2</sup>C Sequence of Reading a Single Register

图 16. I<sup>2</sup>C Sequence of Reading Consecutive Registers

#### 7.3.6.3 PC Bus Control

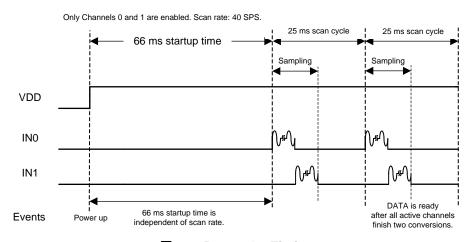

The LDC2112/LDC2114 cannot drive the I<sup>2</sup>C clock (SCL), i.e. it does not support clock stretching. In the unlikely event where the SCL is stuck LOW, power cycle any device that is holding the SCL to activate its internal Power-On Reset (POR) circuit. If the LDC is connected to the same power supply as that device, there will be about 66 ms set-up time before the LDC becomes active again. For more information, refer to *Defining Power-On Timing*. If the data line (SDA) is stuck LOW, the I<sup>2</sup>C master should send nine clock pulses. The device that is holding the bus LOW should release it sometime within those nine clocks. If not, then power cycle to clear the bus.

The LDC2112/LDC2114 has built-in monitors to check that the device is currently working. In the unlikely event of a device fault, the device state will be reset internally, and all the registers will be reset with default settings. For system robustness, it is recommended to check the value of a modified register periodically to monitor the device status and reload the register settings if needed.

#### 7.4 Device Functional Modes

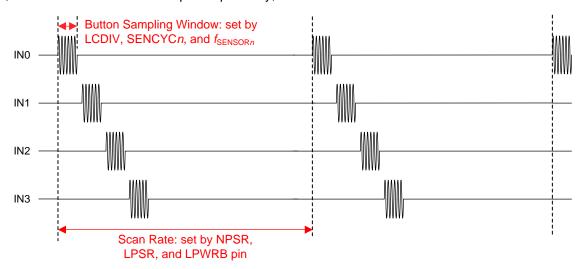

The LDC2112/LDC2114 supports two power modes of operation, a Normal Power Mode for active sampling at 10, 20, 40, or 80 SPS, and a Low Power Mode for reduced current consumption at 0.625, 1.25, 2.5, or 5 SPS. Refer to *Configuring Button Scan Rate* for details.

#### 7.4.1 Normal Power Mode

When the LPWRB input pin is set to  $V_{DD}$ , all enabled channels operate in Normal Power Mode. Each channel can be enabled independently through *Register EN (Address 0x0C)*. For the electrical specification of Normal Power Mode Scan Rate, refer to *Electrical Characteristics*.

#### 7.4.2 Low Power Mode

When the LPWRB input pin is set to Ground, only the low-power-enabled channels are active. Each channel can be enabled independently to operate in Low Power Mode through *Register EN (Address 0x0C)*. For a channel to operate in the Low Power Mode, both the LPEN*n* and EN*n* bits (*n* is the channel index) must be set to 1. The Low Power Mode allows for energy-saving monitoring of button activity. In this mode, the device is in an inactive power-saving state for the majority of the time. Lower scan rates correspond to lower current consumption. In addition, the individual button sampling window should be set to the lowest effective setting (this is system dependent, but typically 0.8 to 1 ms). For the electrical specification of the configurable Low Power Mode Scan Rate, refer to *Electrical Characteristics*.

If a channel is operational in both Low Power Mode and Normal Power Mode, it is recommended to toggle the LPWRB pin only after the button associated with that channel is released.

#### 7.4.3 Configuration Mode

Before configuring any register settings, the device must be put into the configuration mode first. Setting CONFIG\_MODE = 1 through *Register RESET (Address 0x0A)* stops data conversion and holds the device in configuration mode. Any device configuration changes can then be made. The current consumption in this mode is typically 0.3 mA. After all changes have been written, set CONFIG\_MODE = 0 for normal operation. Refer to *PC Interface* for more information.

#### 7.5 Register Maps

Registers indicated with Reserved must be written only with indicated values. Improper device operation may occur otherwise.

| 表 1 | 1. F | legi | iste | r Li | st |

|-----|------|------|------|------|----|

|-----|------|------|------|------|----|

| ADDRESS | NAME      | DEFAULT VALUE | DESCRIPTION                                              |

|---------|-----------|---------------|----------------------------------------------------------|

| 0x00    | STATUS    | 0x00          | Device status                                            |

| 0x01    | OUT       | 0x00          | Channel output logic states                              |

| 0x02    | DATA0_LSB | 0x00          | The lower 8 bits of the Button 0 data (Two's complement) |

| 0x03    | DATA0_MSB | 0x00          | The upper 4 bits of the Button 0 data (Two's complement) |

| 0x04    | DATA1_LSB | 0x00          | The lower 8 bits of the Button 1 data (Two's complement) |

# Register Maps (接下页)

# 表 1. Register List (接下页)

|         |                     | 1X I. INEGISIEI LIS              | ·· (IX   X)                                              |

|---------|---------------------|----------------------------------|----------------------------------------------------------|

| ADDRESS | NAME                | DEFAULT VALUE                    | DESCRIPTION                                              |

| 0x05    | DATA1_MSB           | 0x00                             | The upper 4 bits of the Button 1 data (Two's complement) |

| 0x06    | DATA2_LSB           | 0x00                             | The lower 8 bits of the Button 2 data (Two's complement) |

| 0x07    | DATA2_MSB           | 0x00                             | The upper 4 bits of the Button 2 data (Two's complement) |

| 80x0    | DATA3_LSB           | 0x00                             | The lower 8 bits of the Button 3 data (Two's complement) |

| 0x09    | DATA3_MSB           | 0x00                             | The upper 4 bits of the Button 3 data (Two's complement) |

| 0x0A    | RESET               | 0x00                             | Reset device and register configurations                 |

| 0x0B    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x0C    | EN                  | 0x10 (LDC2112)<br>0x1F (LDC2114) | Enable channels and low power modes                      |

| 0x0D    | NP_SCAN_RATE        | 0x01                             | Normal Power Mode scan rate                              |

| 0x0E    | GAIN0               | 0x28                             | Gain for Channel 0 sensitivity adjustment                |

| 0x0F    | LP_SCAN_RATE        | 0x02                             | Low Power Mode scan rate                                 |

| 0x10    | GAIN1               | 0x28                             | Gain for Channel 1 sensitivity adjustment                |

| 0x11    | INTPOL              | 0x01                             | Interrupt polarity                                       |

| 0x12    | GAIN2               | 0x28                             | Gain for Channel 2 sensitivity adjustment                |

| 0x13    | LP_BASE_INC         | 0x05                             | Low power base increment                                 |

| 0x14    | GAIN3               | 0x28                             | Gain for Channel 3 sensitivity adjustment                |

| 0x15    | NP_BASE_INC         | 0x03                             | Normal power base increment                              |

| 0x16    | BTPAUSE_MAXWIN      | 0x00                             | Baseline tracking pause and Max-win                      |

| 0x17    | LC_DIVIDER          | 0x03                             | LC oscillation frequency divider                         |

| 0x18    | HYST                | 0x08                             | Hysteresis for threshold                                 |

| 0x19    | TWIST               | 0x00                             | Anti-twist                                               |

| 0x1A    | COMMON_DEFORM       | 0x00                             | Anti-common and anti-deformation                         |

| 0x1B    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x1C    | OPOL_DPOL           | 0x0F                             | Output polarity                                          |

| 0x1D    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x1E    | CNTSC               | 0x55                             | Counter scale                                            |

| 0x1F    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x20    | SENSOR0_CONFIG      | 0x04                             | Sensor 0 cycle count, frequency, R <sub>P</sub> range    |

| 0x21    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x22    | SENSOR1_CONFIG      | 0x04                             | Sensor 1 cycle count, frequency, R <sub>P</sub> range    |

| 0x23    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x24    | SENSOR2_CONFIG      | 0x04                             | Sensor 2 cycle count, frequency, R <sub>P</sub> range    |

| 0x25    | FTF0                | 0x02                             | Sensor 0 fast tracking factor                            |

| 0x26    | SENSOR3_CONFIG      | 0x04                             | Sensor 3 cycle count, frequency, R <sub>P</sub> range    |

| 0x27    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x28    | FTF1_2              | 0x50                             | Sensors 1 and 2 fast tracking factors                    |

| 0x29    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x2A    | RESERVED            | 0x00                             | Reserved. Set to 0x00                                    |

| 0x2B    | FTF3                | 0x01                             | Sensor 3 fast tracking factor                            |

| 0xFC    | MANUFACTURER_ID_LSB | 0x49                             | Manufacturer ID lower byte                               |

| 0xFD    | MANUFACTURER_ID_MSB | 0x54                             | Manufacturer ID upper byte                               |

| 0xFE    | DEVICE_ID_LSB       | 0x01 (LDC2112)<br>0x00 (LDC2114) | Device ID lower byte                                     |

| 0xFF    | DEVICE_ID_MSB       | 0x20                             | Device ID upper byte                                     |

|         |                     |                                  |                                                          |

#### 7.5.1 Individual Register Listings

Fields indicated with 'Reserved' must be written only with indicated values. Improper device operation may occur otherwise. The R/W column indicates the Read-Write status of the corresponding field. An 'R/W' entry indicates read and write capability, an 'R' indicates read-only, and a 'W' indicates write-only.

Before reading the OUT (Address 0x01) or channel DATAn registers (n = 0, 1, 2, or 3, Addresses 0x02 through 0x09), the user should always read the STATUS register (Address 0x00) first to lock the data. The LDC2112/LDC2114 supports burst mode with auto-incrementing register addresses.

### 表 2. Register STATUS - Address 0x00

| BIT | FIELD         | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                            |

|-----|---------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OUT_STATUS    | R    | 0     | Output Status Logic OR of output bits from Register OUT (Address 0x01). This field is cleared by reading this register.                                                                                                |

| 6   | CHIP_READY    | R    | 1     | Chip Ready Status b0: Chip not ready after internal reset. b1: Chip ready after internal reset.                                                                                                                        |

| 5   | RDY_TO_WRITE  | R    | 0     | Ready to Write Indicates if registers are ready to be written. See <sup>PC</sup> Interface for more information. b0: Registers not ready. b1: Registers ready.                                                         |

| 4   | MAXOUT        | R    | 0     | Maximum Output Code Indicates if any channel output data reaches the maximum value (+0x7FF or -0x800). Cleared by a read of the status register. b0: No maximum output code. b1: Maximum output code.                  |

| 3   | FSM_WD        | R    | 0     | Finite-State Machine Watchdog Error Reports an error has occurred and conversions have been halted. Cleared by a read of the status register. b0: No error in finite-state machine. b1: Error in finite-state machine. |

| 2   | LC_WD         | R    | 0     | LC Sensor Watchdog Error Reports an error when any LC oscillator fails to start. Cleared by a read of the status register. b0: No error in LC oscillator initialization. b1: Error in LC oscillator initialization.    |

| 1   | TIMEOUT       | R    | 0     | Button Timeout Reports when any button is asserted for more than 50 seconds. Cleared by a read of the status register. b0: no timeout error. b1: timeout error.                                                        |

| 0   | REGISTER_FLAG | R    | 0     | Register Integrity Flag Reports if any register's value has an unexpected change. Cleared by a read of the status register. b0: No unexpected register change. b1: Unexpected register change.                         |

### 表 3. Register OUT - Address 0x01

| BIT | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                              |

|-----|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | RESERVED | R    | 0000  | Reserved. Set to b0000.                                                                                                                  |

| 3   | OUT3     | R    | 0     | Output Logic State for Channel 3 (LDC2114 Only)<br>b0: No button press detected on Channel 3.<br>b1: Button press detected on Channel 3. |

| 2   | OUT2     | R    | 0     | Output Logic State for Channel 2 (LDC2114 Only)<br>b0: No button press detected on Channel 2.<br>b1: Button press detected on Channel 2. |

| 1   | OUT1     | R    | 0     | Output Logic State for Channel 1 b0: No button press detected on Channel 1. b1: Button press detected on Channel 1.                      |

| 0   | OUT0     | R    | 0     | Output Logic State for Channel 0 b0: No button press detected on Channel 0. b1: Button press detected on Channel 0.                      |

### 表 4. Register DATA0\_LSB - Address 0x02

| BIT | FIELD      | TYPE | RESET     | DESCRIPTION                                            |

|-----|------------|------|-----------|--------------------------------------------------------|

| 7:0 | DATA0[7:0] | R    | 0000 0000 | The lower 8 bits of Channel 0 data (Two's complement). |

# 表 5. Register DATA0\_MSB - Address 0x03

| BIT | FIELD       | TYPE | RESET | DESCRIPTION                                            |

|-----|-------------|------|-------|--------------------------------------------------------|

| 7:4 | RESERVED    | R    | 0000  | Reserved.                                              |

| 3:0 | DATA0[11:8] | R    | 0000  | The upper 4 bits of Channel 0 data (Two's complement). |

# 表 6. Register DATA1\_LSB - Address 0x04

| BIT | FIELD      | TYPE | RESET     | DESCRIPTION                                            |

|-----|------------|------|-----------|--------------------------------------------------------|

| 7:0 | DATA1[7:0] | R    | 0000 0000 | The lower 8 bits of Channel 1 data (Two's complement). |

### 表 7. Register DATA1\_MSB - Address 0x05

|   | BIT | FIELD       | TYPE | RESET | DESCRIPTION                                            |

|---|-----|-------------|------|-------|--------------------------------------------------------|

|   | 7:4 | RESERVED    | R    | 0000  | Reserved.                                              |

| Ī | 3:0 | DATA1[11:8] | R    | 0000  | The upper 4 bits of Channel 1 data (Two's complement). |

### 表 8. Register DATA2\_LSB - Address 0x06

| BIT | FIELD      | TYPE | RESET     | DESCRIPTION                                                           |

|-----|------------|------|-----------|-----------------------------------------------------------------------|

| 7:0 | DATA2[7:0] | R    | 0000 0000 | The lower 8 bits of Channel 2 data (Two's complement). (LDC2114 Only) |

### 表 9. Register DATA2\_MSB - Address 0x07

| BIT | FIELD       | TYPE | RESET | DESCRIPTION                                                           |

|-----|-------------|------|-------|-----------------------------------------------------------------------|

| 7:4 | RESERVED    | R    | 0000  | Reserved.                                                             |

| 3:0 | DATA2[11:8] | R    | 0000  | The upper 4 bits of Channel 2 data (Two's complement). (LDC2114 Only) |

### 表 10. Register DATA3\_LSB - Address 0x08

| BIT | FIELD      | TYPE | RESET     | DESCRIPTION                                                           |

|-----|------------|------|-----------|-----------------------------------------------------------------------|

| 7:0 | DATA3[7:0] | R    | 0000 0000 | The lower 8 bits of Channel 3 data (Two's complement). (LDC2114 Only) |

### 表 11. Register DATA3\_MSB - Address 0x09

| BIT | FIELD       | TYPE | RESET | DESCRIPTION                                                           |

|-----|-------------|------|-------|-----------------------------------------------------------------------|

| 7:4 | RESERVED    | R    | 0000  | Reserved.                                                             |

| 3:0 | DATA3[11:8] | R    | 0000  | The upper 4 bits of Channel 3 data (Two's complement). (LDC2114 Only) |

## 表 12. Register RESET - Address 0x0A

| BIT | FIELD       | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                 |

|-----|-------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | RESERVED    | R/W  | 000   | Reserved. Set to b000.                                                                                                                                                                                                                                                                                                      |

| 4   | FULL_RESET  | R/W  | 0     | Device Reset b0: Normal operation. b1: Resets the device and register configurations. All registers will be returned to default values. Normal operation will not resume until STATUS:CHIP_READY = 1.                                                                                                                       |

| 3:1 | RESERVED    | R/W  | 000   | Reserved. Set to b000.                                                                                                                                                                                                                                                                                                      |

| 0   | CONFIG_MODE | R/W  | 0     | Configuration Mode b0: Normal operation. b1: Holds the device in configuration mode (no data conversion), but maintains current register configurations. Any device configuration changes should be made with this bit set to 1. After all configuration changes have been written, set this bit to 0 for normal operation. |

# 表 13. Register EN – Address 0x0C

| BIT | FIELD              | TYPE | RESET | DESCRIPTION                                                                                                                                           |

|-----|--------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LPEN3              | R/W  | 0     | Channel 3 Low-Power-Enable (LDC2114 Only) b0: Disable Channel 3 in Low Power Mode. b1: Enable Channel 3 in Low Power Mode. EN3 must also be set to 1. |

| 6   | LPEN2              | R/W  | 0     | Channel 2 Low-Power-Enable (LDC2114 Only) b0: Disable Channel 2 in Low Power Mode. b1: Enable Channel 2 in Low Power Mode. EN2 must also be set to 1. |

| 5   | LPEN1              | R/W  | 0     | Channel 1 Low-Power-Enable b0: Disable Channel 1 in Low Power Mode. b1: Enable Channel 1 in Low Power Mode. EN1 must also be set to 1.                |

| 4   | LPEN0              | R/W  | 1     | Channel 0 Low-Power-Enable b0: Disable Channel 0 in Low Power Mode. b1: Enable Channel 0 in Low Power Mode. EN0 must also be set to 1.                |

| 3   | EN3 (LDC2114)      | R/W  | 1     | Channel 3 Enable (LDC2114 Only) b0: Disable Channel 3. b1: Enable Channel 3.                                                                          |

|     | RESERVED (LDC2112) | R    | 0     | Reserved. Set to b0. (LDC2112 Only)                                                                                                                   |

| 2   | EN2 (LDC2114)      | R/W  | 1     | Channel 2 Enable (LDC2114 Only) b0: Disable Channel 2. b1: Enable Channel 2.                                                                          |

|     | RESERVED (LDC2112) | R    | 0     | Reserved. Set to b0. (LDC2112 Only)                                                                                                                   |

| 1   | EN1 (LDC2114)      | R/W  | 1     | Channel 1 Enable (LDC2114 Only) b0: Disable Channel 1. b1: Enable Channel 1.                                                                          |

|     | RESERVED (LDC2112) | R    | 0     | Reserved. Set to b0. (LDC2112 Only) For LDC2112, Channel 1 is always enabled.                                                                         |

| 0   | EN0 (LDC2114)      | R/W  | 1     | Channel 0 Enable (LDC2114 Only) b0: Disable Channel 0. b1: Enable Channel 0.                                                                          |

|     | RESERVED (LDC2112) | R    | 0     | Reserved. Set to b0. (LDC2112 Only) For LDC2112, Channel 0 is always enabled.                                                                         |

# 表 14. Register NP\_SCAN\_RATE - Address 0x0D

| BIT | FIELD    | TYPE | RESET    | DESCRIPTION                                                                                                                                       |

|-----|----------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | RESERVED | R/W  | b00 0000 | Reserved. Set to b00 0000.                                                                                                                        |

| 1:0 | NPSR     | R/W  | 01       | Normal Power Mode Scan Rate Refer to Configuring Button Scan Rate for more information. b00: 80 SPS b01: 40 SPS (Default) b10: 20 SPS b11: 10 SPS |

# 表 15. Register GAIN0 – Address 0x0E

| BIT | FIELD    | TYPE | RESET    | DESCRIPTION                                                            |

|-----|----------|------|----------|------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W  | 00       | Reserved. Set to b00.                                                  |

| 5:0 | GAIN0    | R/W  | b10 1000 | Gain for Channel 0 Refer to the Gain Table for detailed configuration. |

# 表 16. Register LP\_SCAN\_RATE - Address 0x0F

| BIT | FIELD    | TYPE | RESET    | DESCRIPTION                                                                                                                                         |

|-----|----------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | RESERVED | R/W  | b00 0000 | Reserved. Set to b00 0000.                                                                                                                          |

| 1:0 | LPSR     | R/W  | 10       | Low Power Mode Scan Rate Refer to Configuring Button Scan Rate for more information. b00: 5 SPS b01: 2.5 SPS b10: 1.25 SPS (Default) b11: 0.625 SPS |

### 表 17. Register GAIN1 - Address 0x10

| BIT | FIELD    | TYPE | RESET    | DESCRIPTION                                                            |

|-----|----------|------|----------|------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W  | 00       | Reserved. Set to b00.                                                  |

| 5:0 | GAIN1    | R/W  | b10 1000 | Gain for Channel 1 Refer to the Gain Table for detailed configuration. |

### 表 18. Register INTPOL - Address 0x11

| BIT | FIELD    | TYPE | RESET   | DESCRIPTION                                                                                           |

|-----|----------|------|---------|-------------------------------------------------------------------------------------------------------|

| 7:3 | RESERVED | R/W  | b0 0000 | Reserved. Set to b0 0000.                                                                             |

| 2   | INTPOL   | R/W  | 0       | Interrupt Polarity b0: Set INTB pin polarity to active low. b1: Set INTB pin polarity to active high. |

| 1:0 | RESERVED | R/W  | 01      | Reserved. Set to b01.                                                                                 |

## 表 19. Register GAIN2 - Address 0x12

| BIT | FIELD    | TYPE | RESET    | DESCRIPTION                                                                           |

|-----|----------|------|----------|---------------------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W  | 00       | Reserved. Set to b00.                                                                 |

| 5:0 | GAIN2    | R/W  | b10 1000 | Gain for Channel 2 (LDC2114 Only) Refer to the Gain Table for detailed configuration. |

# 表 20. Register LP\_BASE\_INC - Address 0x13

| BIT | FIELD    | TYPE | RESET   | DESCRIPTION                                                                                                                                               |

|-----|----------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | RESERVED | R/W  | b0 0000 | Reserved. Set to b0 0000.                                                                                                                                 |

| 2:0 | LPBI     | R/W  | b101    | Baseline Tracking Increment in Low Power Mode Refer to <i>Tracking Baseline</i> for more information. Valid values: [b000:b111]. b101: LPBI = 5 (Default) |

# 表 21. Register GAIN3 – Address 0x14

| BIT | FIELD    | TYPE | RESET    | DESCRIPTION                                                                           |

|-----|----------|------|----------|---------------------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W  | 00       | Reserved. Set to b00.                                                                 |

| 5:0 | GAIN3    | R/W  | b10 1000 | Gain for Channel 3 (LDC2114 Only) Refer to the Gain Table for detailed configuration. |

### 表 22. Register NP\_BASE\_INC - Address 0x15

| BIT | FIELD    | TYPE | RESET   | DESCRIPTION                                                                                                                                                  |

|-----|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | RESERVED | R/W  | b0 0000 | Reserved. Set to b0 0000.                                                                                                                                    |

| 2:0 | NPBI     | R/W  | b011    | Baseline Tracking Increment in Normal Power Mode Refer to <i>Tracking Baseline</i> for more information. Valid values: [b000:b111]. b011: NPBI = 3 (Default) |

# 表 23. Register BTPAUSE\_MAXWIN - Address 0x16

| BIT | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |

|-----|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BTPAUSE3 | R/W  | 0     | Baseline Tracking Pause for Channel 3 (LDC2114 Only) Pauses baseline tracking for Channel 3 when OUT3 is asserted. Refer to <i>Tracking Baseline</i> for more information. b0: Normal baseline tracking for Channel 3 regardless of OUT3 status. (Default) b1: Pauses baseline tracking for Channel 3 when OUT3 is asserted. |

| 6   | BTPAUSE2 | R/W  | 0     | Baseline Tracking Pause for Channel 2 (LDC2114 Only) Pauses baseline tracking for Channel 2 when OUT2 is asserted. Refer to <i>Tracking Baseline</i> for more information. b0: Normal baseline tracking for Channel 2 regardless of OUT2 status. (Default) b1: Pauses baseline tracking for Channel 2 when OUT2 is asserted. |

# 表 23. Register BTPAUSE\_MAXWIN - Address 0x16 (接下页)

| BIT | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|-----|----------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | BTPAUSE1 | R/W  | 0     | Baseline Tracking Pause for Channel 1 Pauses baseline tracking for Channel 1 when OUT1 is asserted. Refer to <i>Tracking Baseline</i> for more information. b0: Normal baseline tracking for Channel 1 regardless of OUT1 status. (Default) b1: Pauses baseline tracking for Channel 1 when OUT1 is asserted. |

| 4   | BTPAUSE0 | R/W  | 0     | Baseline Tracking Pause for Channel 0 Pauses baseline tracking for Channel 0 when OUT0 is asserted. Refer to <i>Tracking Baseline</i> for more information. b0: Normal baseline tracking for Channel 0 regardless of OUT0 status. (Default) b1: Pauses baseline tracking for Channel 0 when OUT0 is asserted. |

| 3   | MAXWIN3  | R/W  | 0     | Max-Win Algorithm Setting for Channel 3 (LDC2114 Only) Refer to Resolving Simultaneous Button Presses (Max-Win) for more information. b0: Exclude Channel 3 from the max-win group. (Default) b1: Include Channel 3 in the max-win group.                                                                     |

| 2   | MAXWIN2  | R/W  | 0     | Max-Win Algorithm Setting for Channel 2 (LDC2114 Only) Refer to Resolving Simultaneous Button Presses (Max-Win) for more information. b0: Exclude Channel 2 from the max-win group. (Default) b1: Include Channel 2 in the max-win group.                                                                     |

| 1   | MAXWIN1  | R/W  | 0     | Max-Win Algorithm Setting for Channel 1 Refer to Resolving Simultaneous Button Presses (Max-Win) for more information. b0: Exclude Channel 1 from the max-win group. (Default) b1: Include Channel 1 in the max-win group.                                                                                    |

| 0   | MAXWIN0  | R/W  | 0     | Max-Win Algorithm Setting for Channel 0 Refer to Resolving Simultaneous Button Presses (Max-Win) for more information. b0: Exclude Channel 0 from the max-win group. (Default) b1: Include Channel 0 in the max-win group.                                                                                    |

# 表 24. Register LC\_DIVIDER - Address 0x17

| BIT | FIELD    | TYPE | RESET   | DESCRIPTION                                                                                                                                                                                                                                |

|-----|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | RESERVED | R/W  | b0 0000 | Reserved. Set to b0 0000.                                                                                                                                                                                                                  |

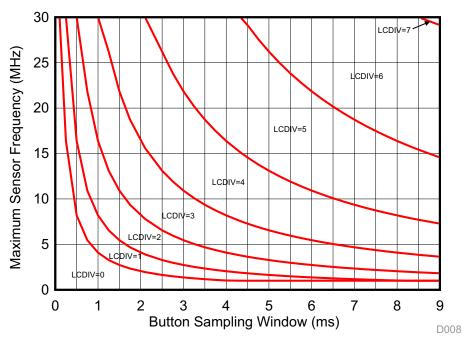

| 2:0 | LCDIV    | R/W  | b011    | LC Oscillation Frequency Divider The frequency divider sets the button sampling window in conjunction with SENCYCn. Valid values: [b000:b111]. Refer to Programming Button Sampling Window for more information. b011: LCDIV = 3 (Default) |

# 表 25. Register HYST – Address 0x18

| BIT | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                         |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | RESERVED | R/W  | b0000 | Reserved. Set to b0000.                                                                                                                                                                                                             |

| 3:0 | HYST     | R/W  | b1000 | Hysteresis Defines the hysteresis for button triggering threshold. Valid values: [b0000:b1111]. Hysteresis = HYST x 4 b1000: HYST = 8, Hysteresis = 32 (Default) Refer to Setting Button Triggering Threshold for more information. |

# 表 26. Register TWIST – Address 0x19

| BIT | FIELD     | TYPE | RESET   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

|-----|-----------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | RESERVED  | R/W  | b0 0000 | Reserved. Set to b0 0000.                                                                                                                                                                                                                                                                                                                       |

| 2:0 | ANTITWIST | R/W  | ь000    | Anti-Twist When set to 0, the anti-twist algorithm is not enabled. When greater than 0, all buttons are enabled for the anti-twist algorithm. The validation of all buttons is void if any button's DATA is negative by a threshold. Anti-twist Threshold = ANTITWIST × 4. Refer to Overcoming Case Twisting (Anti-Twist) for more information. |

# 表 27. Register COMMON\_DEFORM - Address 0x1A

| BIT | FIELD      | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                             |

|-----|------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ANTICOM3   | R/W  | 0     | Anti-Common Algorithm Setting for Channel 3 (LDC2114 Only) Refer to Eliminating Common-Mode Change (Anti-Common) for more information. b0: Exclude Channel 3 from the anti-common group. (Default) b1: Include Channel 3 in the anti-common group.      |

| 6   | ANTICOM2   | R/W  | 0     | Anti-Common Algorithm Setting for Channel 2 (LDC2114 Only) Refer to Eliminating Common-Mode Change (Anti-Common) for more information. b0: Exclude Channel 2 from the anti-common group. (Default) b1: Include Channel 2 in the anti-common group.      |

| 5   | ANTICOM1   | R/W  | 0     | Anti-Common Algorithm Setting for Channel 1 Refer to Eliminating Common-Mode Change (Anti-Common) for more information. b0: Exclude Channel 1 from the anti-common group. (Default) b1: Include Channel 1 in the anti-common group.                     |

| 4   | ANTICOM0   | R/W  | 0     | Anti-Common Algorithm Setting for Channel 0 Refer to Eliminating Common-Mode Change (Anti-Common) for more information. b0: Exclude Channel 0 from the anti-common group. (Default) b1: Include Channel 0 in the anti-common group.                     |

| 3   | ANTIDFORM3 | R/W  | 0     | Anti-Deform Algorithm Setting for Channel 3 (LDC2114 Only) Refer to <i>Mitigating Metal Deformation (Anti-Deform)</i> for more information. b0: Exclude Channel 3 from the anti-deform group. (Default) b1: Include Channel 3 in the anti-deform group. |

| 2   | ANTIDFORM2 | R/W  | 0     | Anti-Deform Algorithm Setting for Channel 2 (LDC2114 Only) Refer to <i>Mitigating Metal Deformation (Anti-Deform)</i> for more information. b0: Exclude Channel 2 from the anti-deform group. (Default) b1: Include Channel 2 in the anti-deform group. |

| 1   | ANTIDFORM1 | R/W  | 0     | Anti-Deform Algorithm Setting for Channel 1 Refer to <i>Mitigating Metal Deformation (Anti-Deform)</i> for more information. b0: Exclude Channel 1 from the anti-deform group. (Default) b1: Include Channel 1 in the anti-deform group.                |

| 0   | ANTIDFORM0 | R/W  | 0     | Anti-Deform Algorithm Setting for Channel 0 Refer to Mitigating Metal Deformation (Anti-Deform) for more information. b0: Exclude Channel 0 from the anti-deform group. (Default) b1: Include Channel 0 in the anti-deform group.                       |

# 表 28. Register OPOL\_DPOL - Address 0x1C

| BIT | FIELD | TYPE | RESET | DESCRIPTION                                                                                |

|-----|-------|------|-------|--------------------------------------------------------------------------------------------|

| 7   | OPOL3 | R/W  | 0     | Output Polarity for OUT3 Pin (LDC2114 Only)<br>b0: Active low (Default)<br>b1: Active high |

| 6   | OPOL2 | R/W  | 0     | Output Polarity for OUT2 Pin (LDC2114 Only)<br>b0: Active low (Default)<br>b1: Active high |

### 表 28. Register OPOL\_DPOL - Address 0x1C (接下页)

| BIT | FIELD | TYPE | RESET | DESCRIPTION                                                                                                                                                        |

|-----|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | OPOL1 | R/W  | 0     | Output Polarity for OUT1 Pin<br>b0: Active low (Default)<br>b1: Active high                                                                                        |

| 4   | OPOL0 | R/W  | 0     | Output Polarity for OUT0 Pin<br>b0: Active low (Default)<br>b1: Active high                                                                                        |

| 3   | DPOL3 | R/W  | 1     | Data Polarity for Channel 3 (LDC2114 Only) b0: DATA3 decreases as f <sub>SENSOR3</sub> increases. b1: DATA3 increases as f <sub>SENSOR3</sub> increases. (Default) |

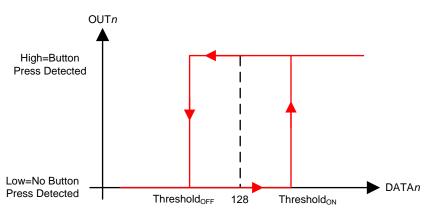

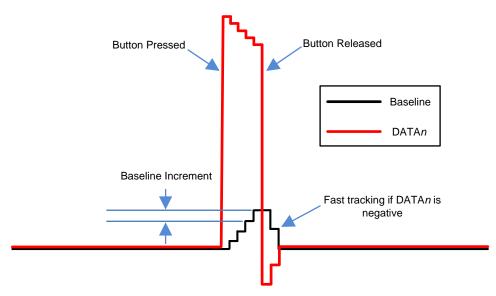

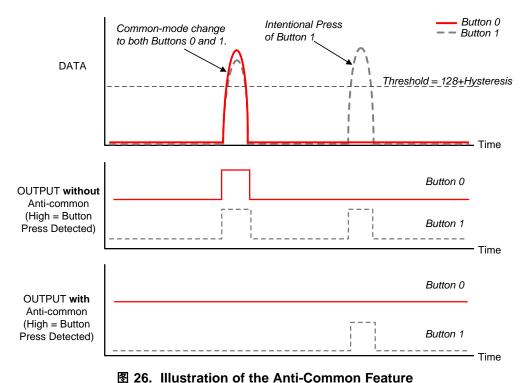

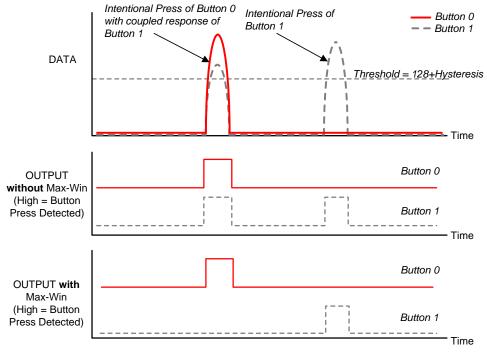

| 2   | DPOL2 | R/W  | 1     | Data Polarity for Channel 2 (LDC2114 Only) b0: DATA2 decreases as f <sub>SENSOR2</sub> increases. b1: DATA2 increases as f <sub>SENSOR2</sub> increases. (Default) |